全加器

全加器英语名称为full-adder,是用门电路实现两个二进制数相加并求出和的组合线路,称为一位全加器。一位全加器可以处理低位进位,并输出本位加法进位。多个一位全加器进行级联可以得到多位全加器。常用二进制四位全加器74LS283。

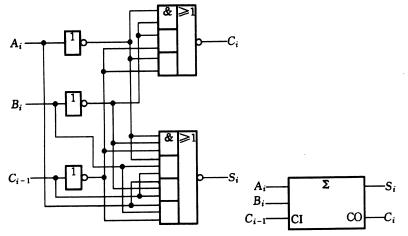

全加器是组合逻辑电路中最常见也最实用的一种,考虑低位进位的加法运算就是全加运算,实现全加运算的电路称为全加器。而其功能设计可以根据组合逻辑电路的设计方法来完成。通过逻辑门、74LS138译码器、74LS153D数据选择器来实现一位全加器的电路设计,并且实现扩展的两位全加器电路。并且Multisim是一个专门用于电路设计与仿真的工具软件。它以界面形象直观、操作方便、分析功能强大、易学易用等突出优点,迅速被推广应用。

全加器工作原理

全加器是能够计算低位进位的二进制加法电路。与半加器相比,全加器不只考虑本位计算结果是否有进位,也考虑上一位对本位的进位,可以把多个一位全加器级联后做成多位全加器.

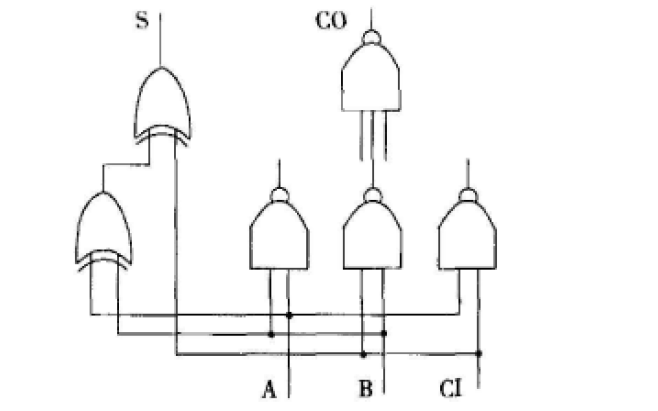

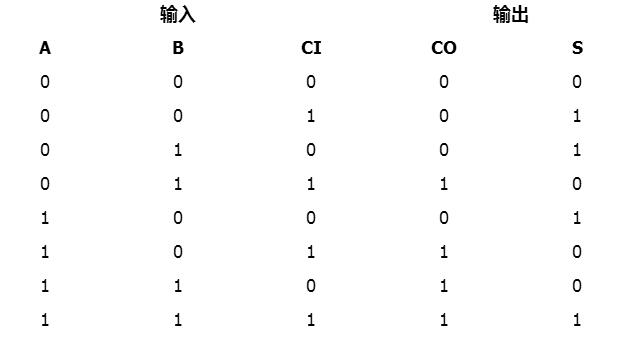

一位全加器的真值表如下图,其中Ai为被加数,Bi为加数,相邻低位来的进位数为Ci-1,输出本位和为Si。向相邻高位进位数为Ci

描述+一位全加器的表达式如下:

Si=Ai⊕Bi⊕Ci-1

第二个表达式也可用一个异或门来代替或门对其中两个输入信号进行求和:

-

逻辑电路

+关注

关注

13文章

494浏览量

42631 -

全加器

+关注

关注

10文章

62浏览量

28516

发布评论请先 登录

相关推荐

FPGA入门——1位全加器设计 精选资料分享

什么是8位全加器和8为带超前进位的全加器?

全加器译码器及显示电路实验

全加器是什么?全加器和半加器的区别?

高性能CMOS全加器设计的详细资料说明

全加器的真值表

Verilog数字系统设计——复杂组合逻辑实验2(8位全加器和8为带超前进位的全加器)

什么是全加器 全加器工作原理

什么是全加器 全加器工作原理

评论