地址不变突发是一个总线周期,在这个总线周期中完成多次操作,但是地址不变。地址不变突发的典型应用是以DMA方式读/写FIFO。主设备在时钟的某一个上升沿将CTI()置为3’b001后,下一个周期的操作必须与本周期,包括SEL_O()信号也不能改变,即在地址不变突发中的每一次操作除传输的数据可能发生变化外其他都是相同的。

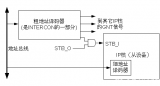

图27 Wishbone总线的地址不变突发示例

图27给出了一个地址不变突发写总线周期示例。图中主设备和从设备一共进行了4次操作。

在时钟上升沿0,主设备将地址信号ADR_O()放到总线上,将数据信号DAT_O()、TGD_O()放到总线上,将WE_O置为高表示写操作,将CTI_O()置为3’b001表示地址不变突发总线周期,将适当的SEL_O()信号置高通知从设备将数据总线上哪些信号是有效的,将CYC_O和TGC_O置高表示操作正在进行,将STB_O置高表示第一次写操作开始。

在时钟上升沿1,从设备检测到主设备的写操作,将DAT_I()采样,并置高ACK_O。

在时钟上升沿2,主设备检测到ACK_I为高,知道第一次传输顺利完成,由于数据没有准备好,于是将STB_O置低表示插入等待周期。

在等待周期,从设备知道地址不变突发写操作仍然在进行,因此一直将ACK_O置高。但是此时主设备和从设备知道没有真正的传输发生。

在时钟上升沿3,主设备已经将新的数据准备好,于是将STB_O置高表示第二次写操作开始,并更新DAT_O()。

在时钟上升沿4,从设备检测到主设备的写操作,将DAT_I()采样。同时从设备发现没有足够的空间存储数据或者由于其他原因不能及时接收新的数据,于是将ACK_O置低插入等待周期。主设备检测到ACK_I为高,于是发起第三次操作,更新DAT_O()。

在时钟上升沿5,从设备发现可以继续接收数据,于是将DAT_I()采样并将ACK_O置高。

在时钟上升沿6,主设备检测到ACK_I为高,于是发起第四次操作,更新DAT_O(),同时将CTI_O置为3’b111表示本次操作为最后一次操作。

在时钟上升沿7,从设备将DAT_I()采样,并根据CTI_O为3’b111知道本次地址不变突发写操作完成,于是将ACK_O置低。

-

时钟

+关注

关注

11文章

1750浏览量

131983 -

总线

+关注

关注

10文章

2910浏览量

88566 -

Wishbone

+关注

关注

0文章

16浏览量

10449

原文标题:【博文连载】Wishbone总线地址不变突发结束方式

文章出处:【微信号:ChinaAET,微信公众号:电子技术应用ChinaAET】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

wishbone总线

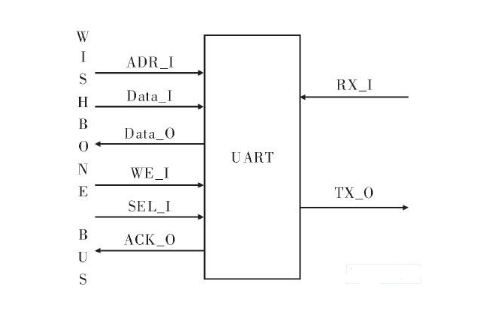

基于WISHBONE总线的FLASH闪存接口设计

基于Wishbone片上总线的IP核的互联

基于Wishbone总线的UART IP核设计

基于WISHBONE总线的FLASH闪存接口设计

基于WISHBONE总线的通用接口控制器

Wishbone总线实现UART IP核设计

基于FPGA的SDX总线与Wishbone总线接口设计

Wishbone一般总线规范的共同特点

Wishbone总线的突发结束

Wishbone总线的主要特征概括

Wishbone II交易总线:速度的另一个等级

Wishbone总线的地址不变突发示例

Wishbone总线的地址不变突发示例

评论