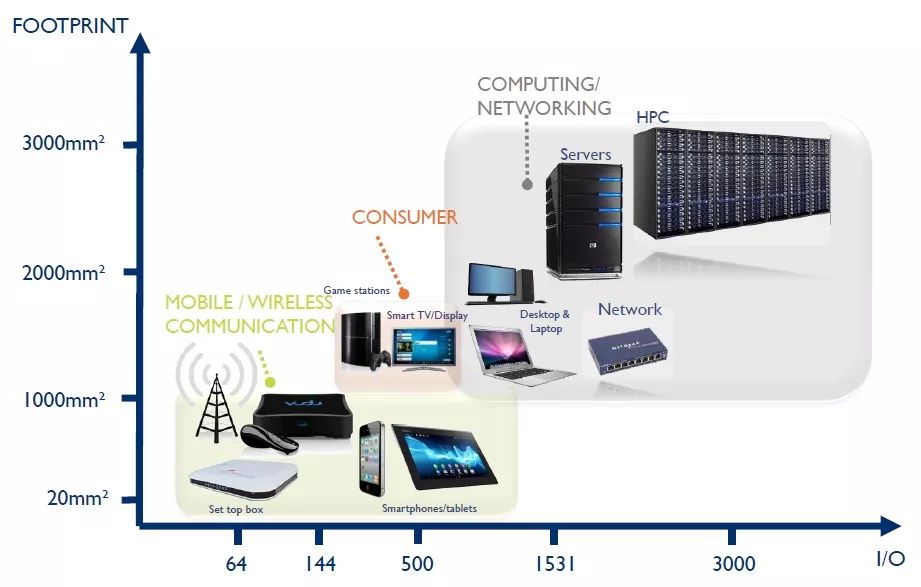

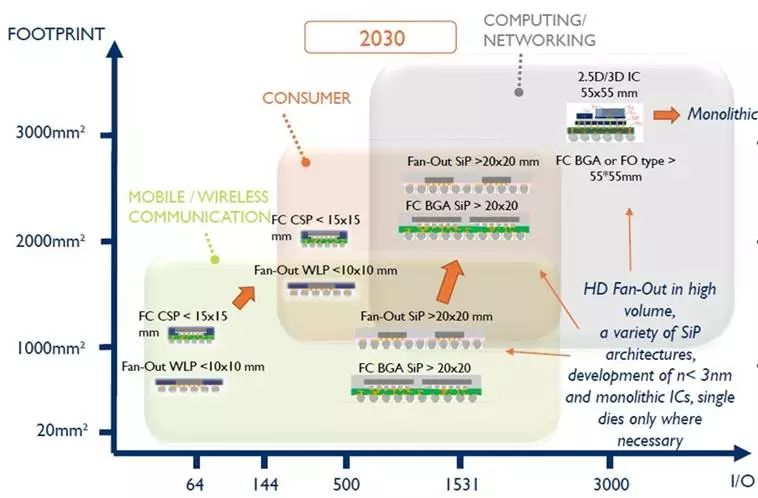

全球电子终端产品日新月异,不论是手机/无线通讯应用、消费性电子应用或是高速运算应用等,都可观察到电子产品朝向高整合度发展趋势,其中越高性能和多功能产品,除伴随之半导体芯片I/O数越高多,其所需芯片之数量也越高,整体封装芯片之面积亦越大。

图1 :电子应用产品之封装晶片之I/O数及面积关系。资料来源: Yole(2017/02)

二、终端产品推动封装技术进化

当终端产品由手持式产品、物联网消费性产品、车用电子再发展到高速运算处理器发展过程中,产品之复杂度激增情况下,能选择的芯片封装方式亦逐渐受限,这主要是因为高效能产品同时搭配先进制程芯片,同时需高整合度(细线宽线距)之封装技术,而高整合之封装技术往往伴随着低制程良率议题(Low Yield Issue),因此高效能产品能选择的封装技术甚至是能提供此製程技术的从业者亦甚是稀少,大多数封装业者亦会担心低封装良率伤害昂贵芯片所付出之代价甚大,此乃反应现今高阶2.5D中介层封装大多在晶圆厂进行的原因,因晶圆厂具备提供芯片之能力,相较专业封测厂具产业链优势。

图2 :终端产品推动封装技术进化。资料来源: Amkor(2017/09)

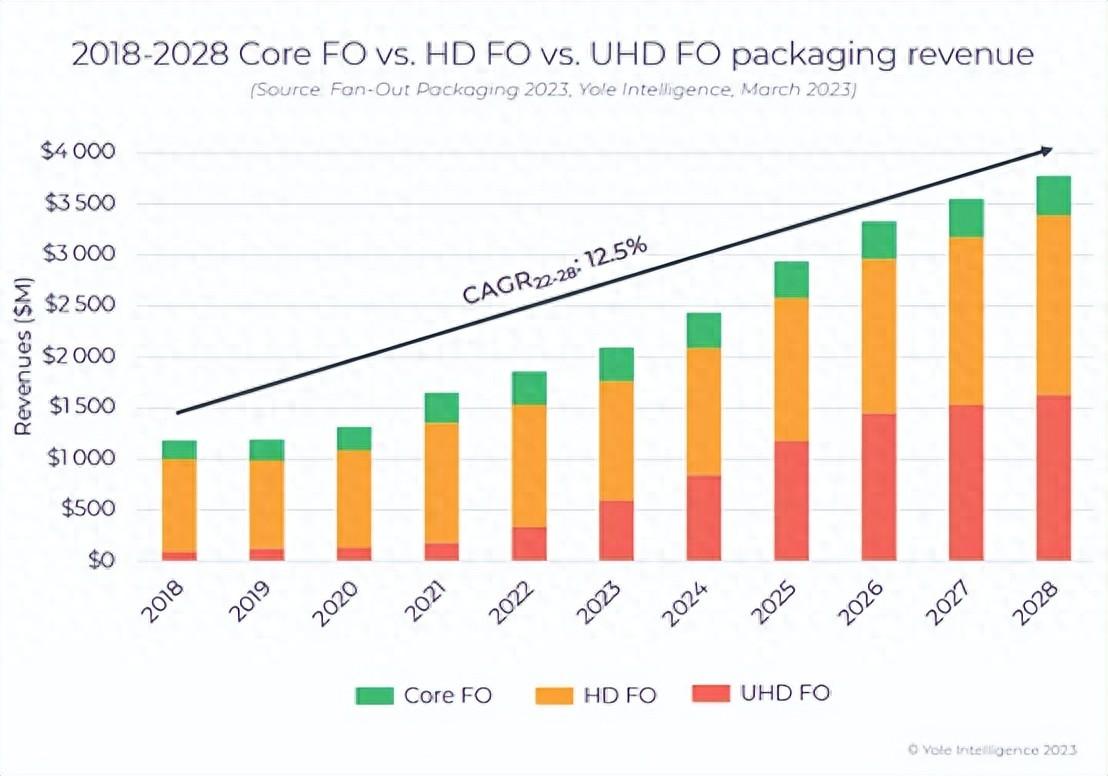

先进封装技术中,大多具备芯片整合能力,如目前不论是量或产值最大的覆晶封装技术,或是发展快速之扇出型及2.5D/3D封装技术等,其2015至2021年之产值年複合成长率分别高达49%及43%, 相对之下覆晶封装之5%年複合成长率确实逊色许多,此亦反应覆晶封装之载板不论在整合度,亦或在价格上都存在着技术瓶颈,因此对高频宽及高速运算需求之电子产品带动扇出型封装甚至更高阶之2.5D/3D封装需求兴起。

图3 :先进封装技术之产值及年複合成长率趋势。资料来源:Yole(2018/03)

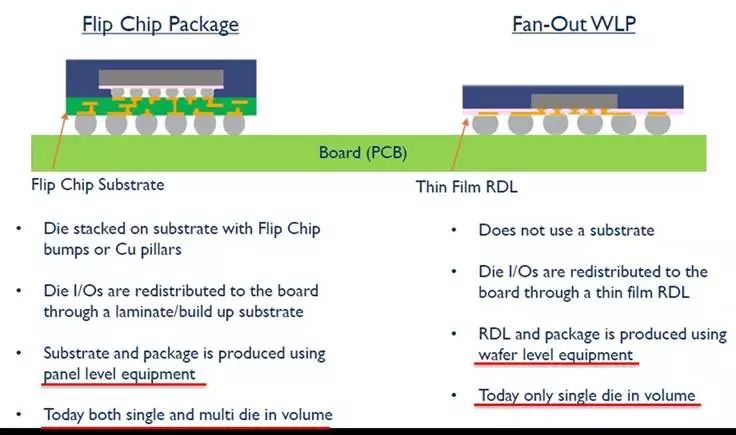

三、扇出型封装逐渐挑战覆晶封装之地位

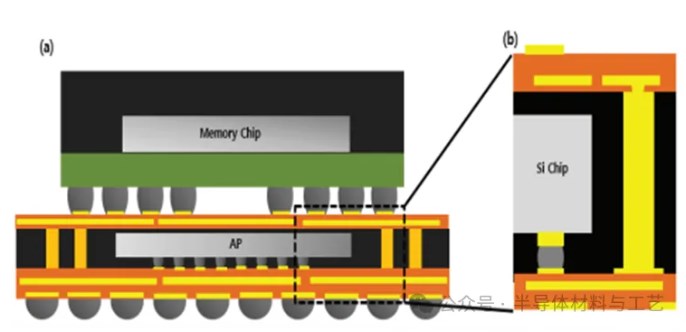

覆晶封装(Flip Chip)技术起源于1960年代,最早是IBM在大型主机上研发出之覆晶技术,而扇出型封装技术主要是源于星科金朋在2008年与意法半导体((STMicroelectronics))、英飞凌(Infineon)协议在英飞凌第一代嵌入式晶圆级球闸阵列(Wafer-Level Ball Grid Array;eWLB)技术基础上,共同合作开发新一代的eWLB技术,开发时程及设备机台落差导致扇出型封装之发展落后覆晶封装许久,而覆晶封装主要使用的设备之一是面板级载板製程,亦即其绕线层是载板製程,目前已可融合单一或多晶片以覆晶或打线方式整合在载板上,但载板之线宽(Line)线距(Space)在10/10 um以下之製程受挑战;另一方面,扇出型封装发展时程虽较覆晶封装短,但因其製程主要以晶圆级封装设备进行,其绕线层主要是薄膜(Thin film)製程,因此具发展高密度线宽线距(Line/Space<8/8 um)製程之优势,唯目前主要仍以单一晶片扇出型封装(Single die fan-out)为主,在以扇出型封装进行多晶片整合製程仍备受重佈线层(RDL)良率挑战。

图4: 覆晶封装与扇出型封装之比较。资料来源:Yole;工研院IEK (2018/03)

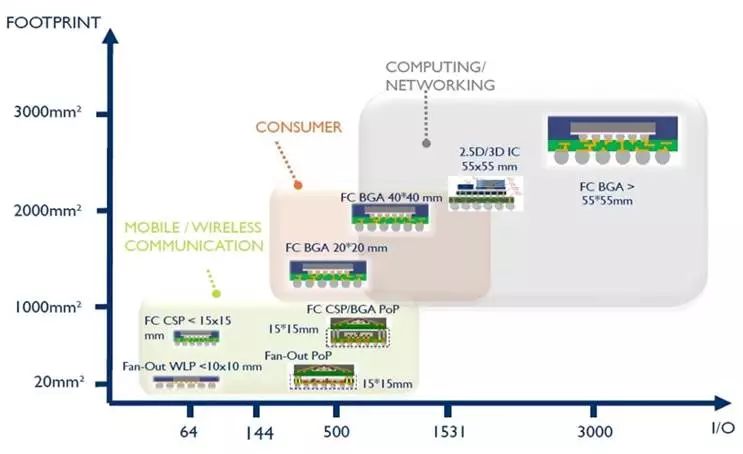

现今之覆晶封装技术较扇出型封装技术成熟,许多覆晶封装面积大于15*15mm^2以上,同时搭配上百个I/O数,而具备晶片整合之覆晶封装(FCBGA;Flip Chip Ball Grid Array)更是大于55*55mm^2以上,同时I/O数大于3000个以上,而扇出型封装目前则主要仍以单一晶片封装为主,封装面积小于15*15mm^2,同时I/O数小于1500个,主要以手机通讯等相关应用为主。

图5: 现今之覆晶仍较扇出型封装技术成熟。资料来源:Yole(2017/09)

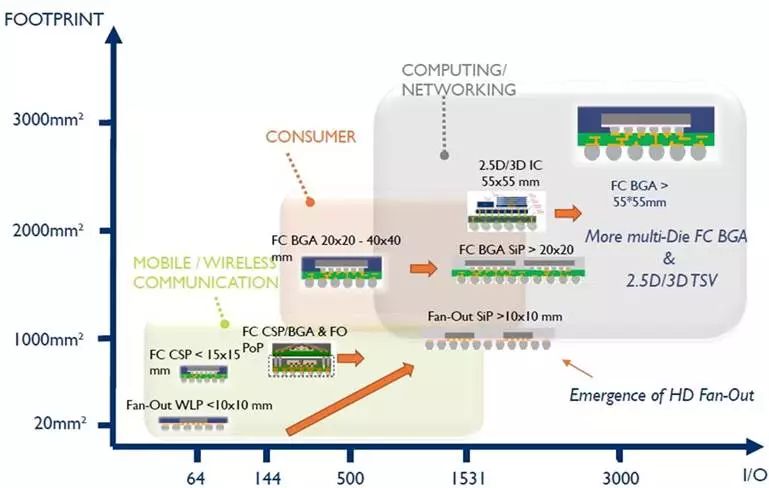

未来五年扇出型封装将逐渐走向多晶片系统级封装(Multi-die System-in-Package),同时扇出型封装亦朝向高密度(High I/O Density)-亦即细线宽线距发展,并併随朝向更大的扇出型多晶片系统级封装发展,但封装面积大于40*40 mm^2之封装将仍以覆晶封装为主,而覆晶封装之载板亦朝向细线宽线距发展。

图6 未来五年扇出型封装走向多晶片SiP封装。资料来源:Yole(2017/09)

未来十年后多晶片系统级扇出型封装SiP,已逐渐可与覆晶封装技术竞争,同时线宽/线距<10/10 um之载板亦逐渐发展成熟,而FOSiP亦逐渐发展成熟,覆晶封装与扇出型封装之竞争将加遽,在高密度扇出型封装逐渐发展成熟趋势下,将严重侵蚀单一或多晶片覆晶封装(FCCSP-Single die/FCBGA-Multi die)之市场份额,在两种技术之成本及效能接近同时,其封装大小(Package Form Factor)、产业链与客户关系将是决定要使用哪种封装的重要关键所在。

图7 未来十年扇出型封装之SiP已可与覆晶封装竞争。资料来源:Yole(2017/09)

四、产业发展趋势

在电子终端产品需求带动下,晶片同质/异质整合趋势已成市场共识,而整合度由过去从PCB及载板提升至薄膜制程或2.5D中介层等高度晶片整合方式,以产业链而言,即将面临的是载板厂与封测厂甚至晶圆厂之竞争关系,但载板厂一直以来都是封测厂之重要合作伙伴,也因此即便客户对高整合度封装有兴趣,但已俱备覆晶封装产能之封测厂是否会愿意抛弃发展已久之覆晶封装技术,改以再投入资金成本购买大量薄膜製程发展扇出型封装技术呢?亦或是以既有之覆晶产能,协同载板厂进行高密度载板之开发?很明显后者可能性较高,因前者再投资成本以封测厂为主,但因覆晶产能可能因此空缺,故未必对封测厂获利有益处,而后者之投资成本以载板厂为主,而载板厂为取得竞争优势,势必得持续朝高密度载板发展,因此,除非无覆晶封装技术及产能包伏之封测厂较有可能积极发展扇出型封测技术外,具覆晶产能之封测厂则对扇出型封装之再投资意愿相对较低。

-

封装

+关注

关注

126文章

7789浏览量

142734 -

晶片

+关注

关注

1文章

401浏览量

31444

原文标题:【技术专栏】电子产品正在颠覆先进封装的竞争格局!

文章出处:【微信号:Anxin-360ic,微信公众号:芯师爷】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

电子产品结构与导热材料解决方案

扇出型 (Fan-Out)封装市场规模到2028 年将达到38 亿美元

测电子产品辐射的仪器叫什么

扇入型和扇出型晶圆级封装的区别

趋势报告揭示循环型电子产品的未来

电子产品环境模拟试验详解

什么是SMD7050晶振?主要应用在哪些电子产品上面?

CCC认证费用分析:比较不同类型电子产品的认证成本

电子产品覆晶封装与扇出型封装之间的竞争分析

电子产品覆晶封装与扇出型封装之间的竞争分析

评论