一个8比特从设备

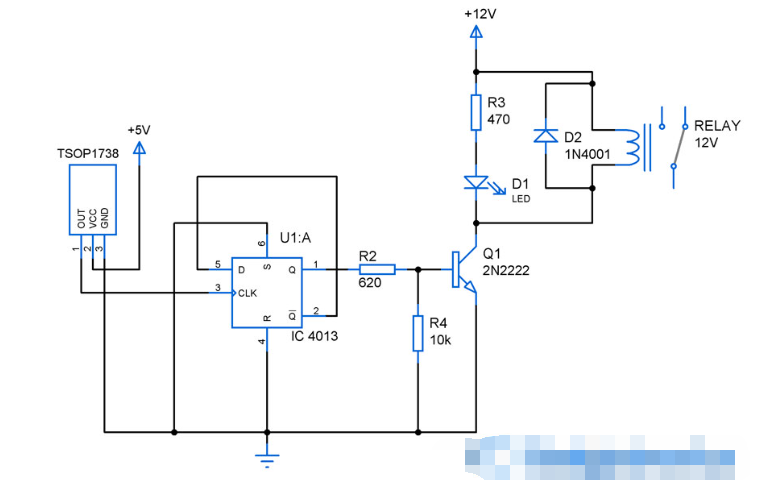

前文曾经指出,Wishbone总线规范是"轻量级(Lightweight)"规范,它实现起来非常简单紧凑,接口需要的互联逻辑非常少。这里给出一个Wishbone从设备的一个例子,如图21所示。该从设备由一个与门和8个D触发器构成。在写周期,当STB_I和WE_I同时有效,数据DAT_I[7:0]在时钟CLK_I的上升沿被写到触发器中。

图21 一个简单的Wishbone从设备

该从设备的RTL代码如下:

moduleslave8bit( inputCLK_I,//这里使用了Verilog2001语法 inputRST_I, input[7:0]DAT_I, inputSTB_I,inputWE_I, outputreg[7:0]DAT_O,outputACK_O); always@(posedgeCLK_IorposedgeRST_I) begin if(RST_I) begin DAT_O<=8'h00; end else if(STB_I&WE_I) begin DAT_O<=DAT_I; end end assign ACK_O=STB_I; endmodule

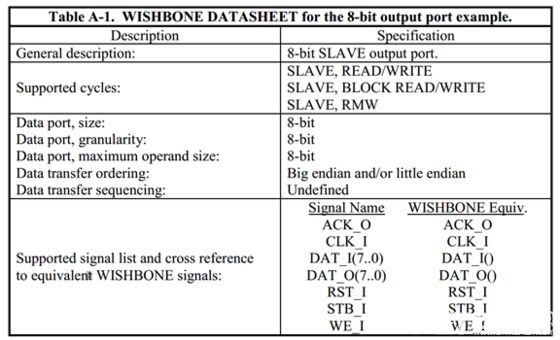

该从设备的Wishbone文档如表5。

表5从设备的Wishbone文档

一个32比特RTL级随机数生成器从设备

下面我们举一个实用一点的例子,一个随机数生成器。随机数生成理论和随机数生成器随机数生成理论和随机数生成器模块的RTL代码见附录2。该模块端口定义如下:

module rng(clk,reset,loadseed_i,seed_i,number_o);

number_o为随机数输出,当loadseed_I有效时,种子seed_I被送入number_o成为随机数的第一个值。

我们的目的是将其包装成WISHBONE兼容的从模块,其Verilog RTL代码如下:

moduleRng_wbc( inputCLK_I, inputRST_I, input[31:0]DAT_I, inputSTB_I,inputWE_I, input[3:0]SEL_I, output[31:0]DAT_O,outputACK_O); assignACK_O=STB_I; wireloadseed=WE_I&STB_I&(|SEL_I); wire[31:0]seed; assignseed[7:0]=SEL_I[0]?DAT_I[7:0]:8'h00; assignseed[15:8]=SEL_I[1]?DAT_I[15:8]:8'h00; assignseed[23:16]=SEL_I[2]?DAT_I[23:16]:8'h00; assignseed[31:24]=SEL_I[3]?DAT_I[31:24]:8'h00; wire[31:0]rand_number; assignDAT_O[7:0]=SEL_I[0]?rand_number[7:0]:8'h00; assignDAT_O[15:8]=SEL_I[1]?rand_number[15:8]:8'h00; assignDAT_O[23:16]=SEL_I[2]?rand_number[23:16]:8'h00; assignDAT_O[31:24]=SEL_I[3]?rand_number[31:24]:8'h00; //随机数生成器的莉化 rngunit_rng(.clk(CLK_I),.reset(RST_I), .loadseed_i(loadseed),.seed_i(seed), .number_o(rand_number)); endmodule

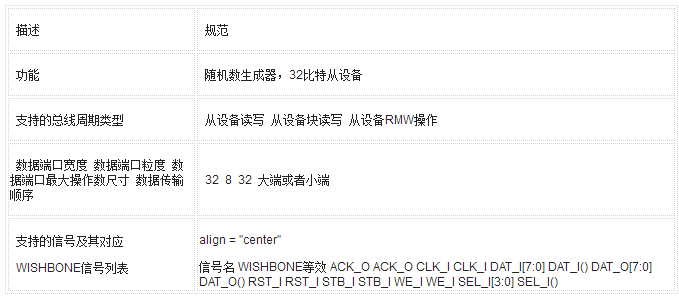

该从设备的Wishbone文档如表6。

表6从设备的Wishbone文档

-

触发器

+关注

关注

14文章

2000浏览量

61148 -

Wishbone

+关注

关注

0文章

16浏览量

10429

原文标题:【博文连载】Wishbone总线从设备接口示例

文章出处:【微信号:ChinaAET,微信公众号:电子技术应用ChinaAET】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

wishbone总线

基于WISHBONE总线的FLASH闪存接口设计

基于Wishbone总线的UART IP核设计

基于WISHBONE总线的FLASH闪存接口设计

设计复用的RTL指导原则

HLS系列 – High Level Synthesis(HLS) 从一个最简单的fir滤波器开始2

用Elaborated Design优化RTL的代码

一个简单的Wishbone从设备的RTL代码

一个简单的Wishbone从设备的RTL代码

评论