- Load:0 second

- Duration:0 second

- Size:0x0

- Volume:0%

- Fps:60fps

- Sudio decoded:0 Byte

- Video decoded:0 Byte

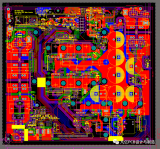

PCB设计中的要点:

1、选择PCB板材

选择PCB板材必须在满足设计需求和可量产性及成本中间取得平衡点。设计需求包含电气和机构这两部分。通常在设计非常高速的PCB板子(大于GHz的频率)时这材质问题会比较重要。 例如,现在常用的FR-4材质,在几个GHz的频率时的介质损(dielectric loss)会对信号衰减 有很大的影响,可能就不合用。就电气而言,要注意介电常数(dielectric constant)和介 质损在所设计的频率是否合用。

2、避免高频干扰

避免高频干扰的基本思路是尽量降低高频信号电磁场的干扰,也就是所谓的串扰 (Crosstalk)。可用拉大高速信号和模拟信号之间的距离,或加ground guard/shunt traces 在模拟信号旁边,还要注意数字地对模拟地的噪声干扰。

3、解决信号的完整性问题

信号完整性基本上是阻抗匹配的问题。而影响阻抗匹配的因素有信号源的架构和输出阻抗 (output impedance),走线的特性阻抗,负载端的特性,走线的拓朴(topology)架构等。解决的方式是靠端接(termination)与调整走线的拓朴。

4、实现差分布线方式

差分对的布线有两点要注意,一是两条线的长度要尽量一样长,另一是两线的间距(此间距 由差分阻抗决定)要一直保持不变,也就是要保持平行。平行的方式有两种,一为两条线走 在同一走线层(side-by-side),一为两条线走在上下相邻两层(over-under)。一般以前者 side-by-side实现的方式较多。

5、在只有一个输出端的时钟信号线情况下,实现差分布线

要用差分布线一定是信号源和接收端也都是差分信号才有意义。所以对只有一个输出端的时 钟信号是无法使用差分布线的。

6、接收端差分线对间的匹配电阻

接收端差分线对间的匹配电阻通常会加, 其值应等于差分阻抗的值。这样信号品质会好些。

7、差分对的布线要靠近且平行

对差分对的布线方式应该要适当的靠近且平行。所谓适当的靠近是因为这间距会影响到差分 阻抗(differential impedance)的值, 此值是设计差分对的重要参数。需要平行也是因为要保持差分阻抗的一致性。若两线忽远忽近, 差分阻抗就会不一致, 就会影响信号完整性 (signal integrity)及时间延迟(timing delay)。

8、处理实际布线中的一些理论冲突的问题

a. 基本上,将模/数地分割隔离是对的。要注意的是信号走线尽量不要跨过有分割的地方(moat), 还有不要让电源和信号的回流电流路径(returning current path)变太大。

b. 晶振是模拟的正反馈振荡电路,要有稳定的振荡信号,必须满足loop gain与phase的规范, 而这模拟信号的振荡规范很容易受到干扰, 即使加ground guard traces可能也无法完全隔离干扰。 而且离的太远, 地平面上的噪声也会影响正反馈振荡电路。所以,一定要将 晶振和芯片的距离进可能靠近。

c. 确实高速布线与EMI的要求有很多冲突。 但基本原则是因EMI所加的电阻电容或ferrite bead,不能造成信号的一些电气特性不符合规范。所以,最好先用安排走线和PCB叠层的技 巧来解决或减少EMI的问题, 如高速信号走内层。最后才用电阻电容或ferrite bead的方式,以降低对信号的伤害。

9、解决高速信号的手工布线和自动布线之间的矛盾

现在较强的布线软件的自动布线器大部分都有设定约束条件来控制绕线方式及过孔数目。 各家EDA公司的绕线引擎能力和约束条件的设定项目有时相差甚远。例如,是否有足够的约束条件控制蛇行线(serpentine)蜿蜒的方式,能否控制差分对的走线间距等。这会影响到 自动布线出来的走线方式是否能符合设计者的想法。另外,手动调整布线的难易也与绕线 引擎的能力有绝对的关系。例如,走线的推挤能力,过孔的推挤能力,甚至走线对敷铜的推挤能力等等。所以,选择一个绕线引擎能力强的布线器,才是解决之道。

-

电源

+关注

关注

185文章

18031浏览量

253304 -

pcb

+关注

关注

4337文章

23279浏览量

402879

发布评论请先 登录

相关推荐

pcb设计时注意事项

HDMI模块的PCB设计

pcb设计中布局的要点是什么

PCB设计与PCB制板的紧密关系

PCB电路板设计与制作的步骤和要点

电路仿真和PCB设计软件

PCB设计的EMC有哪些注意事项

功率PCB设计要点详细整理

PCB设计中有哪些需注意的要点?

PCB设计中有哪些需注意的要点?

评论