信号完整性仿真大多针对由芯片IO、传输线以及可能存在的接插件和分立元件所构成的信号网络系统,为了实现精确的仿真,仿真模型的精确性是首先需要保证的。一般情况下,Allegro PCB SI会执行传输线和分立元件的建模,而芯片IO和连接器的模型通常会由原厂提供。当前业内常见的芯片IO模型有两种格式,IBIS模型和HSPICE模型;常见的连接器模型也是两种,SPICE(HSPICE)模型和S参数模型。Allegro PCB SI支持包括上述四种模型在内业界流行的仿真模型,但一般都需要转化为Cadence自己的DML(Device Modeling Library)后才能使用。

Allegro PCB SI在仿真时需要将仿真模型都转变成DML模型格式这一做法,区别于大多数EDA软件,这种做法可以说是有利有弊有。弊,很明显,就是多一个额外的步骤,虽然这一步骤非常简便;利,则是有利于仿真库的管理,做到仿真库和原始模型文件的隔离,并且在文件格式转换的同时也执行了模型的校验。在大多数情况下,外部模型格式到Cadence DML模型格式的转换还是非常方便的,只需要用Cadence SPB系列工具包中的Model Integrity软件打开模型文件,然后点击转换到DML即可。

在本案例中,我们之前已经从Micron下载到寄存器和内存芯片的IBIS模型,可以有两种方法处理:

其一,在Model Integrity界面下或Allegro PCB SI界面下将IBIS模型转换成DML格式,供之后的仿真调用;

其二,从Cadence SPB 16.5版本开始,Allegro PCB SI名义上也直接支持IBIS模型,所以可以保留现有的两个IBIS文件不做转换,然后在之后的仿真中直接调用。之所以说是“名义上”,因为事实上Allegro PCB SI还是执行了转换,只是这个转换的过程在分配模型的同时一起执行了,没有摆在明面上。

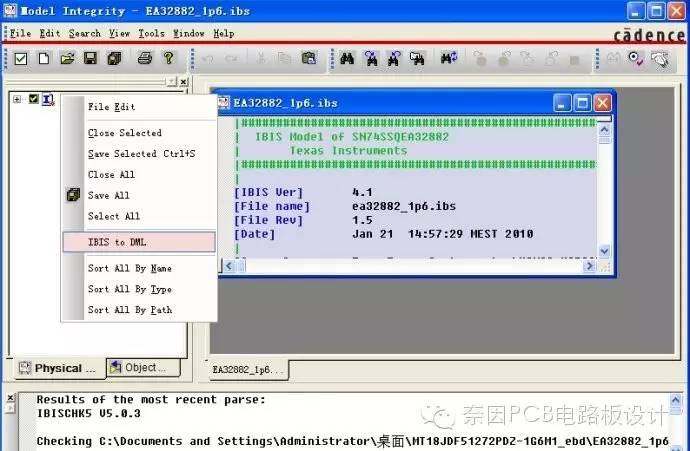

如何使用Model Integrity转换IBIS模型。

1.在开始菜单找到Model Integrity,点击即打开Model Integrity窗口。

2.点击File->Open打开寄存器的IBIS模型文件EA32882_1p6.ibs;

3.右键点击浏览栏中的EA32882_1p6,选择IBIS to DML;

4.转换得到的同名DML模型会显示在Model Integrity窗口中,同名文件也出现在IBIS文件同一目录下。5.重复上述步骤将内存芯片的IBIS模型v79d.ibs也转换成DML格式。

怎么样有效建立SI模型? 在建SI模型时,由于有时候电容和电阻用的是同一个封装,比如0603 、0402,soic8等,有时候在同一个封装下建了同一个模型(也许是由于我自己的操作不对吧 )如果不一个一个地建, 怎么样才能有效地根据不同的阻值、不同的用途批量建立模型呢?

=================================================

解答:device.dml是库文件,RN47K包含在库文件里。 电阻和电容一般情况下不要用同一个封装,实在要用也关系不大,在赋模型的时候按照器件标号去赋就可以了。另外模型不需要批量建,同种器件只需建一个即可。

-

pcb

+关注

关注

4322文章

23124浏览量

398510 -

PCB设计

+关注

关注

394文章

4691浏览量

85853 -

allegro

+关注

关注

42文章

658浏览量

145272 -

IBIS

+关注

关注

1文章

53浏览量

19908 -

可制造性设计

+关注

关注

10文章

2065浏览量

15625 -

华秋DFM

+关注

关注

20文章

3494浏览量

4586

原文标题:Allegro怎么样有效建立SI模型

文章出处:【微信号:Line_pcblayout,微信公众号:Line_pcblayout】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

IBIS 模型

Model Integrity使用求助

PCB SI/PI中添加IBIS模型后,sigxplorer中元件模型显示unknown

我需要用于SPC572L60F2微控制器的IBIS模型

怎么使用IBIS模型用于Spartan-3A

生成IBIS模型错误

请问哪里可以找到芯片的IBIS模型?

哪里可以找到IBIS模型?

【转载】Allegro SI 高速信号完整性仿真连载之二(附详细流程)

求助,请发送在Hyperlynx软件中进行SI分析所需的IBIS模型

Allegro如何有效建立SI模型

Allegro怎么样有效建立SI模型? 如何使用Model Integrity转换IBIS模型

Allegro怎么样有效建立SI模型? 如何使用Model Integrity转换IBIS模型

评论