可编程逻辑具有传统分立 IC 无法提供的灵活性。 借助现成的开发工具,可轻松使用现场可编程门阵列和复杂可编程逻辑器件创建应用特定型功能。 按钮开关输入消抖便是此类功能的一个例子。

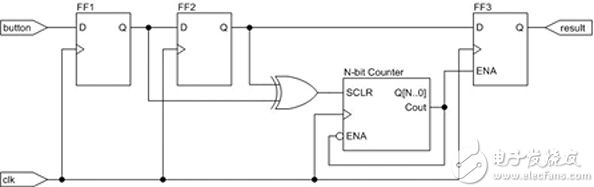

下图 1 说明了一个有效的消抖逻辑电路。 此电路持续将按钮的逻辑电平记录到 FF1 然后记录到 FF2,使得 FF1 和 FF2 始终存储此按钮的最后两个逻辑电平。 当这两个值在指定的时间内保持相等时,启用 FF3,并通过它将稳定值记录到结果输出。

图 1: 逻辑电路消抖。

XOR 门和 N 位计数器完成定时。 如果按钮的电平发生变化,则 FF1 和 FF2 的值在一个时钟周期内不同,从而通过 XOR 门清零 N 位计数器。 如果按钮的电平不变(即,如果 FF1 和 FF2 处于相同的逻辑电平),则 XOR 门会释放计数器的同步清零功能,并且计数器开始计数。 计数器持续按此方式递增,直至其 (1) 达到指定的时间并启用输出寄存器,或 (2) 因按钮的逻辑电平尚未稳定而被 XOR 门中断并清零。

计数器的大小决定了验证按钮稳定性所需的时间。 当计数器递增至其进位输出位被断言时,将会自行停止递增并启用输出寄存器 FF3。 电流将保持此状态,直至另一个按钮值被记录到 FF1,从而通过 XOR 门清零计数器。

-

计数器

+关注

关注

32文章

2256浏览量

94579 -

可编程逻辑

+关注

关注

7文章

515浏览量

44087

发布评论请先 登录

相关推荐

如何使用可编程逻辑为按钮输入消抖:一个有效的消抖逻辑电路

组合逻辑电路和时序逻辑电路比较_组合逻辑电路和时序逻辑电路有什么区别

一个有效的消抖逻辑电路应用设计

一个有效的消抖逻辑电路应用设计

评论