当前最流行的硬件设计语言有两种,即 VHDL 与 Verilog HDL,两者各有优劣,也各有相当多的拥护者。VHDL 语言由美国军方所推出,最早通过国际电机工程师学会(IEEE)的标准,在北美及欧洲应用非常普遍。而 Verilog HDL 语言则由 Gateway 公司提出,这家公司辗转被Cadence所购并,并得到Synopsys的支持。在得到这两大 EDA 公司的支持后,也随后通过了 IEEE 标准,在美国、日本及中国***地区使用非常普遍。

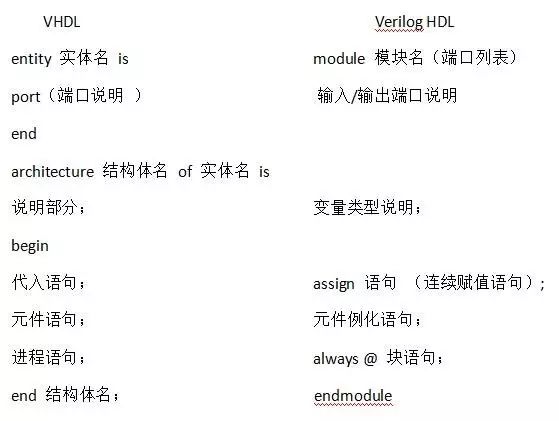

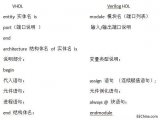

我们把这两种语言具体比较下:

1.整体结构

点评:

两者结构基本相似,并行语句的种类也类似;

VHDL语言需要进行大量说明,程序通常比较长;

Verilog HDL通常不进行说明,或只进行非常简短的说明,程序比较简短。

2.数据对象及类型

VHDL

常量 信号 变量 9种预定义类型 各类用户定义类型

可描述各类不同的量

必须进行类型说明

运算时必须考虑类型的一致性和适用性

Verilog HDL

常量: 数量,参量

类型种类少

运算时所受的约束少

3.运算符号

运算主要分为3类 : 算术运算 逻辑运算 关系运算

算术运算

VHDL中有10种 但很多都不能进行综合,只能用于行为描述

Verilog HDL中只有能够综合的5种

逻辑运算

VHDL中 有常用的6种,均用字符形式表达

Verilog HDL中有3类共14种,

分为一般逻辑运算,位逻辑运算,缩减逻辑运算

关系运算

VHDL中有6种

Verilog HDL中有2类共8种,对比增加了全等和不全等(用于对不定态比较)。

除了以上3类运算外,VHDL中还有连接运算,Verilog HDL中还有连接运算、移位运算和条件运算。

点评:

VHDL的运算划分比较抽象,适应面较广

Verilog HDL的运算划分比较具体,对逻辑代数反映更细致一些。

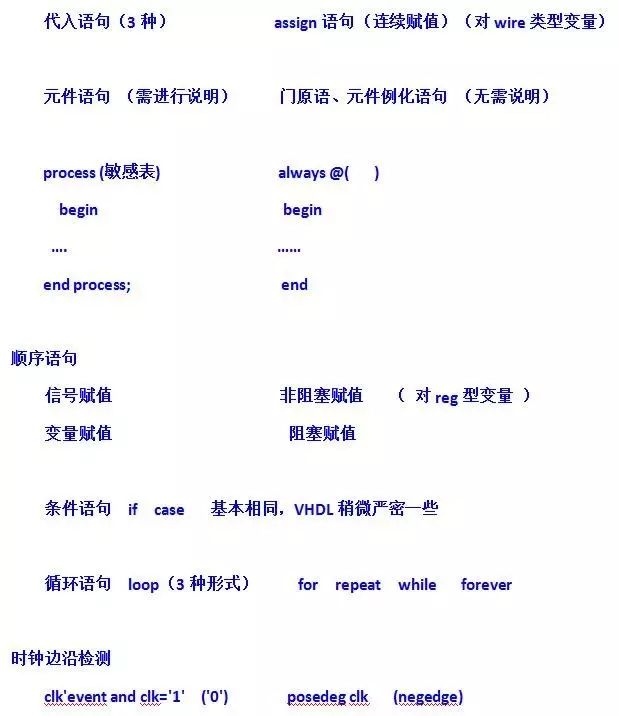

4.语句

两种语言的语句都分为并行语句和顺序语句,并行语句在主程序中使用,顺序语句只能在子结构中使用;

并行语句都分为3种形式:

5.子结构

function function 'define

procedure task

6.附加结构

library

package 'include

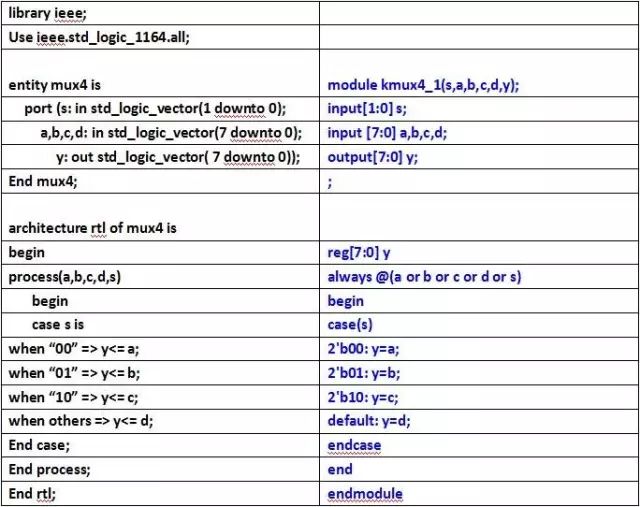

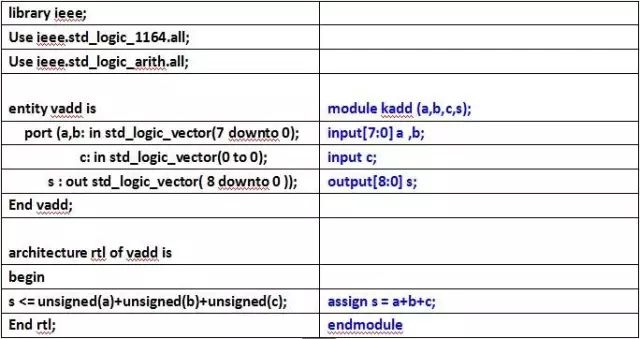

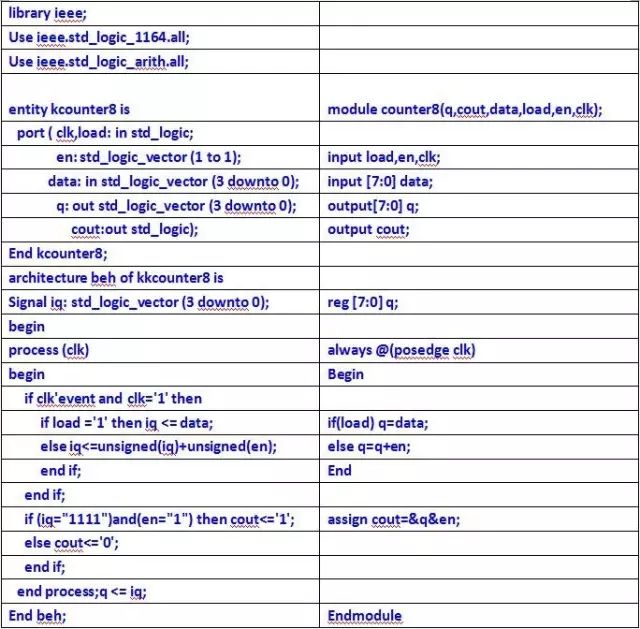

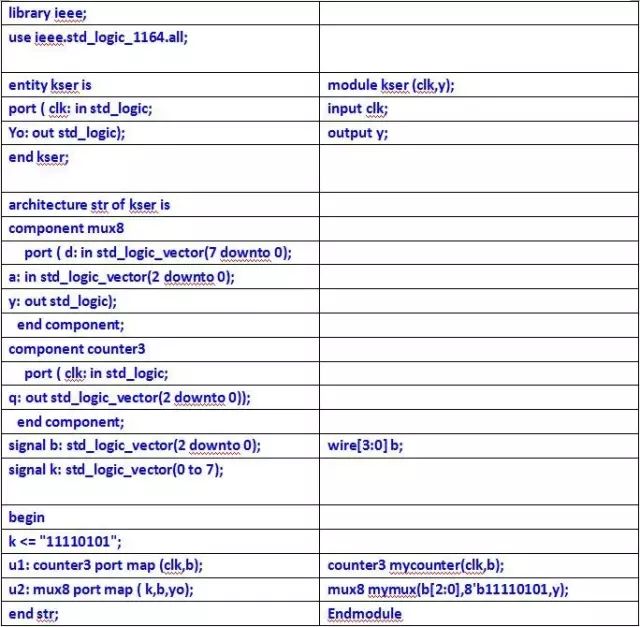

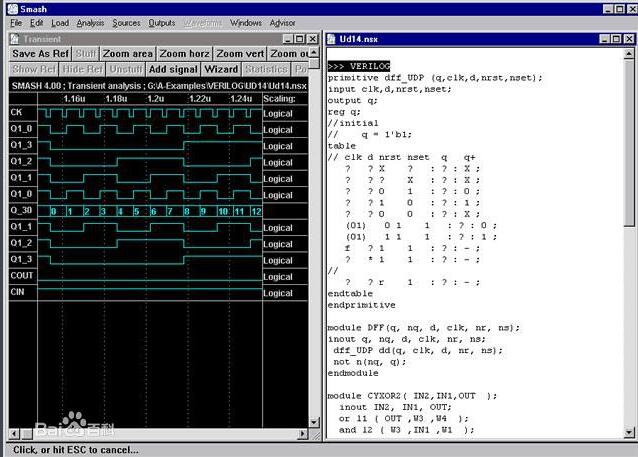

7.典型程序对比:

8位4选1MUX

8位加法器

8位二进制加法计数器

序列信号发生器:kser

预先设计模块:8选1MUX:MUX8控制输入a[2..0] 数据输入d[7..0] 数据输出y

3位2进制加法计数器:COUNTER3时钟输入 clk状态输出q[2..0]

设计要求:按照时钟节拍,由y端口循环顺序输出“11110101”序列信号

初学者往往头疼于选哪种入门合适。其实,随便选一种即可。最关键的是要养成良好的代码编写风格,在满足功能和性能目标的前提下,增强代码的可读性、可移植性。

良好代码编写风格的通则概括如下:

(1) 对所有的信号名、变量名和端口名都用小写,这样做是为了和业界的习惯保持一致;对常量名和用户定义的类型用大写;

(2) 使用有意义的信号名、端口名、函数名和参数名;

(3) 信号名长度不要太长;

(4) 对于时钟信号使用clk 作为信号名,如果设计中存在多个时钟,使用clk 作为时钟信号的前缀;

(5) 对来自同一驱动源的信号在不同的子模块中采用相同的名字,这要求在芯片总体设计时就定义好顶层子模块间连线的名字,端口和连接端口的信号尽可能采用相同的名字;

(6) 对于低电平有效的信号,应该以一个下划线跟一个小写字母b 或n 表示。注意在同一个设计中要使用同一个小写字母表示低电平有效;

(7) 对于复位信号使用rst 作为信号名,如果复位信号是低电平有效,建议使用rst_n;

(8) 当描述多比特总线时,使用一致的定义顺序,对于verilog 建议采用bus_signal[x:0]的表示;

(9) 尽量遵循业界已经习惯的一些约定。如*_r 表示寄存器输出,*_a 表示异步信号,*_pn 表示多周期路径第n 个周期使用的信号,*_nxt 表示锁存前的信号,*_z 表示三态信号等;

(10)在源文件、批处理文件的开始应该包含一个文件头、文件头一般包含的内容如下例所示:文件名,作者,模块的实现功能概述和关键特性描述,文件创建和修改的记录,包括修改时间,修改的内容等;

(11)使用适当的注释来解释所有的always 进程、函数、端口定义、信号含义、变量含义或信号组、变量组的意义等。注释应该放在它所注释的代码附近,要求简明扼要,只要足够说明设计意图即可,避免过于复杂;

(12)每一行语句独立成行。尽管VHDL 和Verilog 都允许一行可以写多个语句,当时每个语句独立成行可以增加可读性和可维护性。同时保持每行小于或等于72 个字符,这样做都是为了提高代码得可读性;

(13)建议采用缩进提高续行和嵌套语句得可读性。缩进一般采用两个空格,如西安交通大学SOC 设计中心2 如果空格太多则在深层嵌套时限制行长。同时缩进避免使用TAB 键,这样可以避免不同机器TAB 键得设置不同限制代码得可移植能力;

(14)在RTL 源码的设计中任何元素包括端口、信号、变量、函数、任务、模块等的命名都不能取Verilog 和VHDL 语言的关键字;

(15)在进行模块的端口申明时,每行只申明一个端口,并建议采用以下顺序:

输入信号的clk、rst、enables other control signals、data and address signals。然后再申明输出信号的clk、rst、enalbes other control signals、data signals;

(16)在例化模块时,使用名字相关的显式映射而不要采用位置相关的映射,这样可以提高代码的可读性和方便debug 连线错误;

(17)如果同一段代码需要重复多次,尽可能使用函数,如果有可能,可以将函数通用化,以使得它可以复用。注意,内部函数的定义一般要添加注释,这样可以提高代码的可读性;

(18)尽可能使用循环语句和寄存器组来提高源代码的可读性,这样可以有效地减少代码行数;

(19)对一些重要的always 语句块定义一个有意义的标号,这样有助于调试。注意标号名不要与信号名、变量名重复;

(20)代码编写时的数据类型只使用IEEE 定义的标准类型,在VHDL 语言中,设计者可以定义新的类型和子类型,但是所有这些都必须基于IEEE 的标准;

(21)在设计中不要直接使用数字,作为例外,可以使用0 和1。建议采用参数定义代替直接的数字。同时,在定义常量时,如果一个常量依赖于另一个常量,建议在定义该常量时用表达式表示出这种关系;

(22)不要在源代码中使用嵌入式的dc_shell 综合命令。这是因为其他的综合工具并不认得这些隐含命令,从而导致错误的或较差的综合结果。即使使用Design Compiler,当综合策略改变时,嵌入式的综合命令也不如放到批处理综合文件中易于维护。这个规则有一个例外的综合命令,即编译开关的打开和关闭可以嵌入到代码中;

(23)在设计中避免实例化具体的门级电路。门级电路可读性差,且难于理解和维护,如果使用特定工艺的门电路,设计将变得不可移植。如果必须实例化门电路,我们建议采用独立于工艺库的门电路,如SYNOPSYS 公司提供的GTECH 库包含了高质量的常用的门级电路;

(24)避免冗长的逻辑和子表达式;

(25)避免采用内部三态电路,建议用多路选择电路代替内部三态电路。

-

vhdl

+关注

关注

30文章

817浏览量

128125 -

硬件设计

+关注

关注

18文章

396浏览量

44565

原文标题:VHDL精密,Verilog简洁,但要写好任何一种都要遵守这25条...

文章出处:【微信号:mcu168,微信公众号:硬件攻城狮】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

数字IC设计入门(6)初识verilog 精选资料推荐

讨论Verilog语言的综合问题

Verilog HDL与VHDL及FPGA的比较分析

VHDL,Verilog,System verilog比较

vhdl和verilog的区别_vhdl和verilog哪个好?

关于VHDL和Verilog两种语言的异同分析和具体的比较

Verilog HDL和VHDL的区别

VHDL与Verilog硬件描述语言如何用TestBench来进行仿真

数字IC设计入门(6)初识verilog

VHDL与Verilog硬件描述语言TestBench的编写

最流行的硬件设计语言,VHDL和Verilog比较

最流行的硬件设计语言,VHDL和Verilog比较

评论