随着物联网(IoT)的快速发展,未来将会存在海量的数据。“大数据”时代,对数据的处理提出更高的需求。高性能处理器及集群能完成数据的实时处理。而在处理器与外设或处理器之间传输的大量数据,对接口(Interface)技术也提出了更高的要求。就像一个人虽然有着聪明的头脑,但神经却比较“长”,就看起来就会很“呆笨”。目前主流并行接口技术就面临着这样的局面,越来越成为了瓶颈。

回顾接口技术发展历史,其实数据的传输最开始是低速的串行接口(Serial Interface,简称串口),为了提高数据的总带宽,首先想到的是增加数据传输位宽,再进一步提升速率。也就是并行接口(Parallel Interface,简称并口)的方式,并逐渐取代传统低速串口成为主流。但随着并口的发展,其限制也也越来越明显。而高速串行(High Speed Serial,HSS)接口技术具有的优势使其有取代目前并口的趋势。表现为接口总带宽的显著提升。其历史就像图1所示,从山间小道升级为乡村公路,再到高速公路(网),能够提供更高的通行量。

图1

目前并口发展遇到的限制主要为,一方面芯片封装面临着IO数量紧张的问题,另一方面是,并口的数据速率提升过程中面临的串扰(Crosstalk)和噪声(SSN)问题,使得数据的同步变得很困难。这个问题可以理解为,就像阅兵方阵,正步走起来英姿飒爽,这都需要很长时间的训练。如果要求齐步跑起来,也要横竖成线(数据对齐同步),可真是难倒人啦。

图2

串口和并口的交替发展演进,真可谓“三十年河东,三十年河西”,技术并没有对错,“时势造英雄”。

串口的典型代表就是在消费电子和其他各领域中普遍使用的通用串行总线(Universal Serial Bus,USB);并口也有很多,比如DDR DRAM内存接口,也就是人们常说的DDR。

对于串口和并口那个速度快的问题,这就要看怎么描述这个问题了。

从线速率(linerate)来看,比如DDR3-1600的最大线速率为1600Mbps(也就是1.6Gbps)。那再看看目前主流的SerDes的线速率能达到多少那,Xilinx的16nm Ultrascale+FPGA提供的SerDes能够达到32Gbps的速度。而最近Credo演示的双模SerDes芯片,有112Gbps PAM4/56Gbps NRZ的性能表现。所以通常理解的高速串口比并口快,主要是从线速率的角度比较。

当然从总数据带宽的角度看,比如64bit DDR3-1600的最大数据带宽也超过了100Gbps(64*1.6Gbps)。也能提供不俗的总带宽表现。其实SerDes也可以多通道并行使用,比如像PCIe协议的x4、x8、x16模式。尽管也存在多通道的对齐问题。但呈现的总带宽相对来说会更大些。高速串口技术的发展未来仍是提升单通道速度和多通道并行使用相结合。所以,串并口的概念可能会进一步模糊。整体结果是提供不断改进升级的数据总带宽。

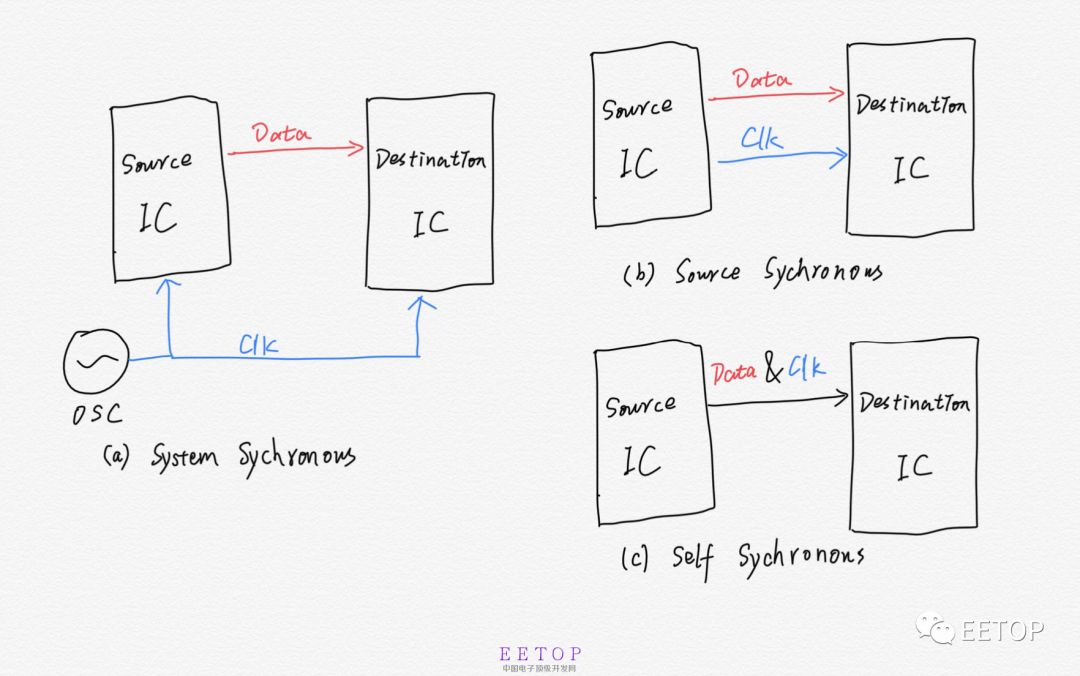

还需要了解下不同芯片间通过同步接口通信的3种基本时序模型。如图3中(a/b/c),分别是系统同步,源同步和自同步的方式,图中省略了板级和芯片内部的布线延迟。最初接口速率较低时,使用系统同步的方式就能满足要求,随着接口速度的提升,严格的时序要求会使用数据和时钟同步发送的方式,比如像DDR的数据要同步dqs时钟线那样。

图3

自同步其实就是目前SerDes中采用的方式,接口传送的数据中包含了时钟的信息,通过接收端(Rx)的时钟数据恢复(Clock Data Recovery,CDR)电路完成对接收数据的时钟抽取和数据再采样。最终恢复出正确的数据。

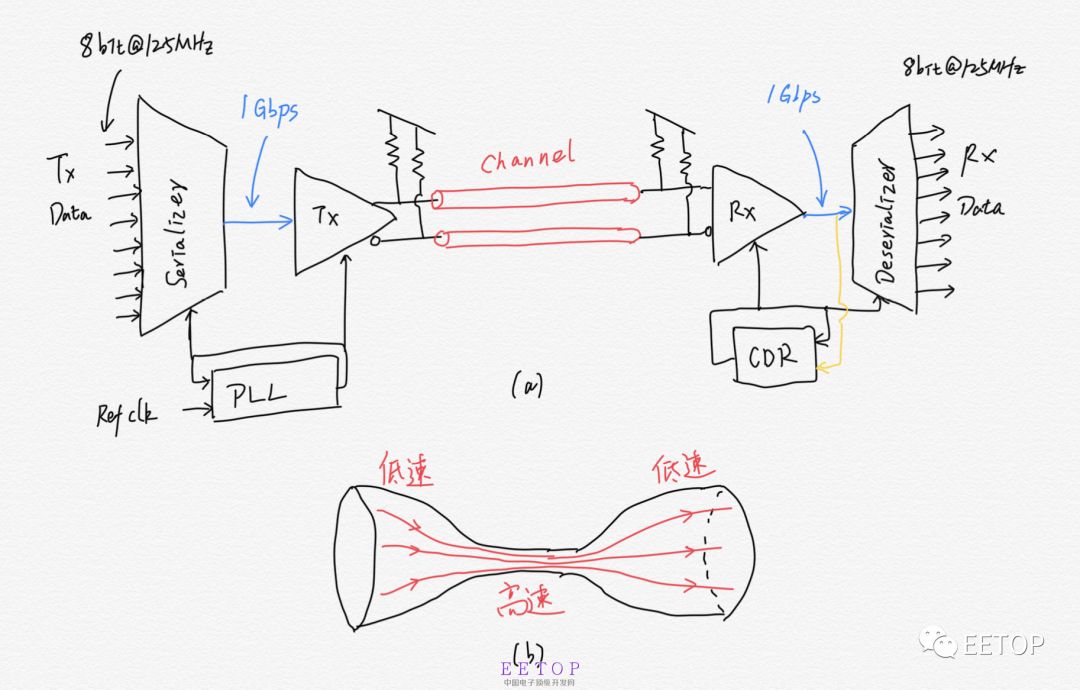

对于高速串行链路(High Speed Serial Link)使用的SerDes技术,其中SerDes是串化器(Serializer)和解串器(Deserializer)的简写,也基本说明了SerDes的原理。就是要完成并串和串并转换。SerDes是典型的数模混合系统,需要比较多的背景知识,数字电路和模拟电路、信号与系统、通信原理、微波和射频电路、电磁场、信号和电源完整性等,综合要求比较高,算是目前点到点(point-to-point)有线(wireline)通信的技术热点。

SerDes接口简单示意图如图4,并给出了不同位置的数据速率的例子。图(a)中时钟速率为125MHz的8bit并行数据(一个时钟周期8ns,共8bit数据),经过串化,转化为1Gbps的1bit串行数据(一个UI为1ns,包含1bit数据),经过发送器和通道到接收器,经过接收器处理后仍为1Gbps,解串后恢复为125MHz时钟速率的8bit并行数据。这个过程可以形象理解为图(b)的低速的拉瓦尔喷管,气流从截面逐渐减小的椎体到截面逐渐增大的椎体,“截面大处流速小,截面小处流速大”。

图4

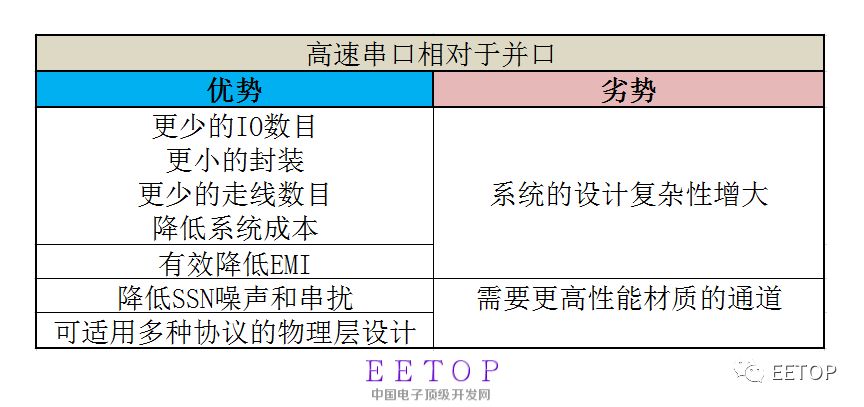

图4(a)为SerDes只是“单工”形式,可以看到,通过串化可以将IO数量从8个减少到2个(信号传输多数采用差分形式)。可以有效缓解芯片IO数目紧张的问题,同时减小PCB走线的复杂性。从经济性的角度,更小的封装和更少的PCB走线,线缆和连接器等,会整体降低系统成本。高速串口技术相对于并口的主要优劣势总结如图5中表格。

图5

从图4(a)也可初窥SerDes的技术,主要体现在几个方面。

第一,高频低抖动时钟的生成。比如对于10Gpbs数据率,内部需要产生至少10GHz的时钟(Single Date Rate,SDR)或5GHz的时钟(Double Date Rate, DDR)。随着SerDes的发展,内部PLL的时钟频率的不断提高,Ring PLL和LC tank PLL都是不可缺少的,时钟的抖动和各种各样的Jitter等对误码率(BER)的影响都需要充分分析。高性能时钟是整个SerDes系统设计的一个技术重点。

第二,信号完整性考虑。在传输线内容中我们初步了解到传输线的非理性特性,随着信号的数据率提高和通道长度的增加,发送器(Tx)发送的数据经过信道(channel)后衰减和码间干扰(ISI)的存在使得接收器(Rx)端的信号已经没了模样。为了把数据正确恢复出来,需要通过均衡器(Equalizer)均衡信道的衰减和数据的码间干扰。比如常见的有Tx的前馈均衡(FFE),Rx端的连续时间线性均衡(CTLE)和判决前馈均衡(DFE)等手段。

第三,自适应算法。Rx端的均衡通常需要满足不同材质和长度信道的特性,并对信号不同频率成分的衰减进行补偿。CTLE和DFE通常都会使用自适应算法(Self-Adaptive Algorithm)实时动态调整来应对信道的特性变化。如果不了解算法实现,就不能准确的理解DFE的本质。

关于自适应算法有很多的教材,比如Simon Haykin著的《自适应滤波器原理》,最近翻看,真的是头大。哎,后悔当初数学没有好好学,现在还在慢慢啃。只能说很难理解。

图6

第四,CDR环路。Rx端的另一个难点是CDR环路,CDR的实现有不同的实现方式。CDR的环路通常会包含了大量数字实现,准确的理解也很关键,对这部分的理解还在学习中,有机会再和大家分享。

第五,时序约束限制。当数据率升高时,对于DFE的判决反馈回路的时序设计提出了更高的要求。比如说对于50Gbps的SerDes,一个UI的时间为20ps,几乎和逻辑门的延迟相当,这就要求DFE的反馈回路的逻辑设计必须尽可能的简单。单独时钟速率会遇到困难,而采用PAM-4或PAM-8等信号方式就会显得很有前景。

SerDes是一个复杂数模混合系统,内部还包含了大量数字实现内容。8B/10B等编解码实现,PRBS生成和检查,环回测试、自适应算法实现,系统状态控制数字实现等等。

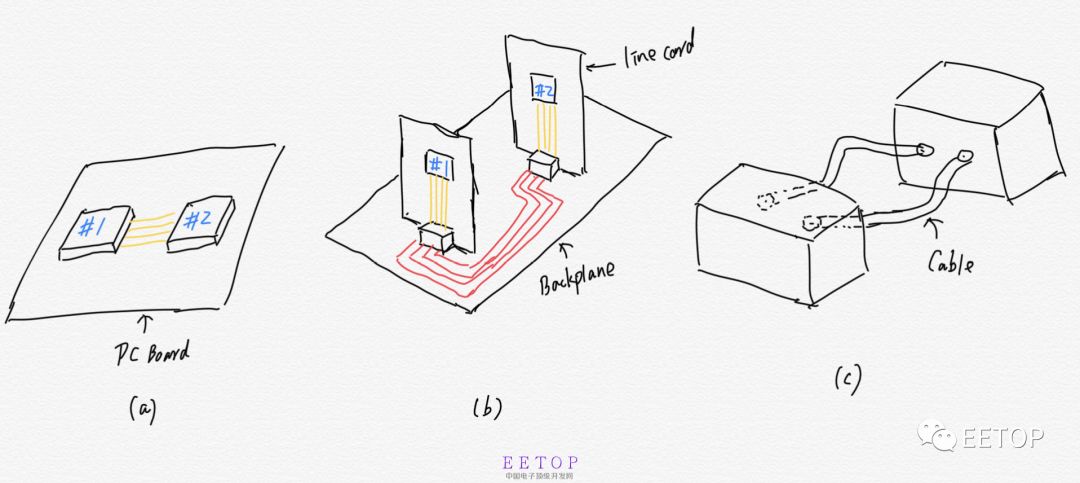

目前SerDes的应用,主要有Chip-to-Chip,Board-to-Board, Box-to-Box等形式,如图7(a/b/c)示意图。并在大型数据中心,通信骨干网络,消费电子等场景下都有应用。

图7

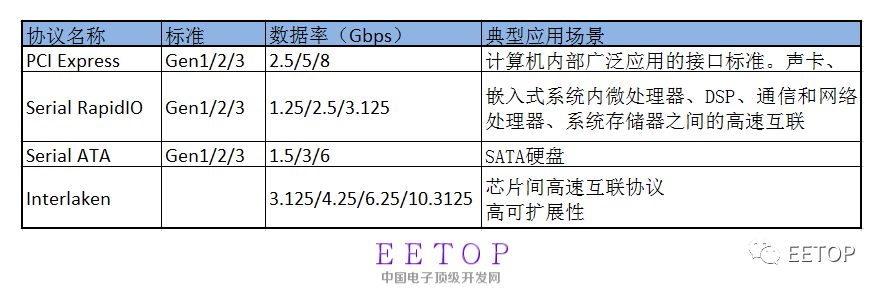

不同的应用场合也催生了不同的协议标准。如PCI Express,Serial ATA,Ethernet,Serial RapidIO和Aurora等。不同协议标准有着不同的速率,并且在不断的演进中。图8列出了几种协议的数据率,目前单通道的线速率主要是集中在Gbps以上。

图8

从协议的角度看,不同的协议通常会有不同的分层定义。我们关注的SerDes硬件实现大多集中在物理层。当然对协议更高层的了解能够帮助更好的理解底层硬件实现。

另附文中缩写术语全称:

NRZ Non-Return to Zero

PAM-4 Pluse Amplitude Modulation - 4 level

SerDes Serializer/Deseiralizer

Gbps Gigabit per second

CTLE Continuous Time Linear Equalization

DFE Desicion Feedback Equalization

FFE Feed Forward Equalization

ISI Inter-Symbol Interference

PRBS Pseudo-Random Binary Sequence

-

接口技术

+关注

关注

1文章

277浏览量

42359 -

SerDes

+关注

关注

8文章

238浏览量

37034

原文标题:SerDes概述

文章出处:【微信号:eetop-1,微信公众号:EETOP】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

回顾接口技术发展历史

回顾接口技术发展历史

评论