是时候改进您的时钟了

Graham Mostyn

几乎每个电子器件都需要一个时钟源。例如,单片机(MCU)使用振荡器来前进到下一条指令,无线电需要通过精确的振荡器来将射频信号混合到基带中加以处理。

智能联网设备的出现对时钟性能提出了更高的要求。本文解释了设计师如何在应对这些挑战的同时降低技术风险、缩短设计时间以及削减物料清单。我们着眼于采用石英和基于MEMS的技术的石英晶体、石英晶振(XO)和高度集成的时钟解决方案。

智能联网设备需要复杂的时钟树

MCU通常包括用于非精密计算应用的内部RC移相振荡器。这些振荡器使用集成的电阻-电容对来创建控制振荡器频率的时间常数。此类振荡器具有大约1%的精度并且表现出高抖动(在时钟转换的时序中会出现意外的随机波动)。 它们适用于不注重转换时序的应用,例如为计算用MCU提供时钟以及驱动一个简单的七段数字液晶显示屏(LCD)。显示屏需要多个时钟波形,但转换时序容差为几毫秒。此外,也可实现高达几Mbps的UART通信,这种情况下的时序容差为几百纳秒,但这同时也代表着简单RC振荡器的限值。

智能联网产品通过Bluetooth®、有线以太网、Wi-Fi®或其他连接协议与云端进行网络通信。由于涉及无线电和/或高速数据,因此需要精度达百万分之几(ppm)的低抖动精密时钟。

生成精密时钟所需的关键因素是稳定的参考频率,而这需要使用谐振器。谐振器是一种电子无源器件,在某些(谐振)频率下自然振荡的幅度高于其他频率——小提琴琴弦就是一个简单的例子。电子器件通常选用石英晶体和MEMS谐振器。谐振器的要求如下:

谐振频率随时间和温度变化呈稳定态势。这样可以避免时钟频率漂移。

高品质因数(Q),确保谐振器只响应很窄的频带。

能够在高信号电平下工作,从而在输出端达到良好的信噪比

第二项和第三项对于确保低抖动时钟信号至关重要,可实现稳定的时序转换。

由于谐振器是无源器件,因此需要受控的能量来维持振荡并产生参考频率。将谐振器以反馈配置耦合到维持放大器可实现这种稳定的振荡。如果石英晶体或MEMS谐振器配有合适放大器,会非常适合作为10 Mbps及以上域中数据传输的频率参考。

石英谐振器具有高Q值和高输出能力,适用于抖动必须极低的应用。 可以实现100飞秒的相位噪声(在传统的12 kHz至20 MHz带宽中测量)。MEMS谐振器能够以非常稳定的频率在扩展级温度下工作,而且兼具极高的可靠性以及抗冲击和振动性能,并能够实现超小型时钟解决方案(接近1平方毫米)。 MEMS谐振器具有较高的Q值和较低的输出;可实现500飞秒的相位噪声,而近期的谐振器设计也在不断降低该值。 例如,许多现代网络应用(例如PCIe)都支持较小的集成带宽,因此这两种技术都非常合适。

在嵌入式系统中实现时钟

在嵌入式系统中,可通过三种常见的谐振器实现来产生时钟信号。

将石英晶体直接连接到“目标SoC”(将由时钟驱动)

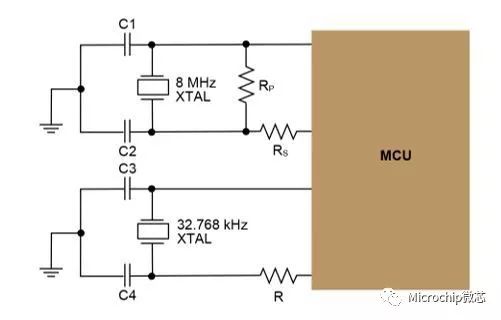

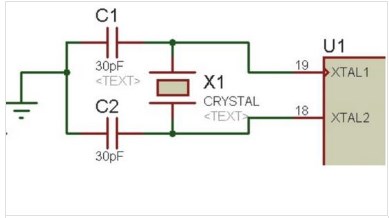

图1:两个晶体直接连接到MCU,显示负载电容和串联电阻

通过石英晶振(XO)为整个系统创建一个时钟输出

图2:晶振由石英晶片组成,传统上采用陶瓷封装并带有金属盖

基于石英或MEMS的时钟发生器(以低频和高频[>50 MHz]创建一个或多个时钟输出)

图3:集成时钟发生器将MEMS(或晶体)谐振器与振荡器相结合,并通过可编程PLL和缓冲输出级扩展功能

-

振荡器

+关注

关注

28文章

3832浏览量

139081 -

嵌入式系统

+关注

关注

41文章

3593浏览量

129466 -

智能联网

+关注

关注

0文章

21浏览量

10888

原文标题:专家技术文章:是时候改进您的时钟了

文章出处:【微信号:MicrochipTechnology,微信公众号:Microchip微芯】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

嵌入式技术在物联网中的应用

嵌入式系统的PCI Express时钟分配

嵌入式设计经验:ARM-WinCE平台时钟同步设计

智能联网设备需要复杂的时钟树,在嵌入式系统中实现时钟

智能联网设备需要复杂的时钟树,在嵌入式系统中实现时钟

评论