文.Joseph Juan

USB规范是USB开发者论坛(USB IF)维护的产业标准,规定了许多个人计算机与外接接口设备间USB连接事项,比如电缆、接头、连接协议、通讯以及电源。作为目前最新版本的USB规范,USB 3.2将数据传输带宽大幅提升至10Gbps。USB 3.2 Gen2规范大幅提升了数据编码效率,提供的速率比USB 3.1 Gen1一代提供的速率(5Gbps)快一倍。

USB Type-C(也作USB-C)支持最新的USB 3.2标准。特性完备的USB-C电缆可支持10Gbps的数据吞吐量,是USB 3.2 Gen1标准的两倍。根据DisplayPort 1.4标准,在每路显示输出中该电缆支持四信道,每信道数据传输率可达8.1Gbps。DisplayPort则是以数据报的形式通过数字接口同时传输高分辨率音视频信号,总带宽可达32.4Gbps。高速的数据传输率和常见的嵌入式时钟架构的结合,有助于在差分讯号对信道中传输海量的数据和影音频号。

讯号完整性成高速讯号传输挑战

高速讯号在通过电缆或印刷电路板传输时,衰减现象很严重,甚至会导致讯号畸变。讯号通常透过传输线路传输,长度为10到12英吋的传输线路导致的通道插入损耗达20dB或更高。此外,反射、串扰、杂波讯号和散射都会导致讯号完整性与眼图区间恶化。讯号传输距离增加导致讯号衰减程度加重且讯号质量下降,进而导致数据位错误,无法在远程或接收端成功复原传输的讯号。

为避免或减轻这种现象,须为数据传输率为8.1Gbps以上的串行接口设置中继器,以滤除随机杂波和系统噪声,使讯号符合规范要求。中继器通常部署在信道途中,以补偿信道损耗。目前有两种类型的中继器:Retimer和Redriver。Retimer可对来自上游信道的讯号进行均衡,使用CDR恢复时钟讯号,并生成数字应激讯号,传送至下游信道。Redriver可均衡来自上游信道的讯号并将其传送至下游通道。它的输出讯号在输入讯号的连续驱动下生成。Redriver不包含CDR,也不执行复位时操作。

桌机/笔电USB-C与USB-A接口讯号改善方案

在所有互联协议中,数据传输速率不断提高,对CPU的性能要求更高,进而提升整个信道的数据传输速率。当主流CPU供货商不断减小其芯片尺寸以降低功耗、维持性价比时,这种情形尤其明显,最终导致保证讯号符合规范要求的最大传输路径长度不断缩短。

英特尔(Intel)的CNL和CFL平台USB3.1 Gen 2应用设计指南建议OEM厂商在使用USB-C接头时,使用基于Retimer的主动复用解决方案;在使用USB Type-A接头时,使用Retimer方案,以保证讯号完整性,获得更好的JTOL区间。Retimer应用必须符合USB 3.2规范的附录E,在USB 3.2 Gen2模式下能够提供23dB的损耗补偿。

USB 3.2规范定义了以下两种类型的Retimer:

·SRIS Retimer

在SSC无关参考时钟(Separate Reference clock Independent of SSC, SRIS)Retimer应用中,传输时钟讯号来自本地参考时钟,与接收端复原的时钟讯号无关。

·BLR

数据位Retimer(Bit-Level Retimer, BLR)的应用中,传输时钟讯号来自接收端复原的时钟讯号(链路训练的某些阶段除外)。

图1 对桌机/笔电的USB-C插入损耗进行补偿设计

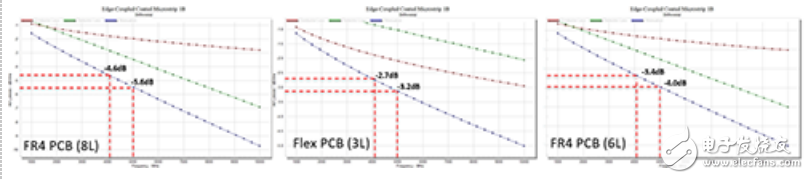

图1与图2为对桌机/笔电的USB-C插入损耗进行补偿的设计。从图1和图2可知,DisplayPort的插入损耗为10.7dB(数据传输率8.1Gbps);USB-3的插入损耗为12.8dB(数据传输率10Gbps)。

图2 对桌机/笔电的USB-C插入损耗进行补偿设计

硅谷数模(Analogix)对此进行了一项测试,测试环境如下:

1. USB主机:Gigabyte GB-BSi5HA- 6200

2. 插入损耗板:15英寸(USB-C -micro-USB, FR-4)

3. Retimer(ANX7440)EVB

4. USB设备:Sandisk SSD Plus

5. 示波器:DS0Z334A(33GHZ)

图3为测量位置与测量结果。安装了Retimer的系统可望在主机到设备之间对最多23dB的插入损耗进行补偿(图4)。Retimer简化了PCB布线,可以在不牺牲平台性能的前提下,确保个人计算机主板和USB/DisplayPort电缆实现高吞吐量讯号传输。

图3 USB主机讯号测试示例图

图4 安装Retimer的系统对插入损耗进行补偿

DisplayPort讯号改善方案

若要透过主动电缆和菊花链实现多个Retimer之间的无缝互通,须具备功能完备的DisplayPort Retimer,支持链路训练可调PHY中继器(LTTPR)模式和带AUX Snooper的透明模式。

USB-A/USB-C讯号改善方案

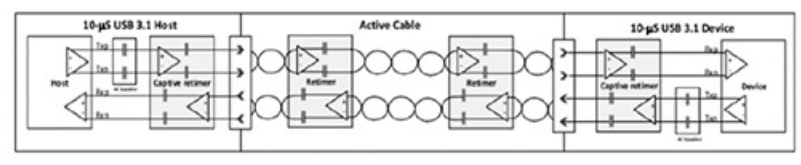

使用菊花链连接多个Retimer可以在通用连接系统中实现多功能的USB-C互联。USB-C菊花链提高了扩展USB-C电缆的讯号完整性。USB 3.2附录E可确保以菊花链形式连接的多个Retimer之间的无缝互连,若要满足此标准,须在USB 3路径部署采用SRIS或BLR架构且能够进行23dB损耗补偿的Retimer。USB 3.2规范附录E的E.1.2.1.2小节给出了Retimer连接模型的要求,该规范支持Pending_HP_Timer_timeout配置下的4-Retimer连接,适用于10-μs USB 3.2主机和设备。

4-Retimer连接指10-μs主机或设备与另一个10-μs主机或设备的连接。在这种情况下,最多可使用四个Retimer,图5显示了一个4-Retimer连接,其中包括一个10-μs主机和一个10-μs USB 3.1设备,它们之间透过一条主动电缆连接。而针对下一代10Gbps笔电与桌机的Retimer应可实现4-Retimer菊花链连接功能,满足最新的USB 3.2规范附录E的要求,以满足USB 3.2 CTS互通测试要求的前提下,对USB 3.1 Gen 2 10Gbps讯号高达23dB的信道损耗进行补偿。

图5 10-μs主机与10-μs设备间的连接

中继器不仅用于尺寸较大的PCB电路板和较长的传输路径,还可用于尺寸非常小的平台,比如智慧手机。理由如下:

1. CPU芯片组无法为各信道提供足够的输出驱动。

2. 部分信道会经过讯号损耗较大的PCB区域。

3. 天线附近的电磁干扰限制讯号的强度。

4. 与接头相连的电缆会增加通道长度。

智能型手机讯号改善方案

智慧手机会连接不同的外接显示设备,也会连接各种配件。如果不使用Retimer,智能手机内部电路板的DisplayPort 1.4接口的损耗将为8到10dB,USB 3.2界面损耗将为10到12dB,这些损耗会导致智能手机内部电路板性能下降,进而使DisplayPort 1.4数据传输率下降至5.4Gbps以下,使USB 3.2数据传输率下降至5Gbps以下。所以,应用处理器(AP)制造商通常建议将Retimer用于DisplayPort 1.4和USB 3.2的数据传输。

而针对下一代智慧手机设计的Retimer必须支持在各种长度的电缆上进行DisplayPort 1.4(8.1Gbps)和USB 3.1 Gen2(10Gbps)的高带宽数据传输。智能手机通常采用高速USB-C接口,而下一代应用处理器在Retimer的帮助下可在USB-C接头上实现极高的数据传输率,使得智能手机成为实现VR应用的理想选择,因为连接头戴式VR显示器要求同时支持DisplayPort和USB 3传输,以通过细长电缆传输刷新频率为90Hz、分辨率为4K×2K的视频信号。

智能手机连接到USB-C接口的监视器时通常使用DisplayPort替代模式,其有两个数据信道,在60Hz刷新频率下最高可达4K分辨率。如果是连接USB-C配件,则通常为DisplayPort到HDMI连接,在60Hz刷新频率下可实现4K分辨率和USB 3的数据传输率。Retimer能够在上述高数据传输率情况下确保数据完整,并保障主机到同步设备间的影像与数据传输。

电缆讯号改善方案

为外壳处的接头部署中继器或在接头外壳内部署中继器时,可以使用较细较长的电缆。主动电缆在接头内的PCB上部署了中继器。目前市场提供用于连接USB、DisplayPort、HDMI、PCI Express、SATA和SAS等接口的主动电缆(图6)。

图6 主动电缆接头内的PCB上部署中继器

针对长电缆情况,Retimer可以在长度为2公尺、5公尺甚至7公尺的主动电缆的两端进行讯号复原,使得低成本电缆解决方案能够满足高速DisplayPort和USB 3.2讯号传输的性能和兼容性方面的要求。

Retimer供货商须与主流CPU和AP提供商密切合作,努力确保其讯号改善产品满足链路训练要求,提供所需的兼容性通道,并共同设计模拟模型,以进一步改进设计,提高在高速接口使用Retimer的成功率。

(本文作者为Analogix资深营销经理)

本文来源:新通讯2018年6月号208期《技术前瞻》,如有侵权请联系邮箱:jftougao@elecfans.com

-

usb

+关注

关注

60文章

7949浏览量

264855 -

中继器

+关注

关注

3文章

390浏览量

28274 -

完整性

+关注

关注

1文章

12浏览量

10331 -

Retimer

+关注

关注

2文章

9浏览量

7428

发布评论请先 登录

相关推荐

确保信号完整性的电路板设计准则

信号完整性与电源完整性的仿真分析与设计

如何确保PCB设计信号完整性

有什么办法可以确保信号完整性?

信号完整性与电源完整性的相关资料分享

确保信号完整性的电路板设计准则

确保信号完整性的电路板设计准则

浅谈确保信号完整性的电路板设计准则

PCB信号完整性有哪几步_如何确保PCB设计信号完整性

如何确保PADS设计信号的完整性

信号完整性与电源完整性的详细分析

中继补偿传输信道耗损 Retimer确保讯号完整性

中继补偿传输信道耗损 Retimer确保讯号完整性

评论