新的 “单芯片时钟树” 增加了创新的多配置支持和集成晶体选项。

中国,北京-2018年8月14日- Silicon Labs (亦称“芯科科技”,NASDAQ:SLAB)宣布扩展了其Si5332任意频率时钟产品系列,新版本Si5332将时钟IC和石英晶体基准整合在同一封装内,简化了电路板布局布线和设计。一体化Si5332解决方案可确保产品在整个使用周期寿命内可靠启动和运行,而不像传统解决方案因采用不同供应商时钟IC和晶体而存在互操作性风险。Silicon Labs还在整个Si5332产品系列中引入了多配置支持,使开发人员能够将多个时钟树配置整合到单一型号之中。

传统的时钟发生器依赖于外部的分立石英晶体频率参考。开发人员必须仔细设计晶体接口电路,以实现容性负载匹配,确保精确的时钟合成。为了最大限度的降低噪声耦合的风险,开发人员通常不能在晶体附近布置高速信号,这样会限制印制电路板(PCB)布线的灵活性。

Si5332时钟发生器通过在封装内集成高质量的晶体参考消除了这些设计限制。除了简化设计之外,这种方法还可最大限度的减少PCB总体占用空间,并最大限度的提高PCB布线灵活性。由于片内晶体免受外部PCB噪声影响,因此与使用外部时钟源(190fs RMS,12kHz-20MHz)的Si5332版本相比,片内集成晶体的Si5332器件可提供更低的抖动(175fs RMS)。

Silicon Labs时钟产品总经理James Wilson表示:“Si5332时钟发生器提供业界最高水平的时钟集成度,可在10/25/100G数据中心、通信、工业和广播视频应用中实现完整的时钟树整合。这种完整的时钟解决方案降低了供应链的复杂性,因为其来自单一供应商Silicon Labs。”

Si5332时钟利用Silicon Labs久经考验的MultiSynth技术,提供具有出色抖动性能的任意频率、任意输出时钟合成。Si5332支持多达12个时钟输出,每个输出时钟可选择不同信号格式(LVDS、LVPECL、HCSL和LVCMOS)和独立的1.8-3.3V VDDO,可连接各种FPGA、ASIC、以太网交换机/PHY、处理器、SoC,以及包括PCIe在内的高速SerDes。最终,这些功能特性使得Si5332能够在单一IC中整合整个时钟树。

新的多配置功能将时钟集成提升到一个新的水平,可在单一IC中整合多达16种独特的时钟树配置。单一Si5332型号现在可以取代晶体振荡器(XO)+缓冲器、时钟发生器、时钟发生器+缓冲器时钟树。每种独特的配置均可通过硬件引脚进行引脚选择,无需使用串行接口来重新配置器件以支持不同的频率。多配置功能特性利用单一型号简化跨域多平台和设计的器件认证,而不是引入不同的时钟器件去支持不同的频率组合。

Silicon Labs ClockBuilder Pro (CBPro)软件支持Si5332时钟发生器,简化了器件配置和定制。通过CBPro,客户可以根据具体要求定制时钟解决方案,并可在不到两周之内收到样片。CBPro为每个器件生成定制的可订购型号,并且没有最低订购数量或非经常性工程费用和限制。

关于Silicon Labs

Silicon Labs(NASDAQ:SLAB)是领先的芯片、软件和解决方案供应商,致力于建立一个更智能、更互联的世界。我们屡获殊荣的技术正在塑造物联网、互联网基础设施、工业自动化、消费电子和汽车市场的未来。我们世界一流的工程团队创造的产品专注于性能、节能、互联和简易化。

-

振荡器

+关注

关注

28文章

3858浏览量

139512 -

缓冲器

+关注

关注

6文章

1999浏览量

45752 -

时钟

+关注

关注

11文章

1750浏览量

131953 -

时钟发生器

+关注

关注

1文章

203浏览量

67461 -

芯科科技

+关注

关注

1文章

378浏览量

15709

发布评论请先 登录

相关推荐

基于兆芯CPU的全栈SCADA一体化方案荣获信创优秀方案奖

华为入选中国云网安一体化能力领导者

英特尔发布全新企业AI一体化方案

英特尔发布全新企业AI一体化解决方案

千方新能源停充一体化解决方案

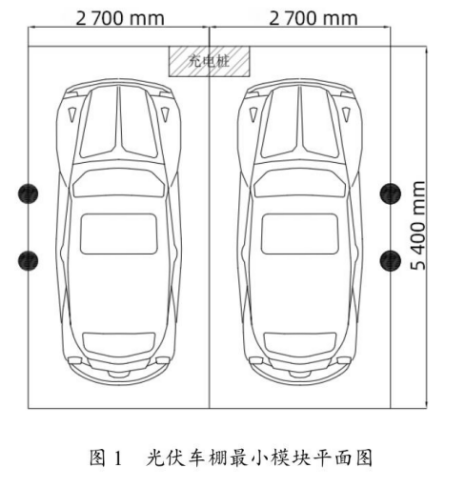

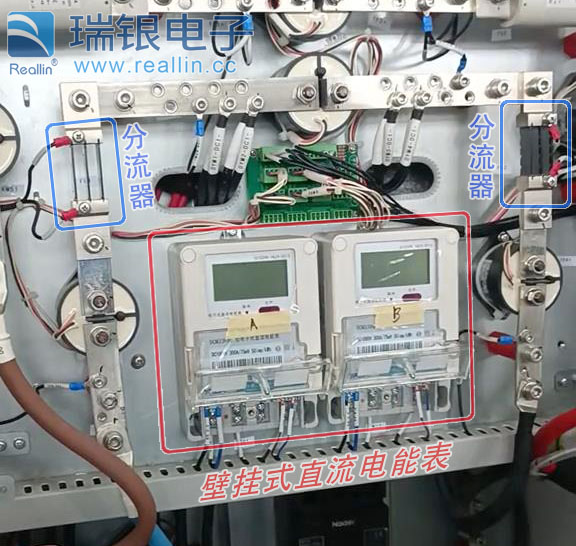

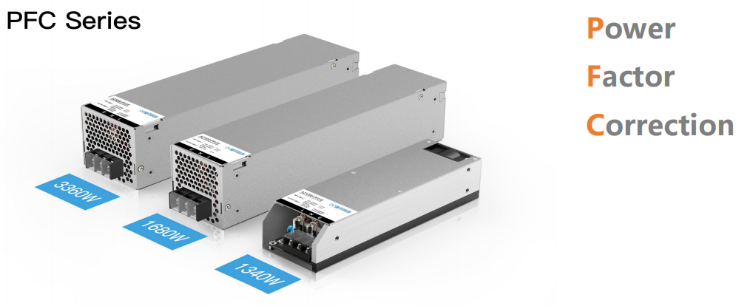

光储充一体化电站建设解决方案

物联网水肥一体化系统方案

浅析光储智能一体化充电站的解决方案与应用

《嵌入式机电一体化系统设计与实现》读后感

揭秘! 经纬恒润“车路云一体化”方案研发服务背后的科技驱动力

芯科科技推出任意频率时钟一体化Si5332解决方案

芯科科技推出任意频率时钟一体化Si5332解决方案

评论