摩尔定律快到尽头,半导体如果要维持其高科技产业的特性,必须有手段持续性的创造新价值。Pixabay

摩尔定律快到日暮时分了,套用杜牧也是以日暮为起头的诗句(注):「长晶犹似卖楼人」,半导体人好似房地产开发商,最重容积层率。平面已盖无可盖,现在要起高楼了。

先是2.5D/3D封装,这已是行之有年的技术。然后就一下子跃进到真正的3D工艺-3D NAND Flash。几十层的线路、结构,用4、5层的光罩工艺就能成就,成本极低。可是这样的技术,只能用于具有特殊条件的元件。

第一个是线路内的单元(cell)排列要有高度的重复性,互联机路简单,象是存储器。

第二个是每个单元内有些结构可以与邻近单元相连接,譬如像charge trap NAND Flash中储存电荷的绝缘体。每一单元内的绝缘体虽然相连,但是储存于各单元内的电荷困在绝缘体内的特定位置,不会流动至另一单元,不至于影响储存功能。当把平面的结构变成垂直方向增长的时候,这些可以相连的结构也可以垂直不间断的沉积,对于整体工艺的简化有相当的帮助。

所以在3D NAND Flash工艺中,各大厂家纷纷从2D的floating gate工艺转为charge trap,因为floating gate工艺中储存电荷的floating gate物质是导体,而各单元间的floating gate若相连,每个单元储存的信息会随电荷流动而丧失。因此每层之间各单元的floating gate必须蚀刻断开,这对于3D工艺增加不少麻烦。

这样的3D工艺由于关键蚀刻技术与设备的突破,前程能见度还不错,到2024年有望达近200层。中短期内是能替代摩尔定律、挑起增加半导体新经济价值大梁的技术。

不完全符合上述条件的元件呢-譬如新兴存储器的PCRAM和ReRAM,还有cross bar工艺可用。只是cross bar工艺存储器虽然也是一层一层的堆叠上去,但是每一层都需要个别的光罩处理,工艺费用下降有限。但是芯片的效能可以提升,存储器密度也可以持续增长。目前cross bar大致是20几纳米的工艺、堆叠2层;到2022年,预计工艺可以推进至10几纳米、堆叠8层,还有些增长空间。

如果是其它的组合呢?譬如说是CPU加存储器芯片,显然上述两种方式都不适用,现在被认为“promising”的三维单片堆叠(3D monolithic stacking)技术可能是个解决方案,至少DARPA是这么想的。

三维单片堆叠基本上是多芯片堆叠,先将需要高温工艺的芯片做好,然后将其它已半制造好的芯片以离子切割(ion cut,基本上是氢离子)方式打薄,粘着于原来的芯片之上,继续后面的低温工艺。由于芯片内各模块得以在最适宜工艺处理,整体芯片的表现及成本可以与用更先进工艺的平面芯片媲美,而老旧的晶圆厂得以延续其生命周期。

当然,三维单片堆叠还有许多挑战待解决,譬如不同层间模块的设计需要有好的EDA、多层芯片散热问题、层间对准问题、多模块布线问题等。

半导体如果要维持其高科技产业的特性,必须有手段持续性的创造新价值。新的设计方法、新的元件、新的材料都可能创造新的价值,但是三维工艺看来最耐久,因为有机会像摩尔定律般的重复如法炮制!

注:改自杜牧金谷园一诗尾句,原诗为:繁华事散逐香尘,流水无情草自春。日暮东风怨啼鸟,落花犹似堕楼人。

-

半导体

+关注

关注

334文章

27253浏览量

217931 -

存储器

+关注

关注

38文章

7481浏览量

163751 -

摩尔定律

+关注

关注

4文章

634浏览量

78983

原文标题:【名家专栏】半导体的3D之路-兼论三维单片堆叠

文章出处:【微信号:DIGITIMES,微信公众号:DIGITIMES】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

创想三维助力遵义教育,百台3D打印机捐赠仪式圆满举行

三维堆叠封装新突破:混合键合技术揭秘!

三维打印技术原理

SK海力士五层堆叠的3D DRAM生产良率达到56.1%

德国蔡司工业级3D三维扫描仪抄数机

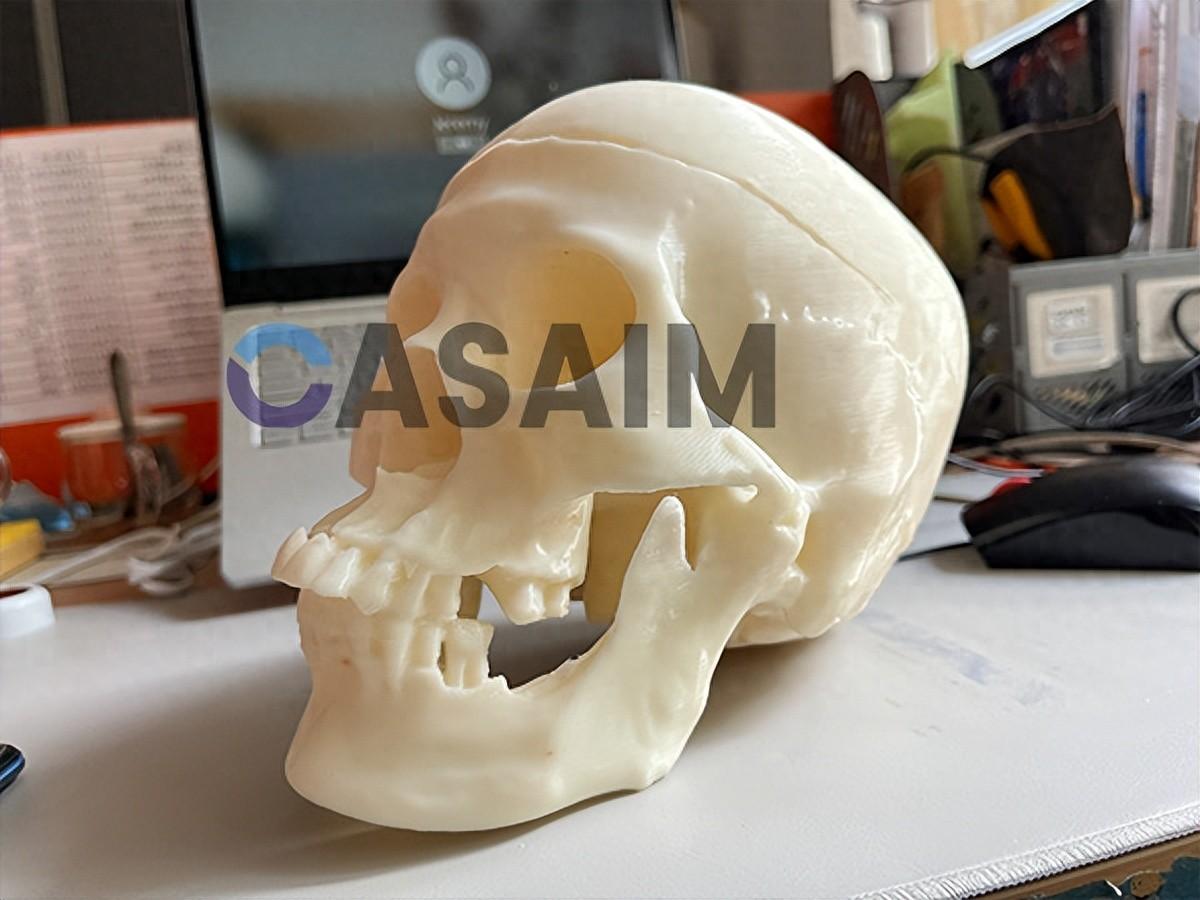

三维扫描与3D打印在法医头骨重建中的突破性应用

奥比中光与创想三维联合打造的高精度3D扫描仪正式发布

泰来三维| 高精度工业3D扫描助力模具检测和逆向设计“数字化”发展

泰来三维|见过三维扫描乌贼吗?三维扫描助力仿生设计学研究

珠三角石油工业压力阀三维扫描逆向3d建模设计服务

半导体的3D之路-兼论三维单片堆叠

半导体的3D之路-兼论三维单片堆叠

评论