PCIe总线错误检测囊括了链路(Link)上的错误以及包传递过程中的错误,如下图所示。用户设计的应用程序层中的错误不属于链路传输中的错误,不应当通过PCIe的错误检测与处理机制处理,一般可借助设备特殊中断(Device Specific Interrupt)等合适的方式进行报告与处理。

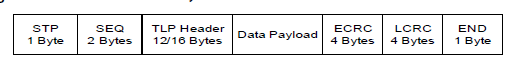

包传递过程的错误主要通过CRC编码来检测。PCIe定义了两种CRC——LCRC和ECRC。其中LCRC(Link CRC)由数据链路层产生和校检,用于检测从一端的数据链路层发送到另一端的数据链路层的TLP是否发生的错误。而ECRC(End-to-end CRC)由事务层产生和校检,且ECRC是可选的。

有人可能会质疑ECRC存在的必要性,因为LCRC已经对TLP进行了CRC校检,在此基础上多加一层ECRC可能是没有必要的。这里来简单地说明一下,一般情况下(尤其是没有Switch的简单PCIe总线系统中),ECRC的确是没有必要存在的。ECRC主要为解决Switch中传输的可能错在的传输错误问题的,换句话说,如果用户的设计中并没有Switch(只是简单的Root与Endpoint的端对端直连),完全可以不使用ECRC。

如下图所示,假设来自Endpoint的TLP被正确地传输到Switch的Downstream输入端口(Ingress Port),Downstream输入端口中的数据链路层也完成了对其的LCRC校检,且未发现错误。然后Switch会将该LCRC移除,并添加新的序列号(Sequence Number),随后重新计算LCRC,再将该TLP发送至Switch的Upstream输出端口(Egress Port)。显然,在此过程中TLP是不受保护的,一旦期间数据传输遇到错误等异常,可能会导致重新计算LCRC前的数据已经受到了破坏,且仅仅使用LCRC是无法发现这样的错误的。

注:关于序列号(Sequence Number),可以参考前面的关于Ack/Nak的相关文章。

需要注意的是,ECRC是AER中的一部分,要想使用ECRC,该PCIe设备必须是支持AER的。

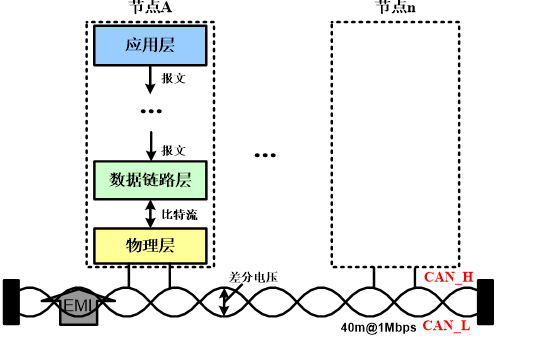

如果按照错误产生的层(Layer)来分,则可以分为物理层错误,数据链路层错误和事务层错误。

物理层错误(Physical Layer Errors)主要有:

· 8b/10b编解码异常

· Framing异常(8b/10b编码中是可选的,128b/130b中是必选的)

· Elastic Buffer错误(可选的)

· 起始字符失锁(Loss of Symbol Lock)或者通道对齐失锁(Lane Deskew)(可选的)

数据链路层错误(Data Link Layer Errors)主要有:

· LCRC校检失败

· 序列号(Sequence Number)异常

· DLLP中的16-bit CRC校检失败

· 链路层协议错误(Link Layer Protocol Errors)

事务层错误(Transaction Layer Errors)主要有:

· ERCR校检失败(可选的)

· 异常的TLP(Malformed TLP)(即TLP的格式异常)

· 流量控制协议异常(Flow Control Protocol Violation)

· 不支持的请求

· 数据损坏(Data Corruption,又称为Poisoned Packet)

· Completer Abort(可选的)

· 接收端溢出(Receiver Overflow)(可选的)

· 返回包超时(Completion Timeout)

· 不对应的返回包(Unexpected Completion,即Completion与发出的Request不一致)

当接收端的物理层检测到TLP存在错误时,如果再将该TLP继续传送至数据链路层和事务层必然也会发现错误。而过多的错误会让错误分析与处理变得困难。因此,没有必要在向上传递该TLP,而是将其直接扔掉,并报告相应的错误。

然而,即使这样,PCIe总线的错误报告中也有很多错误源自同一个错误源。因此需要对错误进行优先级排序,使得错误源(最底层的错误)的优先级更高,能够最先得到处理。PCIe总线中的错误优先级排序如下(优先级从高到低):

· 不可更正的内部错误(Uncorrectable Internal Error)

· 接收端Buffer溢出

· 流量控制协议错误

· ECRC校检失败

· 异常的TLP(Malformed TLP)

· AtomicOp Egress Blocked

· TLP包头异常(TLP Prefix Blocked)

· 访问控制服务(Access Control Services,ACS)异常

· MC(Multi-cast) Blocked TLP

· 不支持的请求(Unsupported Request,UR),Completer Abort(CA)或者不对应的返回包(Unexpected Completion)

· 接收到损坏的数据包(Poisoned Packet)

-

crc

+关注

关注

0文章

206浏览量

30997 -

Link

+关注

关注

0文章

104浏览量

28210 -

PCIe

+关注

关注

16文章

1496浏览量

89111

原文标题:【博文连载】PCIe扫盲——PCIe错误检测机制

文章出处:【微信号:ChinaAET,微信公众号:电子技术应用ChinaAET】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

PCIe简介及引脚定义

PCIe的技术原理详细说明

体验紫光PCIE之使用WinDriver驱动紫光PCIE

PCIe至USB的TMS320DM816xTMS320C6A816x和AM389x评估板详细资料概述

KeyStone中使用PCIE的应用案例和PCIE特征的详细描述

PCIe扫盲—PCIe错误检测机制的详细资料概述

PCIe扫盲—PCIe错误检测机制的详细资料概述

评论