DDR硬件设计要点

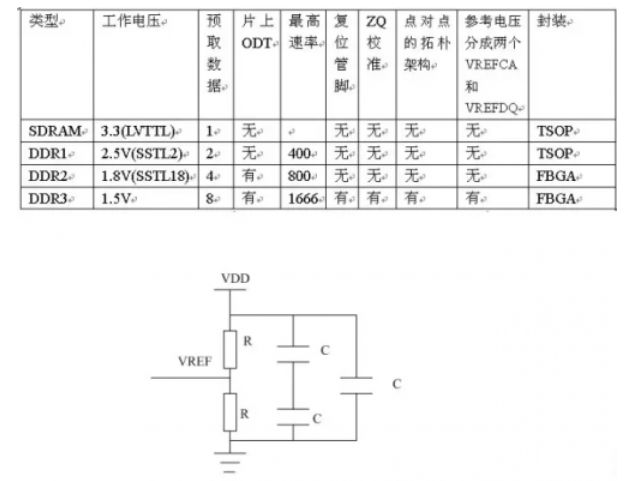

1. 电源DDR的电源可以分为三类:

a、主电源VDD和VDDQ,主电源的要求是VDDQ=VDD,VDDQ是给IO buffer供电的电源,VDD是给但是一般的使用中都是把VDDQ和VDD合成一个电源使用。

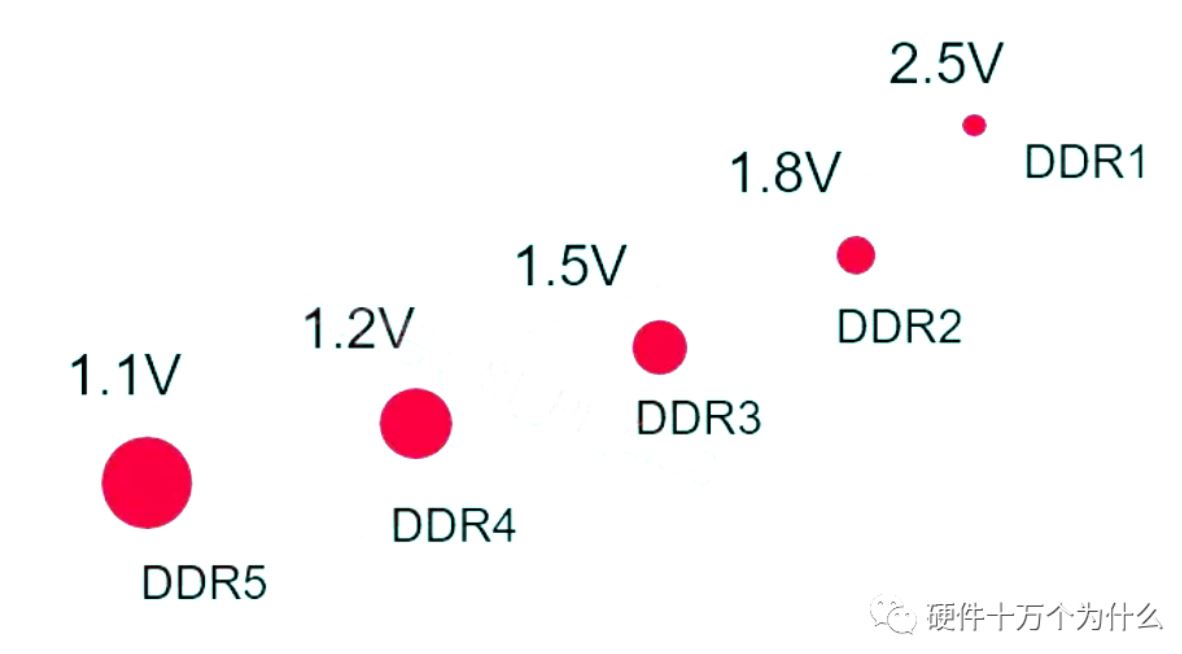

有的芯片还有VDDL,是给DLL供电的,也和VDD使用同一电源即可。电源设计时,需要考虑电压,电流是否满足要求,电源的上电顺序和电源的上电时间,单调性等。电源电压的要求一般在±5%以内。电流需要根据使用的不同芯片,及芯片个数等进行计算。由于DDR的电流一般都比较大,所以PCB设计时,如果有一个完整的电源平面铺到管脚上,是最理想的状态,并且在电源入口加大电容储能,每个管脚上加一个100nF~10nF的小电容滤波。

b、参考电源Vref,参考电源Vref要求跟随VDDQ,并且Vref=VDDQ/2,所以可以使用电源芯片提供,也可以采用电阻分压的方式得到。由于Vref一般电流较小,在几个mA~几十mA的数量级,所以用电阻分压的方式,即节约成本,又能在布局上比较灵活,放置的离Vref管脚比较近,紧密的跟随VDDQ电压,所以建议使用此种方式。需要注意分压用的电阻在100~10K均可,需要使用1%精度的电阻。 Vref参考电压的每个管脚上需要加10nF的点容滤波,并且每个分压电阻上也并联一个电容较好。

C、用于匹配的电压VTT(Tracking Termination Voltage)

VTT为匹配电阻上拉到的电源,VTT=VDDQ/2。DDR的设计中,根据拓扑结构的不同,有的设计使用不到VTT,如控制器带的DDR器件比较少的情况下。如果使用VTT,则VTT的电流要求是比较大的,所以需要走线使用铜皮铺过去。并且VTT要求电源即可以吸电流,又可以灌电流才可以。一般情况下可以使用专门为DDR设计的产生VTT的电源芯片来满足要求。

而且,每个拉到VTT的电阻旁一般放一个10Nf~100nF的电容,整个VTT电路上需要有uF级大电容进行储能。

在华为的设计中,在使用DDR颗粒的情况下,已经基本全部不使用VTT电源,全部采用电阻上下拉的戴维南匹配,只有在使用内存条的情况下才使用VTT电源。

一般情况下,DDR的数据线都是一驱一的拓扑结构,且DDR2和DDR3内部都有ODT做匹配,所以不需要拉到VTT做匹配即可得到较好的信号质量。DDR2的地址和控制信号线如果是多负载的情况下,会有一驱多,并且内部没有ODT,其拓扑结构为走T型的结构,所以常常需要使用VTT进行信号质量的匹配控制。DDR3可以采用Fly-by方式走线:

一个DDR3设计案例,来分析对比采用高阻抗负载走线和采用主线和负载走线同阻抗两种情况的差异。

如上图,Case1采用的是从内层控制器到各个SDRAM均为50ohm的阻抗设计。Case2则采用了主线40ohm,负载线60ohm的设计。对此通过仿真工具进行对比分析。

从以上仿真波形可以看出,使用较高阻抗负载走线的Case2在信号质量上明显优于分支主线都采用同一种阻抗的Case1设计。而且对靠近驱动端的负载影响最大,远离驱动端的最末端的负载影响较小。这个正是前面所分析到的,负载的分布电容导致了负载线部分的阻抗降低,如果采用主线和负载线同阻抗设计,反而导致了阻抗不连续的发生。把负载走线设计为较高的阻抗,用于平衡负载引入的分布电容,从而可以达到整条走线阻抗平衡的目的。

通过提高负载走线阻抗来平衡负载电容的做法,其实在以往的菊花链设计中是经常用到的方法。DDR3称这种拓扑为fly-by,其实是有一定的含义的,意在强调负载stub走线足够的短。

2. 时钟

DDR的时钟为差分走线,一般使用终端并联100欧姆的匹配方式,差分走线差分对控制阻抗为100ohm,单端线50ohm。需要注意的是,差分线也可以使用串联匹配,使用串联匹配的好处是可以控制差分信号的上升沿缓度,对EMI可能会有一定的作用。

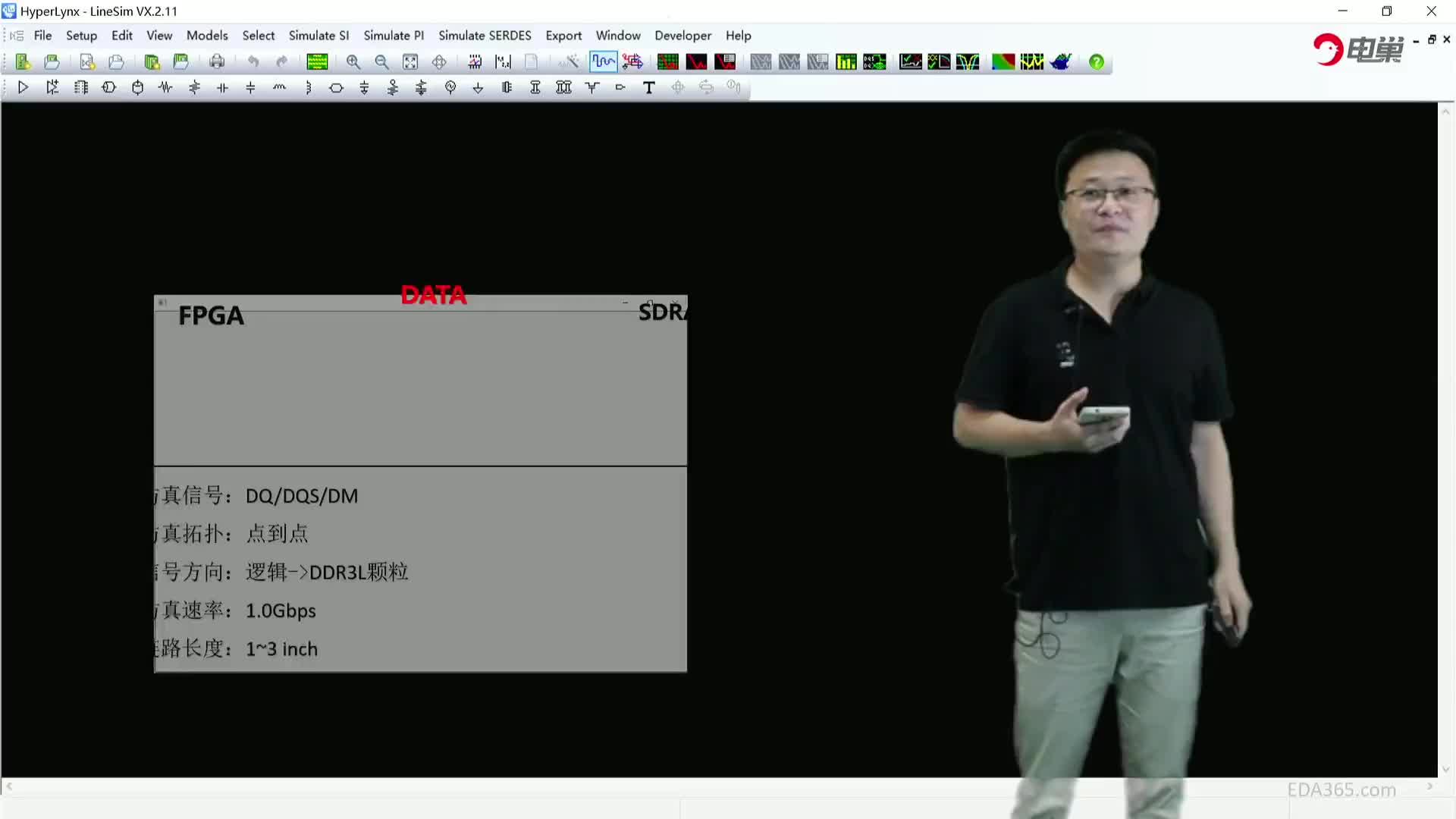

3. 数据和DQS

DQS信号相当于数据信号的参考时钟,它在走线时需要保持和CLK信号保持等长。DQS在DDR2以下为单端信号,DDR2可作为差分信号,也可做单端,做单端时需要将DQS-接地,而DDR3为差分信号,需要走线100ohm差分线。由于内部有ODT,所以DQS不需要终端并联100ohm电阻。每8bit数据信号对应一组DQS信号。

DQS信号在走线时需要与同组的DQS信号保持等长,控制单端50ohm的阻抗。在写数据时,DQ和DQS的中间对齐,在读数据时,DQ和DQS的边沿对齐。DQ信号多为一驱一,并且DDR2和DDR3有内部的ODT匹配,所以一般在进行串联匹配就可以了。

4. 地址和控制

地址和控制信号速度没有DQ的速度快,以时钟的上升沿为依据采样,所以需要与时钟走线保持等长。但如果使用多片DDR时,地址和控制信号为一驱多的关系,需要注意匹配方式是否适合。

5. PCB布局注意事项

PCB布局时,需要把DDR颗粒尽量靠近DDR控制器放置。每个电源管脚需要放置一个滤波电容,整个电源上需要有10uF以上大电容放在电源入口的位置上。电源最好使用独立的层铺到管脚上去。串联匹配的电阻最好放在源端,如果是双向信号,那么要统一放在同一端。如果是一驱多的DDR匹配结构,VTT上拉电阻需要放在最远端,注意芯片的排布需要平衡。下图是几种DDR的拓扑结构,首先,一驱二的情况下分为树状结构,菊花链和Fly-by结构,Fly-by是一种STUB很小的菊花链结构。DDR2和DDR3走菊花链结构都是比较适合的。走树状结构可以把两片芯片贴在PCB的正反两面,对贴减小分叉的长度。一驱多的DDR拓扑结构比较复杂,需要仔细进行仿真。

6. PCB布线注意事项

PCB布线时,单端走线走50ohm,差分走线走100ohm阻抗。

注意控制差分线等长±10mil以内,同组走线根据速度的要求也有不同,一般为±50mil。

控制和地址线及DQS线和时钟等长,DQ数据线和同组的DQS线等长。

注意时钟及DQS和其他的信号要分开3W以上距离。

组间信号也要拉开至少3W宽的距离。

同一组信号最好在同一层布线。

尽量减少过孔的数目。

7. EMI问题

DDR由于其速度快,访问频繁,所以在许多设计中需要考虑其对外的干扰性,在设计时需要注意一下几点

原理有性能指标要求的,易受干扰的电路模块和信号,如模拟信号,射频信号,时钟信号等,防止DDR对其干扰,影响指标。

DDR的电源和不要与其他易受干扰的电源模块使用同一电源,如必须使用同一电源,要注意使用电感、磁珠或电容进行滤波隔离处理。

在时钟及DQS信号线上,预留一些可以增加的串联电阻和并联电容的位置,在EMI超出标准时,在信号完整性允许的范围内增大串联电阻或对地电容,使其信号上升延变缓,减少对外的辐射。

进行屏蔽处理,使用金属外壳的屏蔽结构,屏蔽对外辐射。

注意保持地的完整性。

8. 测试方法

注意示波器的探头和示波器本身的带宽能够满足测试要求。

测试点的选择要注意选到尽量靠近信号的接受端。

由于DDR信令比较复杂,因此为了能快速测试、调试和解决信号上的问题,我们希望能简单地分离读/写比特。此时,最常用的是通过眼图分析来帮助检查DDR信号是否满足电压、定时和抖动方面的要求。

触发模式的设置有几种,首先可以利用前导宽度触发器分离读/写信号。根据JEDEC规范,读前导的宽度为0.9到1.1个时钟周期,而写前导的宽度规定为大于0.35个时钟周期,没有上限。第二种触发方式是利用更大的信号幅度触发方法分离读/写信号。通常,读/写信号的信号幅度是不同的,因此我们可以通过在更大的信号幅度上触发示波器来实现两者的分离。

测试中要注意信号的幅度,时钟的频率,差分时钟的交叉点,上升沿是否单调,过冲等。

时序中最重要,最需要注意的就是建立时间和保持时间。

-

电源

+关注

关注

185文章

17870浏览量

252178 -

DDR

+关注

关注

11文章

717浏览量

65598

原文标题:一文读懂电源DDR硬件设计要点

文章出处:【微信号:wujianying_danpianji,微信公众号:单片机精讲吴鉴鹰】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

DDR硬件设计的四大注意要点

关于计算机的硬件维护的浅析

关于DDR应用的一般注意要点的详细介绍

浅析电源DDR硬件设计技巧

浅析电源DDR硬件设计要点

浅析电源DDR硬件设计要点

评论