单片机P0端口的结构及工作原理

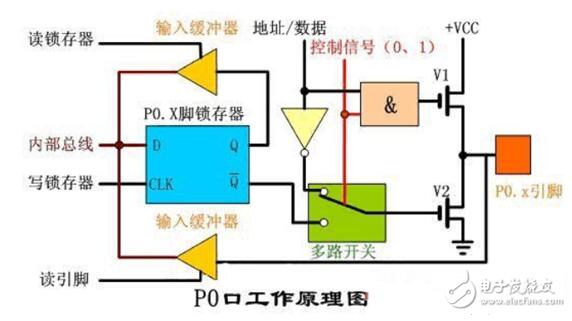

P0端口8位中的一位结构图见下图:

由上图可见,P0端口由锁存器、输入缓冲器、切换开关、一个与非门、一个与门及场效应管驱动电路构成。再看图的右边,标号为P0.X引脚的图标,也就是说P0.X引脚可以是P0.0到P0.7的任何一位,即在P0口有8个与上图相同的电路组成。

单片机端口上拉电阻的作用

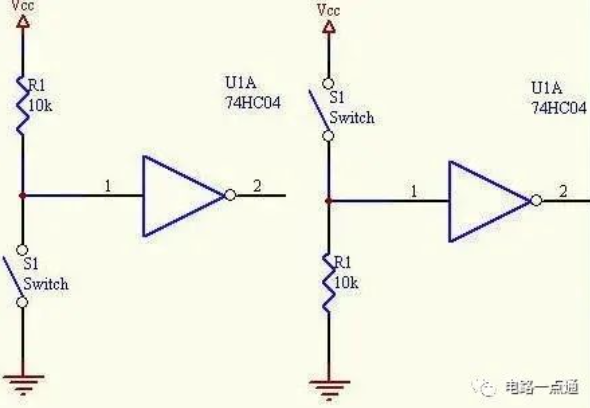

顾名思义,上拉就是把电平拉高(一般到电源),下拉就是拉低(一般到地)。上拉主要是为了提高灌电流驱动能力,相当于从电源借点儿功率到IO口,下拉主要是在IO口功率足够的情况下,为了保护IO口,静态时为0电平。

对于不同的单片机和端口,上拉电阻的作用不同,最常见的由于内部结构的问题,不能处于悬空状态。我就以51单片机进行叙述,以其P0口为例,P0口是集电极开路输出,也就是OC门,这种结构没有输出高电平的能力就相当于一个一端接地的开关, 按下去就输出低电平0V,断开就没有电压,是悬空状态。至于用不用上拉电阻,取决于外部电路,如果要输出高电平控制一个器件,而这个器件本身又没有内置上拉,就必须自己接一个上拉电阻,如果要用低电平控制一个器件,则可以不用加上拉。一般来讲,做板子时都会在P0口放一个排阻,10Kohm就可以了。

P0口作为I/O口输出的时候时,输出低电平为0 输出高电平为高组态(并非5V,相当于悬空状态,也就是说P0 口不能真正的输出高电平)。给所接的负载提供电流,因此必须接上拉电阻(一电阻连接到VCC),由电源通过这个上拉电阻给负载提供电流。P0作输入时不需要上拉电阻,但要先置1。因为P0口作一般I/O口时上拉场效应管一直截止,所以如果不置1,下拉场效应管会导通,永远只能读到0。因此在输入前置1,使下拉场效应管截止,端口会处于高阻浮空状态,才可以正确读入数据。

单片机p0口为什么要加上拉电阻

P0口内部没有上拉电阻,是开漏的,不管它的驱动能力多大,相当于它是没有电源的,需要外部的电路提供,绝大多数情况下P0口是必需加上拉电阻的。

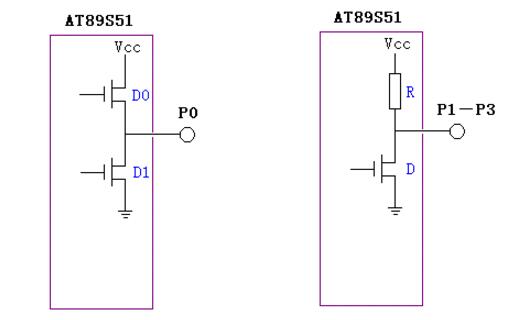

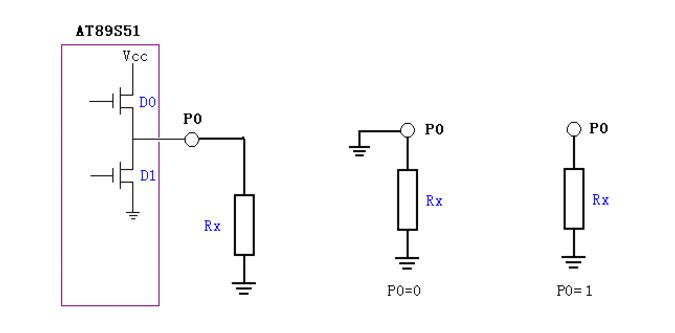

P0口和其它三个口的内部电路是不同的,如下图:

P0口是接在两个三极管D0和D1之间的,而P1-P3口的上部是接一个电阻的。P0口的上面那个三极管D0是在进扩展存储器或扩展总线时使用MOVX指令时才会控制它的导通和截止,在不用此指令时都是截止的。在平常我们使用如:P0_1=0P0_1=1这些语句时控制的都是下面那个三极管D1。

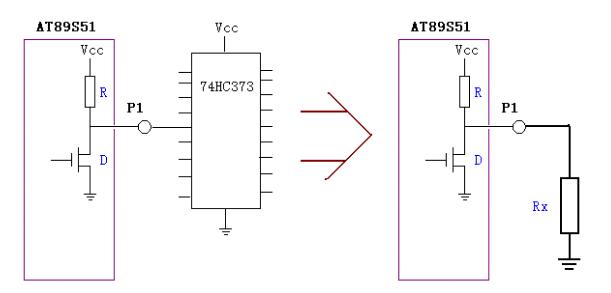

我们先假设P1口接一个74HC373,来看一看它的等效图

当AT89S51的P1口上接了74HC373后就等于接了一个负载,如上图右边。一般来说这些数字电路的输入阻抗都很大,都在几百K到上兆欧姆,而P1口内的电阻R一般在几十K以内。

如上图,当我们发出指令P1=0时,三极管D导通,见中间的等效图,这时P1点的电位为0。

当发出P1=1的指令后,三极管D截止,见右边等效图,因为Rx的阻值要比R的阻值大得多,因此P1点的电位是接近电源电压的。即高电平。

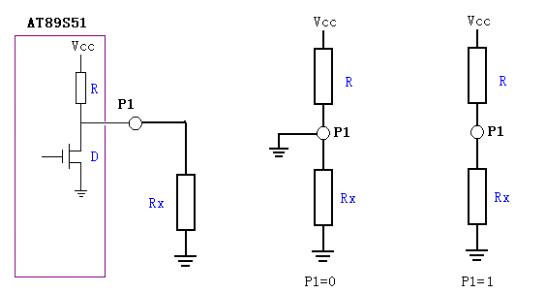

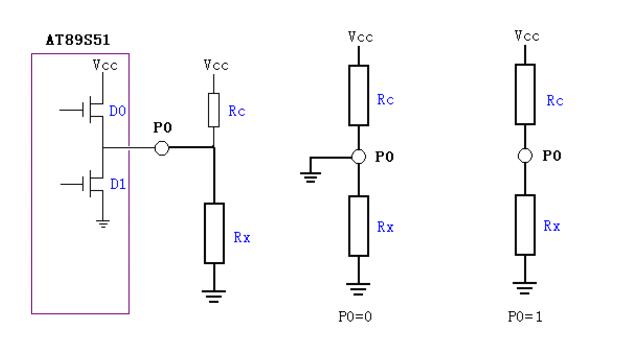

我们再来看看P0口接负载时的图

当P0=0时,等效图是中间的,三极管D1导通,P0点的电位为0。

而当P0=1时,等效图是右边的,三极管D1截止,而上面的三极管D0始终是截止的,这样P0点就等效于悬空了,它处在不稳定状态,P0点又是RX的高阻抗输入点,很容易受到外界和周围电路的干扰从而直接影响到74HC373的输出状态。因此就得加上个电阻。如下图

加上电阻Rc后,电路的状态就和P1口一样了,这个电阻Rc就是上拉电阻。

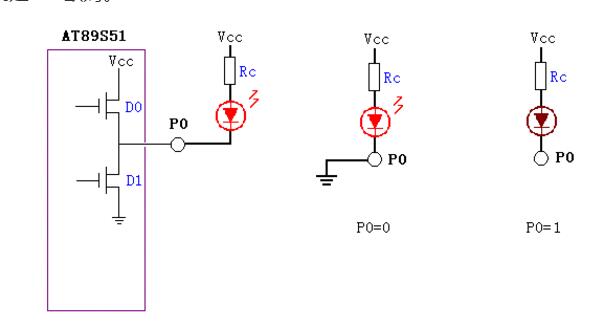

但你如果只是为了让P0口驱动个发光管,那电路可以直接简化成下图那样。S51内部的电流最好不超过15mA,如果发光管的电压为2.2V那电阻就是(5-2.2)÷15=0.18K,也就是180欧姆。

当P0=0时P0点为低电位,发光管亮起,流过D1的电流约为15mA。

当P0=1时,P0点为悬空,但发光管和180欧电阻都是低阻抗元件,P点电位就为高电位,再说也无任何输出影响,因此这样电路是可以的

-

单片机

+关注

关注

6035文章

44554浏览量

634668 -

上拉电阻

+关注

关注

5文章

359浏览量

30609

发布评论请先 登录

相关推荐

I2C总线为什么要接上拉电阻

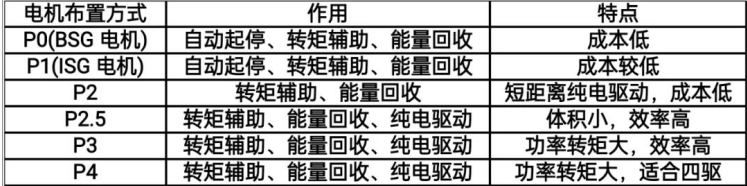

混合动力系统构型P0到P4介绍

如何计算上拉电阻的值

电路设计基础:上拉电阻、下拉电阻分析

求助,关于GPIO4和GPIO5上拉电阻问题求解

开漏输出没有外接上拉电阻,外接个LED结果能闪亮是怎么回事?

MCU电路上拉电阻、下拉电阻的概念

stm32G031串口外部不接上拉电阻,导致stm32进入到了硬件中断怎么解决?

请问H743的USB硬件连接不需要外部上拉电阻?

上拉电阻和下拉电阻是什么

p0口为什么接上拉电阻

p0口为什么接上拉电阻

评论