摘要:

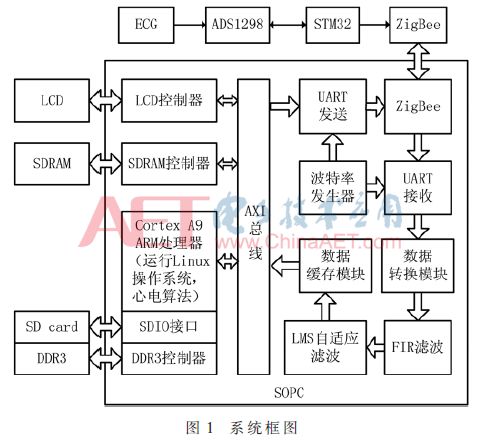

针对家用心电监护系统的需求,设计了一种基于SOPC的多导联ECG实时监测系统。系统以ADS1298为心电信号采集前端,通过ZigBee将多个导联的心电数据发送到后端处理。系统后端采用内嵌了ARM Cortex A9双核处理器的FPGA,并在ARM上搭建了

Linux开发环境。在FPGA中通过并行处理、流水线设计和自定义IP核实现对心电数据的接收、格式转换、FIR滤波、LMS自适应陷波和数据缓存;在ARM上实现了QRS检测算法、心率变异性分析和心梗检测算法,并通过SD卡和LCD屏实现心电数据的长时间存储及心电波形与诊断结果的实时显示。

目前,心血管疾病的发病率迅速上升,已经成为威胁人类身体健康的主要因素之一。常规的心电监护仪需要患者在有限时间内,到固定的医疗场所进行监护诊断,无法满足患者长期实时监护的需求,因此家用心电监护仪在人们的生活中发挥着越来越重要的作用[1]。现今,绝大多数的家用心电监护仪或是通过采集电路,将心电数据经互联网发送到医院监护中心进行远程监护[2-3],或是实现多体征参数的监护,计算心率,画出波形等[4]。这些都没有对复杂的心血管疾病进行实时分析诊断。因此本文提出了一种针对家用的、可对心血管疾病实时分析诊断的心电监测系统。

本文使用内嵌了ARM Cortex A9双核处理器的FPGA,其运算处理能力强,可实时分析处理心电数据。通过软硬件协同设计,在ARM上实现了难以硬件化的QRS检测算法,心率变异性分析和基于卷积神经网络的心梗检测算法;在FPGA中实现FIR滤波器和LMS自适应陷波及数据缓存,减轻ARM处理负担,提高数据处理效率。

基于SOPC的多导联ECG监测系统框架如图1所示,系统包括心电信号采集前端和心电数据处理后端两部分,两者之间通过ZigBee进行数据传输与控制。

2.1 心电信号采集前端

为了达到心电信号采集前端便携化的目的,使用了TI公司推出的专门针对ECG信号采集的ADS1298芯片。ADS1298内部集成了8通道24位带符号的模数转换模块,分别用来测量I、Ⅱ导联及V1~V6的6个胸导联信号[5]。根据这8个导联的信号经过一定的运算处理可得到十二导联心电信号[6]。其采样频率可在250 S/s~32 kS/s之间。

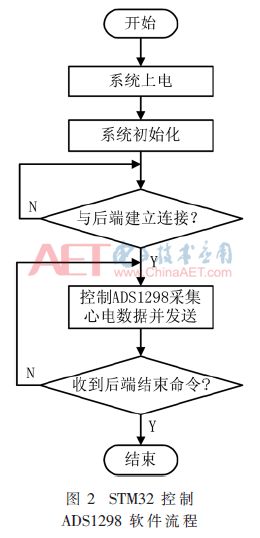

系统通过AgCl电极片拾取心电信号,ADS1298每完成一次采样转换,STM32控制ZigBee模块将所用到的导联的心电数据发送到心电数据处理后端。其软件控制流程如图2所示。

2.2 无线传输模块

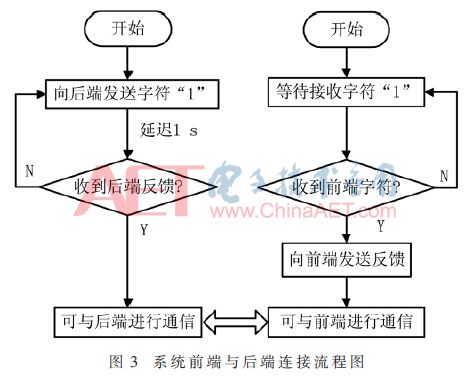

本系统使用UART接口的ZigBee模块。虽然ZigBee传输距离较短,速率慢,但由于系统AD采样速率较低,并且针对家用,传输距离限于几十米范围,再加上ZigBee功耗低,因此ZigBee满足设计要求[7]。首先系统上电后要检测前端与后端是否建立连接。图3所示为判断是否建立连接流程。

2.3 心电数据处理后端

心电数据处理后端的主要任务是通过FPGA与ARM完成对心电数据的预处理与算法处理。

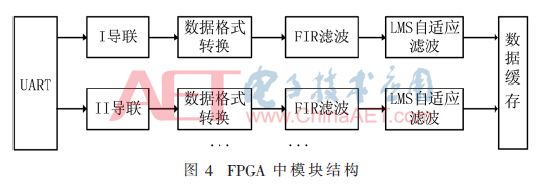

FPGA中设计结构如图4所示。用多路并行处理的方式处理心电数据,且每一路的设计遵从流水线的设计思路,提高系统处理速度,实现实时处理。

2.3.1 UART模块

为灵活接收ZigBee的数据并将数据传送到后端处理,本系统在FPGA中用Verilog采用有限状态机的方式实现了UART接口。

2.3.2 数据格式转换模块

由于FIR滤波与LMS自适应滤波均为浮点数运算,因此该模块的主要功能是将心电采集前端发送的24位整型数据转换成对应的32位浮点型数据。其结构如图5所示。

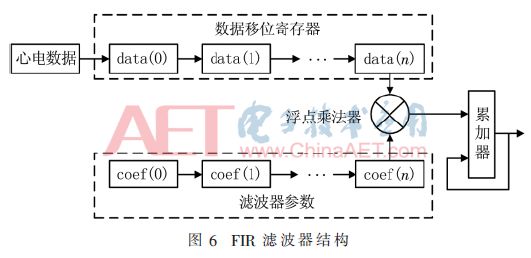

2.3.3 FIR滤波模块

从心电采集前端发送的心电数据中有由呼吸引起的基线漂移,其频率在0.5 Hz左右[8],因此设计了截止频率为0.5 Hz的FIR高通滤波器。经测试,1 000阶滤波器效果较好。

FIR滤波器本质上是卷积运算,仅涉及移位、相乘、累加运算。在MATLAB中设计得到的滤波器系数均为浮点数,因此采用Altera自带的浮点乘法器与浮点加法器IP核。考虑到滤波器的阶数为1 000阶,因此采用串行结构且只用一个浮点乘法器与浮点加法器。经计算,完成移位、1 001次乘法、1 000次加法需占用9 000个时钟周期左右。而系统时钟为50 MHz,可得该模块吞吐率可达160 kb/s。心电信号的采样率为250 Hz,所以该FIR滤波器可实时处理心电数据。图6所示为FIR滤波器的具体结构。该模块对FPGA资源占用率为2%。

2.3.4 LMS自适应滤波器

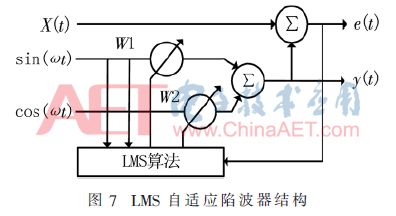

前端心电采集系统发送的心电数据中有较严重的50 Hz工频干扰,所以设计了基于LMS算法的自适应陷波器[9],抑制输入信号中的工频干扰。

基于LMS算法的自适应陷波器结构如图7所示。其中X(t)是含有干扰信号的输入信号,干扰信号频率为ω,由于干扰信号的幅值与相位未知,因此提供两个相互正交的单频信号sin(ωt)与cos(ωt),通过调整权值来合成与干扰信号相同的信号,将输入信号与合成的干扰信号作差就可得到有用信号。

LMS自适应陷波器所涉及的运算仅为乘法和加法,且都为浮点运算,为节省FPGA资源,使用一个浮点乘法器和加法器。经计算,按照此种方法,该模块的吞吐率可达16 Mb/s,可实时处理心电数据。该模块对所用FPGA资源占用率为2%。

2.3.5 基于自定义IP核的数据缓存模块

为提高ARM的处理效率,以自定义IP核形式设计了数据缓存模块将心电数据存储到片外的SDRAM中,之后由ARM读取SDRAM中的数据作算法处理。本系统ARM与FPGA之间通过AXI总线进行数据交换。

数据缓存模块的实现是基于Altera的Qsys硬件平台。在Qsys中添加SDRAM Controller,通过FPGA和ARM分别对SDRAM Controller的控制,来完成对片外SDRAM的读写。SDRAM Controller是基于Avalon总线实现的Avalon从端口。因此在FPGA中实现对SDRAM Controller的控制是通过遵循Avalon总线传输协议编写一个Avalon主端口。然后将该Avalon主端口模块例化为自定义IP核添加到Qsys中,便可实现在FPGA中对SDRAM Controller的控制。ARM则通过AXI总线完成控制。

2.3.6 ARM处理平台

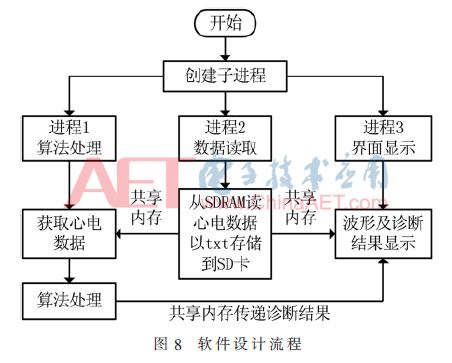

嵌入式ARM硬核为双核,且主频可达925 MHz,运算能力强,可实时处理心电数据。在ARM上构建了Linux操作系统,编程方式采用多任务编程,通过创建多个进程分别完成心电数据的读取,实现难以硬件化的心电检测算法,控制各模块之间协调工作,将心电数据以txt文件格式存储到SD卡当中,以及在LCD屏上显示心电波形和诊断结果。各进程之间通过共享内存的方式实现数据交互。图8所示为软件设计流程。

3.1 占用资源情况

系统总导联数为5导联,采样率为250 Hz。在友晶DE1-SoC开发板上运行,FPGA总资源占用情况如表1所示,占用资源在系统限度内。

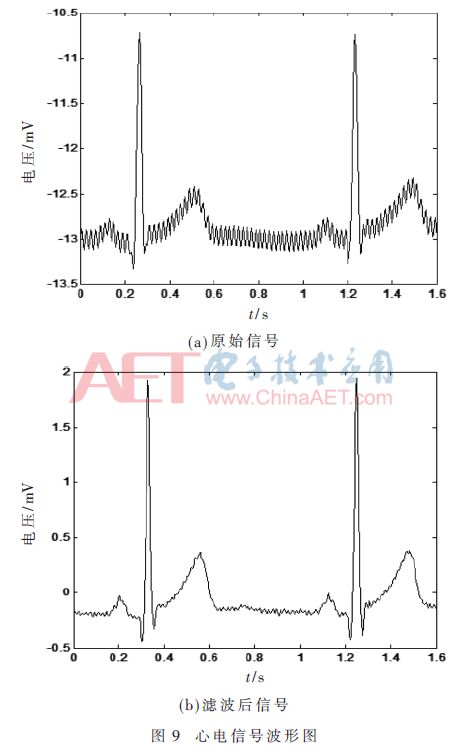

3.2 ECG信号提取测试

图9(a)是心电前端采集系统采集的原始心电信号波形,有明显的基线漂移和较大的工频干扰。图9(b)为从系统SD卡中得到的经过FPGA滤波处理的心电图,可看到基线漂移被明显滤除,且50 Hz工频得到有效抑制。

3.3 系统测试

被测者身心状况良好。图10为液晶屏的显示,可实时显示心电波形及诊断结果。图中下方左边Heart Rate显示心率为69,正常;下方中间status显示正常心电信号(Norm)或是有心肌梗死前兆,图中显示的为Norm即正常心电信号;SDNN和NN50显示心率变异性结果,其中SDNN为0.133在正常范围(0.141±0.039 s)内,NN50显示30 s内相邻心跳间期的差值超过50 ms的心跳个数,为11个。

3.4 心电算法的实现

本系统实现了课题组前期QRS检测算法[10],通过计算RR间期,可计算心率值。在此基础上本文进行了额外的心率变异性分析,从而辅助心血管疾病的预防。包含两个方面:(1)SDNN:全部心跳间期的的标准差,正常情况下该值一般在0.141±0.039 s的范围内[11]。(2)NN50:心电信号中所有每对相邻心跳间期的差值超过50 ms的心跳个数,数值越大表明心率变异性也越大[12]。

本系统也实现了课题组前期的基于V2、V3、V5、aVL导联和卷积神经网络的心梗检测算法[13],该算法可达到总体96%的准确率。通过将在PC上离线训练好的卷积神经网络移植到SOPC平台,实现对心梗疾病的诊断。

本文提出了一种基于SOPC的多导联ECG实时监测系统,可以实现对心电信号的采集和无线传输,并在SOPC平台上进行实时数字滤波、算法分析诊断以及诊断结果和心电波形的显示。实验表明,本系统可以很好地采集人体心电信号,经处理后可得到良好的心电波形,并借助ARM处理器对心电数据实时算法分析,实现心电疾病的诊断。

-

sopc

+关注

关注

2文章

248浏览量

62216 -

神经网络

+关注

关注

42文章

4776浏览量

100933 -

监测系统

+关注

关注

8文章

2739浏览量

81395

原文标题:【学术论文】基于SOPC的多导联ECG实时监测系统

文章出处:【微信号:ChinaAET,微信公众号:电子技术应用ChinaAET】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

DSP的EASI十二导联多功能Holter系统

基于ADAS1000系列的12导联ECG测量系统

心电图(ECG)设计如何防止ECG子系统受到各种外部和环境辐射影响

人体健康指标实时监测系统设计

基于SOPC的红外实时成像系统的研制

一种基于SOPC的多导联ECG实时监测系统

一种基于SOPC的多导联ECG实时监测系统

评论