ARM中有5种异常模式,有7种中断源。这7种中断源中有些中断是我们希望发生的,但有些中断是我们不希望发生的。

我们希望发生的中断:

软中断:属于svc模式,通过SWI指令便可以产生软中断,进入到svc模式。

irq中断:属于irq模式,当产生普通的外部中断时,处理器便进入到IRQ模式。

fiq中断:属于fiq模式,当产生高优先级外部中断时,处理器便进入到FIQ模式。

我们不希望发生的中断:

复位:属于svc模式,当系统上电时便会产生复位中断,系统进入到svc模式。复位中断不需要中断返回。

取指中止中断:属于abt模式,当预取指发生错误时,便产生取指中止中断,进入到abt模式。

数据中止中断:属于abt模式,当访问数据存储器时,便产生数据中止中断,进入到abt模式。

未定义指令中断:属于und模式,当执行到一条未定义指令时,便产生未定义指令中断,系统进入到und模式。

中断的优先级:

ARM中有6个优先级。各个中断的优先级顺序如下:(1 6 6s 5 2 4 3)

复位: 1

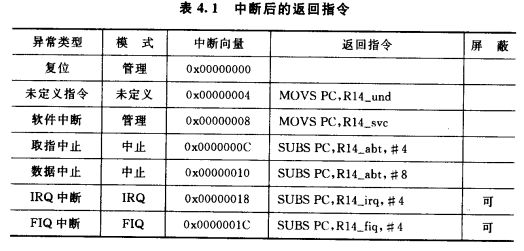

关于各种中断在中断返回时还需要给LR减去一个不同的偏移量的问题我觉得没必要深入研究了,这还要涉及到ARM指令的流水线技术,平时写中断代码都是用C写的,没必要知道这个。用到时再去查表即可。

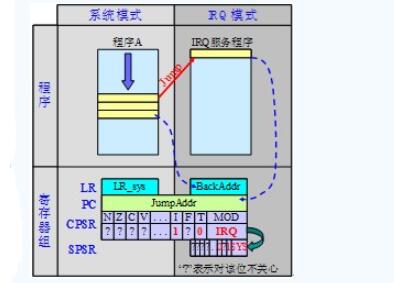

处理器在进入异常和退出异常时所做的工作:

进入异常时:

1、将要返回处的地址保存在对应异常模式的LR中。(复位不需要保存返回地址)2、将cpsr的内容复制到对应异常模式的spsr中。3、强制修改cpsr的内容,进入到相应异常模式以及根据需要修改某些位。4、强制PC从相应的中断向量地址处进行取址。

注:以上这些步骤都是有cpu自动完成的,也就是当有中断产生时,硬件就会自动完成上述步骤。

退出异常时:

1、将LR中保存的地址赋给PC。2、将spsr的内容恢复给cpsr。3、将irq中断禁止位清零。

注:只需要在异常处理程序中写一句返回指令(如上面的表4.1所示)即可全部实现上述的步骤。

-

ARM

+关注

关注

135文章

9589浏览量

393773 -

中断

+关注

关注

5文章

920浏览量

43882

原文标题:ARM中的异常和中断

文章出处:【微信号:mcu168,微信公众号:硬件攻城狮】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

简述ARM的2种工作状态和7种工作模式

ARM的2种工作状态和7种工作模式。[附带文档下载]

在SWI软中断指令中LR中放的是异常模式下的返回地址求解

ARM处理器7种工作模式

arm处理器异常模式有哪些

ARM中的5种异常模式和7种中断源

ARM中的5种异常模式和7种中断源

评论