缩减硅工艺的可怕竞争,最近又难倒了一位参赛选手。格芯今日宣布,它将无限期地暂停 7nm LP 工艺的开发,以便将资源转移到更加专业的 14nm 和 12nm FinFET 节点的持续开发上。这一突然的战略转折,发生在该公司位于纽约马耳他的 Fab 8 工厂宣称对这项前沿技术加大投资规模的几个月之后。

首席技术官 Gary Patton 在接受 AnandTech 采访时称,这一决定是出于经济方面的考虑,而非 7LP 面临的任何技术障碍。

格芯称,未来一段时间,该公司将专注于射频、嵌入式存储器、低功耗定制 14-nm 和 12-nm FinFET 工艺的定制改进。

此外,格芯还将把重点放在 22DFX 和 12FDX 工艺上,以迎合低功耗、相对低成本、以及高性能的 RF / 模拟 / 混合信号设计。

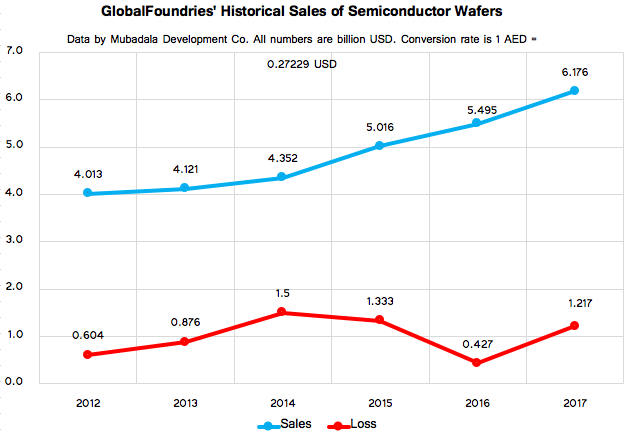

(图自:GlobalFoundries INC)

AnandTech 报道还指出,有关格芯的 5-nm 和 3-nm 节点的未来发展,也已经被搁置。

今年年底之后,该公司将停止与位于纽约奥尔巴尼的 IBM 芯片研究部门(SUNY Polytechnic Institute)的合作。

另外,格芯会裁撤 5% 的员工,其而不得不与 IBM 和 AMD 重新商谈供应协议。

对于发烧友们来说,格芯此举无疑让大家心碎一地。但问题的真相似乎是,该公司难以吸引到长期的业务,来支撑 7nm、5nm、甚至 3nm 制程所需的巨额现金。

格芯在新闻稿中指出,该公司除 AMD 和 IBM 之外的客户,更青睐于已经成熟的 14-nm FinFET 工艺,而不是需要反复经历艰难过渡的前沿节点。

万幸的是,就算没有了格芯Fab 8 工厂的支持。AMD 的下一代芯片,也不会受到太大的影响。

其首款 7-nm 产品 —— 一款面向数据中心的 Vega GPU —— 正在 GF 竞争对手台积电那边研制,同时还有代号为罗马的下一代服务器 CPU 。

总而言之,在格芯当了逃兵之后,台积电、三星和英特尔仍将继续这方面的追求。至于是否会有下一个“受害者”,仍有待时间去检验。

-

14nm

+关注

关注

2文章

135浏览量

82498 -

硅工艺

+关注

关注

0文章

5浏览量

7099 -

7nm

+关注

关注

0文章

267浏览量

35434 -

格芯

+关注

关注

2文章

236浏览量

26060 -

12nm

+关注

关注

0文章

33浏览量

8102

发布评论请先 登录

相关推荐

北京市最值得去的十家半导体芯片公司

三星重启1b nm DRAM设计,应对良率与性能挑战

创飞芯90nm BCD工艺OTP IP模块规模量产

台积电2nm工艺将量产,苹果iPhone成首批受益者

台积电产能爆棚:3nm与5nm工艺供不应求

锐成芯微推出基于8nm工艺的PVT Sensor IP

所谓的7nm芯片上没有一个图形是7nm的

台积电产能分化:6/7nm降价应对低利用率,3/5nm涨价因供不应求

传三星电子12nm级DRAM内存良率不足五成

联电携手英特尔开发12nm制程平台,预计2026年完成,2027年量产

清溢光电:已实现180nm节点掩膜版量产 佛山基地2025年末迁入设备

存内计算——助力实现28nm等效7nm功效

台积电扩增3nm产能,部分5nm产能转向该节点

2024年全球与中国7nm智能座舱芯片行业总体规模、主要企业国内外市场占有率及排名

Ethernovia推出全球首款采用7nm工艺的汽车PHY收发器系列样品

格芯成为 7nm LP 工艺开发的逃兵,专注于14/12nm FinFET 节点

格芯成为 7nm LP 工艺开发的逃兵,专注于14/12nm FinFET 节点

评论