多年来,高速信号转换系统中的模数转换器(ADC)所使用的典型流水线架构包含了取样波形所需的所有功能,这些功能被集成进同一封装中:

1. 某种形式的跟踪保持电路,可保持用于转换的信号;

2. 内置参考和偏置电流;

3. 时钟缓冲器和较小的数字电路,可将来自各级电路的比特组成无误码的数据字。

在大多数情况下,这些转换器中的可编程性仅限于通过一个休眠管脚打开/关闭转换器,或通过在双补码(two's complement)或偏移二进制码(offset binary)输出格式中选择一种格式。

系统内调整

随着ADC速度和通道密度的提高,数字输出驱动电平和终端电阻的系统内调整有助于保证高数据速率时的数字信号完整性。对具有串行低压差分信号(LVDS)输出的ADC来说更是如此。在没有输入信号的情况下,通过从ADC输出端提供一个数字激励信号,就可以在输出总线上发送练习模型。这样做可以确保多个数字组成得到正确的连接。即使是信噪比(SNR)和无杂散动态范围(SFDR)之间的性能折衷也可以通过寄存器调整实现。

目前已有一些流水线式ADC具备了增强的可编程能力,例如TI公司的ADS*5。在该器件中,4个14位、125兆样本/秒的ADC、以及用户可编程性都被集成在单一的9×9mm封装内,因此比起采用多个ADC、每个ADC包含一个转换器、整体体积更大的方案,该器件使用起来更容易。ADS*5还有许多特性可用于精确调整数字接口,以及实现SNR和SFDR之间的系统折衷。这正是系统内可编程能力存在的真正价值。

一旦定义好ADC和下游数字器件之间的链路并在板上建立起来,通过串行可编程接口(SPI)调整ADC的能力,就可以把以前要数周的调试时间缩短到5分钟。如果没有这种可编程能力,那就可能需要设计多个电路板才能解决意外的数字信号完整性或时序问题。

可调整的LVDS接口

可以通过ADS*5中的SPI调整寄存器设置中的LVDS电流等级,以优化低阻抗或互连匹配不良的差分信号完整性。这些调整可以在板子制造出来后进行。LVDS信号完整性在LVDS传输路径末端进行表征。

例如,图1就是只有5pF负载电容的一个LVDS数据输出位的示波器图形。LVDS输出驱动强度被设为3.5mA进入板上100欧姆电阻,触发频率为~375MHz。这些是正常的LVDS设置。在高速和更长距离时,LVDS信号中可能会发生反射,从而减小数据有效窗口,破坏接收器件识别正确转换信号的能力。这种信号完整性问题正在图1中发生。

图1:LVDS的电容负载5pF,以额定的3.5mA进入板上接收端100欧姆的电阻。

有几种方法可以解决这个问题,它们除了访问ADC的SPI外没有其他任何要求。你可以将LVDS输出电路中的内部负载电阻作为源负载来终结传输线。这会在LVDS输出端形成一个50欧姆的负载(两个100欧姆电阻并联)。因此,额定的3.5mA电流形成的信号幅度是700mVpp额定输出电压的一半。

更低的差分信号电平本身会导致与上述劣化信号同样多的检测错误,但只要LVDS接收器具备必要的灵敏度,那么对许多系统来说就没有问题。

如果要求更高的LVDS摆幅,可以设置ADS*5让LVDS输出电流翻倍到7mA(图2),从而使信号回到700mVpp。电容负载也从5pF(图1)提高到10pF(图2),进一步彰显了额外电流和双倍终端信号的好处。在图2中,所有转化现在都没有反射能量。

图2:LVDS的电容负载10pF,以的7mA进入板上接收端50欧姆的电阻。

就像驱动能力可以根据要求增加一样,在LVDS信号完整性允许的条件下,也可以降低驱动能力以便节省功耗。为了节省功率,如果满幅700mVpp没必要的话,或者距离可能很短、ADC和数字器件之间的负载也很小,那么就可以改变LVDS输出电流和负载电阻。

根据不同的期望结果,这样做有几大好处。在信号速率不是特别高、电容负载又低的情况下,可以使用低于3.5mA标准的几种电流设置之一、以及大于100欧姆的内部负载电阻(甚至无需额外的负载电阻,进而节省费用和空间),这样仍能建立可靠的链接。

在信号完整性允许的情况下,一种节省功耗的方法是选用142欧姆的内部LVDS差分负载和2.5mA的LVDS电流。在这种组合设置下仍能达到约700mVpp。通常,在条件有保证的情况下,建议为LVDS路径末端的差分终端电阻提供一块空间。对于短路径来说可能没有必要,ADC里的内部源端的终端电阻已经足够。

LVDS规范允许LVDS源的差分输出处于247到454mV峰值范围内的任一点。其他组合也可能用于增加或减少仍处于TIA/EIA/ANSI-* LVDS规范内的LVDS驱动强度和电压电平。你可以从系统概念开始就选择这些特性以便节省功率。另外,它们也可以在LVDS信号完整性问题被意外发现时仅用作保障措施。

这些特性可以在发生问题时节省大量板级调试的时间和费用。要看清楚LVDS接收器件要求的电压值。因为每块板都是不同的,你可能需要对ADC编程以便调整LVDS输出电平。这可以在电路板信号丢失被表征和考虑后,在LVDS接收端来维持允许的范围。

内置测试模型

ADS*5提供了多种内置的测试模型,可以在没有模拟输入源的时候使用。这些模型可以在初始电路板调试时用来考察ADC和FPGA之间的时序关系,以便确定FPGA接口处正确的时钟与数据关系。这能确保有良好的时序(时序通常可以在FPGA LVDS输入信号中调整)。

与提供模拟信号相比,使用内置练习模型的一个好处是模型具有一致性,因此可以排除模拟源带来的任何误差问题,使实验具有可重复性,也更容易建立。练习模型也可以在电路板制造与测试过程中用作电路板功能测试的一部分。

信号增益、SNR和SFDR

可编程性不仅仅能解决板级互连问题,一些特性还可以用来实现系统性能折衷。举例来说,ADS*5也有内部模拟输入信号增益功能,允许牺牲SNR来提高SFDR,或只是降低模拟输入幅度。

ADS*5既有粗略增益调整也有精细增益调整。在这两种情况下,模拟输入电压值必须至少要减去ADC中所选取的增益值。这样可以保持ADC的输入电压范围,避免让数字输出字饱和或削减。因此,如果你想使用ADC中的增益设置进行开发,最好要在ADC之前的模拟电路中就计划减少板级模拟输入信号的电平。

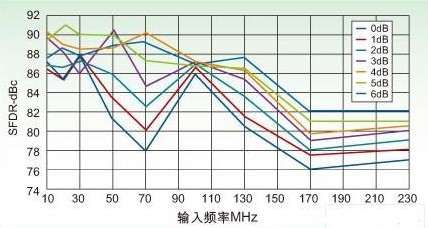

从图3和图4可以看出,折衷在输入信号电平和使用两种不同增益调整方法导致的失真(或这里特指的SFDR)之间是显而易见的。这个特性可用来获得多重对象。对于能利用数字抽取技术恢复SNR的窄带系统来说,根据涉及的输入频率,可以通过降低转换器中的SNR来改善SFDR。

图3:使用精细增益控制时SFDR与输入频率的对比。

图4:使用粗略增益控制时SFDR与输入频率的对比

另外,通过允许更小的输入信号进入ADC,同时仍保持来自ADC的全刻度代码,驱动ADC的模拟电路就可能改善失真,并为放大器和ADC整合电路创建更好的SFDR。

可以在创建原型的阶段就使用这个特性,以便确定输入信号电平的最佳组合,从而无需设计多块电路板就能取得最佳的系统失真。可以在系统中动态地进行增益调整,并一道使用自动增益控制(AGC)来恢复尽可能多的动态范围。还可以通过一个封装引脚实现粗略的3.5dB增益设置,以便用于那些没有SPI但想要调整ADC增益的应用,附加的内部寄存器子集也是如此。

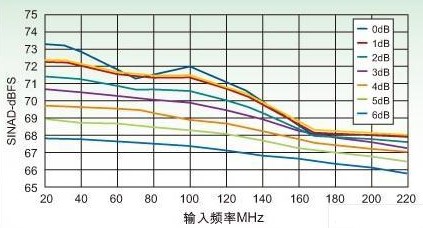

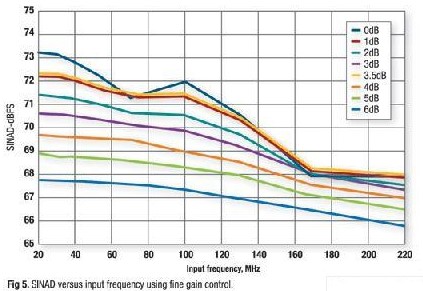

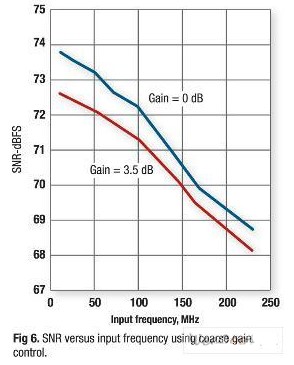

图5和图6给出了信号-噪声及失真比(SINAD),以及与A/D转换器的内部增益设置有关的SNR减少的情况。

图5:使用精细增益控制时SINAD与输入频率的对比

图6:使用粗略增益控制时SNR与输入频率的对比

由于高速A/D转换器的可编程性越来越强,它们对用户的友好程度也越来越高。对那些厌烦SPI方法或编程的传统模拟硬件设计师来说,该ADC仍可以使用默认的设置,直接简单的忽略掉其可编程特性。

高速ADC是模拟和数字硬件之间的桥梁,它经常由全数字或全模拟硬件设计师负责。此时,数字硬件设计师更容易接受其可编程特性,但它也可以帮助那些无法正确建立数字时序或信号完整性的模拟硬件设计师节省宝贵的时间。

-

转换器

+关注

关注

27文章

8755浏览量

148301 -

缓冲器

+关注

关注

6文章

1974浏览量

45706 -

adc

+关注

关注

99文章

6538浏览量

546034

发布评论请先 登录

相关推荐

可编程交流负载标准

什么是可编程逻辑

时钟的重要性

高速可编程遥感卫星数据模拟源的设计与实现

可编程SoC(SoPC),什么是可编程SoC(SoPC)

LabVIEW可编程FPGA模块对示波器的重要性

实现重要分析与硬件加速的可编程Xilinx zynq-7000平台推荐

可编程电源的原理 可编程电源的优缺点

可编程三相交流电源重要性和优势

可编程单相交流电源的重要性及优势

可编程电源如何编程

用TMAG5328电阻器和电压可编程霍尔效应开关实现可编程性和诊断

高速ADC的可编程特性的重要性

高速ADC的可编程特性的重要性

评论