1 引言

锁相环(PLL)是模拟电路中的一个重要模块,本文研究的是广泛使用的电荷泵型锁相环(CPPLL)。锁相环电路通过比较参考输入和输出反馈信号的频率/相位,并将此特征转化为电压,然后通过与压控振荡器(VCO)的配合来调整输出信号的频率,最后使得锁相环的参考输入和输出反馈信号的频率相等、相位恒定,从而锁定输出信号的频率。电荷泵型锁相环更是具有稳定性高、捕捉范围大等诸多优点。

本文所研究的,就是在不影响锁相环功能的同时,通过添加尽可能简单而又有效的辅助电路,来有效减少PLL系统的锁定时间,并给出了在0.6μm工艺下的设计实例。通过Spectre仿真验证,结果表明,改进效果是有效且显着的。

2 鉴频鉴相器及电荷泵电路

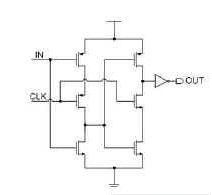

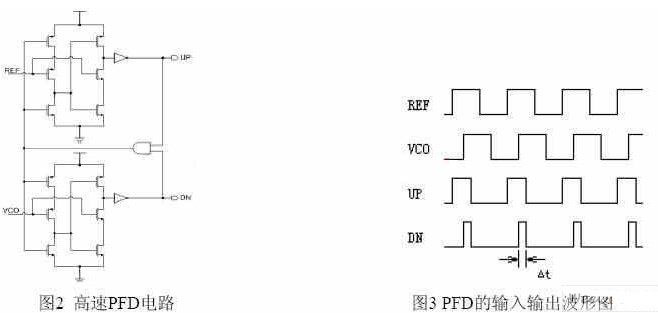

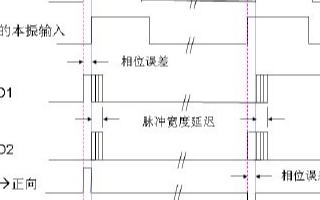

首先我们介绍在鉴频鉴相器中使用的TSPC锁存器,如图1。TSPC锁存器的主要优点是速度快,延时小,而且需要的MOS管数目也比传统的锁存器少。利用上述TSPC的控制功能及性能,我们可以得到使用广泛的鉴频鉴相器,如图2所示。此鉴频鉴相器实现的功能如图3所示(以参考输入REF相位超前为例)。为了消除死区,在DN信号端有一个宽度为△t的周期性短脉宽重叠信号。利用得到的这对信号控制电荷泵电容的充放电,就可以调整电压Vctrl的值,最终实现对VCO[4]输出频率的调节。

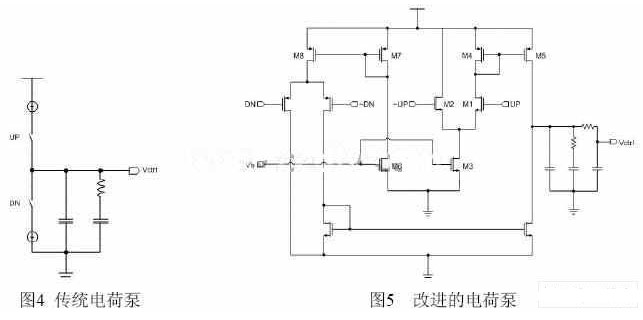

3 对电荷泵的改进

传统的PFD/CP,如图4所示,电荷泵电流是固定的,通过开关控制对电荷泵电容的充放电。这个固定电流一般不是很大,当在Vctrl需要大的电压跃变,比如输入参考频率发生比较大的跃迁,此时调整Vctrl到所需值就需要很长的时间,这将极大地影响锁相环的性能。许多文章对此进行了改进,就是加入第二组电荷泵,使得在系统非锁定时能够提供大电流以实现快速充放电,减少锁定时间。本文对电荷泵的改进,是在不增加多余电流通路的情况下,通过适时的、周期的改变电荷泵电流,最终达到缩短输出频率调整时间的目的。

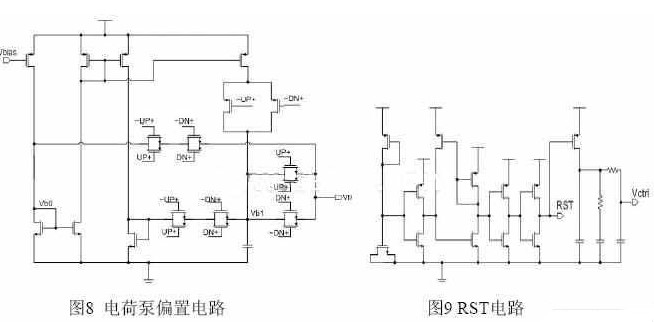

我们对传统电荷泵进行了改进,其结构如图5所示。Vb为偏置电压。UP、DN为鉴频鉴相器(PFD)的输出,-UP、-DN分别对应UP、DN的取反值,这四个控制电压共同完成对电荷泵电流的控制。当UP为高电平时,M1导通,M2关断,M3的电流全部流过M1,该电流通过电流镜完成对电荷泵电容的充电,反之M3的电流全部流过M2,电荷泵充电电流为零。DN的控制也是如此(图中M3和M6,M7和M8分别是1:1的镜像关系,以保证充放电电流大小一致)。如果能够控制偏置电压Vb,亦可控制两个尾电流的大小,进而控制充放电电流的大小,使得缩短PLL的锁定时间变为可能。

我们采用电压切换的方法来控制偏置电压Vb。在参考输入信号与输出反馈信号频率/相位相差不大时Vb偏置到Vb0(固定电压),得到一个恒定的电荷泵电流,这有助于对电荷泵电路进行精确的设计;当相差比较大的时候Vb偏置到Vb1(变化电压),并且Vb1的最小值大于Vb0,目的是为了使Vb在任何时候切换到Vb1,都能产生更大的尾电流。

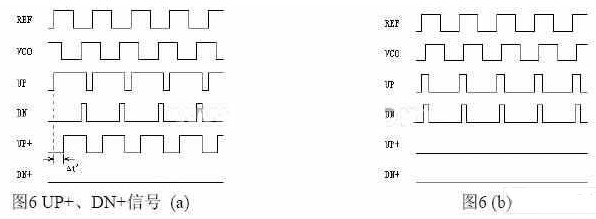

Vb在Vb0、Vb1之间的切换遵循图6所示的原则。当UP信号持续较长时间高电平,以参考输入信号相位超前输出反馈信号为例,如图6(a),我们希望能够得到如图中UP+和DN+这样一对控制信号:当UP信号的宽度超过△t’时,UP+在UP上跳沿延时△t’时刻变为高电平,在UP下降沿变为低电平,DN+则一直保持低电平。在这对UP+、DN+信号起作用时,切换偏置电压Vb到Vb1;如果UP信号的宽度小于时间长度△t’,如图6(b),则UP+、DN+均为低电平,Vb偏置在Vb0,完成恒定电流充电过程。

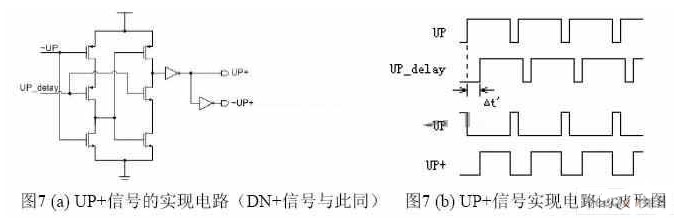

UP+、DN+信号的实现电路如图7(a)所示(以UP+信号为例)。通过简单的使用TSPC锁存器就得到了UP+信号,其信号波形如图7(b)。-UP信号为锁存器的输入;UP信号延时△t’得到的UP_delay信号作为TSPC锁存器的时钟信号。同理可得DN+信号。但需要注意的是,延时△t’必须大于重叠脉冲的宽度△t,避免在重叠脉冲期间产生一个短脉冲信号。

需要注意的是,一旦偏置电容充电达到一定值,就只能靠漏电来完成降压,而这个过程十分缓慢,那么当参考输入与输出反馈信号的频率/相位相差不大时,就会导致偏置电压Vb过大,因而需要动态调整偏置电容的端电压。我们的解决方案是,通过开关将偏置电容与一个流过固定电流的二极管连接的MOS管相接,在UP+、DN+均为低电平时,偏置电容放电,随着低电平时间的长短不同,偏置电容的端电压也将对应不同的值。完整的电路如图8所示。

4 系统启动优化

系统启动优化是为了缩短PLL系统从上电启动到输出稳定频率的时间。

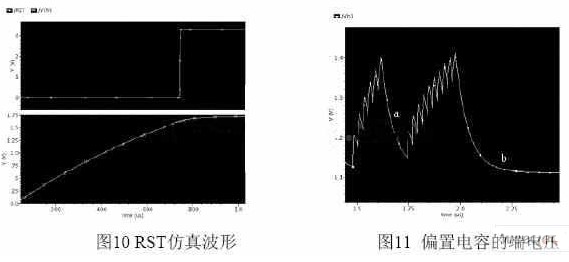

改进的原理,是在上电瞬间产生一个从低电平到高电平跃迁的RST信号,以控制对电荷泵电容的充电,使其在极短的时间内上升到Vctrl_init,我们设定,在Vctrl_init电压下,VCO输出信号频率为整个频率调整范围内的中间值。

电路如图9所示。RST信号控制一个PMOS管,在上电初期,对电荷泵电容进行大电流充电。仿真结果如图10所示,电荷泵电容的端电压Vctrl在750ns时上升到1.7v。

5 仿真结果

综合以上两种改进,我们设计了PLL整体电路并进行了系统仿真。

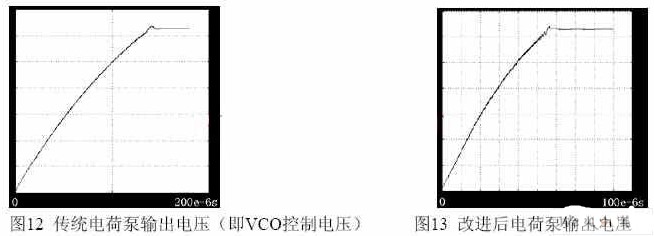

图11是偏置电容端电压的波形,图中尖锐的上升沿表示UP+或DN+信号打开开关对偏置电容进行充电;短时间尖锐的下降沿表示UP+或DN+信号自身高电平间短暂的时间间隔;a处平滑的下降沿表示UP+或DN+信号的间隔比较大;b处的下降沿最后趋于平整,表示进入了恒定电荷泵电流调节的模式。由此可见,偏置电路很好地实现了对偏置电容端电压的调整。

在参考频率为25MHz的情况下,电荷泵改进前、后PLL的锁定时间如图12、图13所示,改进后锁相环的锁定时间减少为改进前的1/2,而且稳定时的振铃也更为平坦。

5 结论

与构造两个电荷泵来实现快速充放电的方式相比,本文所用的连续控制电荷泵电流的方式,对Vctrl的调节更加合理,并且减少了MOS管数目,降低了功耗,在添加启动优化的电路后,通过在极短时间内提升Vctrl电压的方式,使得锁定时间的大大减少。

-

振荡器

+关注

关注

28文章

4194浏览量

143186 -

pll

+关注

关注

6文章

991浏览量

138394 -

锁存器

+关注

关注

8文章

958浏览量

45478

发布评论请先 登录

电荷泵锁相环电路锁定检测的基本原理,影响锁相环数字锁定电路的关键因子是什么?

锁相环控制频率的原理

模拟锁相环,模拟锁相环原理解析

电荷泵锁相环的数字锁定检测电路应用分析

详解FPGA数字锁相环平台

基于电荷泵锁相环技术的电路锁定检测的基本原理和设计实现

利用开关的控制加速锁相环锁定的设计方法

利用开关的控制加速锁相环锁定的设计方法

评论