0 引言

流水线模数转换器(pipeline ADC)是中高精度(10~14 bit)高速(10~500 MS/s)ADC的主流实现结构,被广泛应用于通信系统、图像设备、视频处理等系统中。作为其前端最关键的模块,采样保持电路的性能直接决定了整个ADC的性能,在以上系统中对功耗的要求十分严格。本设计在实现高速高精度采样保持功能的同时,还实现了MDAC功能,这样既能降低ADC功耗又能减少芯片面积。

1 采样保持电路结构

传统流水线ADC的最前面为一级采样保持电路其后接MDAC级。采样保持电路能够较好地减小由于MDAC和子ADC之间的采样信号失配造成的孔径误差。由于采保电路位于整个ADC的最前端,对其精度要求最高,故该模块需要消耗较大的功耗通常为整个ADC功耗的20%~30%,并且会降低ADC的动态范围和线性度。流水ADC是在双向非交叠时钟的控制下工作,相邻的采样保持电路和第一级MDAC总是工作在不同的状态,采样或保持。每个模块只是在保持状态需要运放参与工作。这样采样保持和第一级MDAC可以分时复用同一个运放,达到降低功耗并减少面积的目的。

基于以下原因MDAC级选择了1.5 bit/级。首先,每级有1 bit冗余位来进行数字冗余修正,大大减小比较器失调造成的影响;其次,1.5 bit/级结构的单级闭环增益为2,开关电容电路可以具有较小的负载电容和较大反馈因子,较小的单级分辨率可以获得较高的速度。

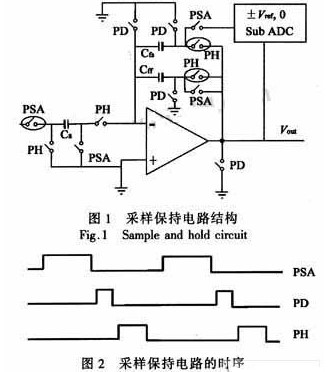

图1为本设计的采样保持电路结构,图2为其时序,加圈处为自举开关。采样保持电路在3相时钟的控制下,工作于3种不同的状态,采样/放大、复位、保持。

具体工作原理如下:当PSA为高电平时电路工作于采样/放大状态,输入信号被采样至电容Cs上

Ql=Vin·Cs (1)

运算放大器和电容Cff,Cfs及子ADC构成MDAC结构,处于保持状态;当PD为高电平时电路工作于复位状态,Cs完成对输入信号的采样,输入电荷存于Cs上。运放及Cff,Cfs处于复位状态,运放输入端短接,输出端短接,电容两端短接,消除电路的记忆效应,为下一状态做准备。当PH为高电平时电路处于保持状态,运算放大器呈ChargeTransferring型采保连接形式,输出电平与采样电平值接近,输人电荷转移到Cff,Cfs上

Q2=Q1 (2)

取Cff=Cfs=0.5 Cs,运放的输出进入子ADC;当PSA为高电平时,Cfr跨接在运放两端,Cfs与DAC的输出模拟电平相连,电路呈现减法放大功能

Q3=Vout·Cff+Vdac(D)·Cfs (3)

由于PH和PSA两个相位运算放大器的输入始终处于虚地状态,根据电荷守恒Q2=Q3,得到当Cff=Cfs时,就实现了1.5 bit/级MDAC的减法、放大功能。

与传统的采样保持电路相比,新型结构的优势在于:在一个时钟周期内,单级模块在实现采样保持功能的同时,还实现了一级MDAC功能;电容Cff,Cfs在保持相和减法放大相实现了复用,降低了功耗和面积;同一运放分时复用于保持相和减法放大相,降低了功耗和面积;与无采保结构的ADC相比,由于保持相的存在,消除了运放与比较器输入端信号路径延时不等的影响,在降低功耗的同时,动态性能没有下降。

使用这种结构需要注意的几个问题:①精度问题。由于PD相的存在,在本设计中PH的时间由传统的两相非交叠11.2 ns缩短为8.4 ns,保持相时间内运放是否能建立到要求的精度范围。因为电容Cff,Cfs在PSA和PH相的复用减少了PH相时运放所带的负载,在1.5 bit结构中运放的负载为

Cload=(1-β)Cfn+Csn+1 (5)

式中:β为反馈系数,缩减因子取为0.5;Cload=1.5Cfn。新结构中

Cload=(1-β)Cfn=0.5 Cfn (6)

负载减少了60%,时间只缩短了25%,所以可建立到指定精度。因该阶段把采样的电荷转移到了Cff,Cfs,发生了一次运算,故输出需达到12 bit的精度,输出端误差应满足ε≤1/212。②功耗问题。由于负载减少的程度大于建立时间减少的程度,所以并不需要增加单个运放的功耗。③稳定性问题。在PH和PSA相时,运放需要工作在两个不同的反馈环路中,对于本设计选择的1.5 bit/级结构,每个环路中运放的反馈系数都为0.5,所以两个状态电路电路都容易达到稳定。当把本结构推广到每级2.5 bit或以上结构时,在PSA相的反馈系数将小于0.5,运放的带宽和极点位置就需仔细考虑,以确保电路的每个状态都是稳定的。

2 改进的自举开关设计

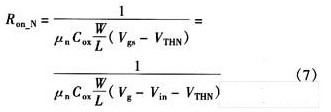

在模数转换器的设计中,由于模拟信号是先通过采样开关,再进人ADC转换电路的,因此,采样保持电路中接输入模拟信号的采样开关的设计也十分重要。NMOS管的导通电阻可用式(7)表示,其大小与栅源电压成反比。在低电压电路中利用电荷泵提高时钟电压,可以减小电阻,但却不能消除由于输入电压变化而引起的非线性失真。当栅源电压超过电源电压时,会导致器件可靠性不高。

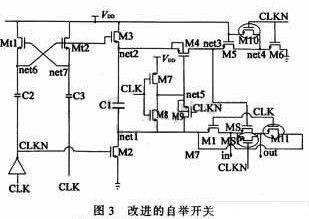

为了减少主要来自于开关的导通电阻、寄生电容和沟道注入电荷与输入信号的相关性引起的非线性失真,设计的采样保持电路采用了改进的栅压自举开关,如图3所示,在传统的自举开关的基础上增加了M10,M11,MSP三个MOS管。自举开关用在图1加圈的开关处。

电路第一个改进是增加M11。MS左右两边并不对称,当开关闭合时in和out两边泄漏的电荷并不相等,会影响采样电容上的电荷。通过增加M11令其尺寸和Ml相同,改为对称结构如图所示可以解决这一问题。并且让M1和M11的栅直接由CLK信号控制而不是像传统结构中那样与MS的栅相连,这使得他们比MS稍微提前一点关断,会减少MS释放的电荷数量,提高采样的精度。增加M11带来的另一个好处是提高了MS的可靠性。若没有M11,在MS导通瞬间必须确保其漏端电压比源端电压高,使栅漏之间的电压不大于VDD。增加M11后,电路变为对称结构,源漏电压相等,电路在满幅度工作时,栅源栅漏电压都不会大于VDD提高了可靠性。

电路第二个改进是增加M10。在传统自举开关中,M5和M6的作用是在CLKN为高时,给MS的栅电容提供一条放电的通路。M5是为了提高M6的可靠性而增加的器件,CLKN为高时可以减少M6的Vds和Vgs。在CLK相M5管处于导通状态,M6管处于截止状态,并且net3电压很高为(VDD+Vin),因此沿M5和M6存在着电荷泄漏通路,影响MS的Vgs,导致噪声。因此本设计对其做了改进,增加M10管,使得在CLK为高时,M5管处于可靠的关闭状态。这样带来了两点好处:第一是有效地减小了泄漏电流;第二是通过在CLK为高时关闭M7管,减小了M7的电容,从而减小了与C1相关的寄生电容,使MS能得到更高的Vgs,提高信噪比。

电路的第三个改进是增加了MSP管。MS的导通电阻,会受到体效应的影响而变化,影响采样的精度。并联尺寸很小的MSP管可以很明显地减小导通电阻,减少输入信号和体效应对其的影响,同时可以提高整个电路的线性度。采用改进结构后自举开关在线性方面与传统结构相比有8 dB的提高,后仿结果SFDR为86.83 dB,SNDR为75.229 dB,符合12 bit要求。

3 运算放大器的设计

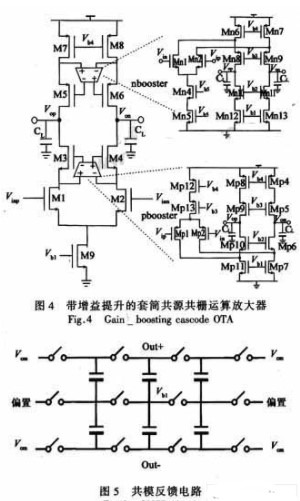

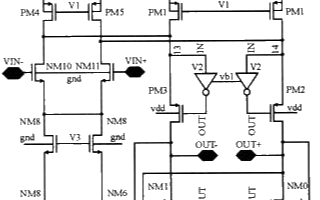

运算放大器是本设计的最核心部分。运算放大器采用带增益提升的套筒式共源共栅结构,这是由于所需增益比较大(大于80 dB),单级放大器达不到所需的增益,而采用两级结构会出现相位的补偿问题,并且功耗也比较大,所以本设计选择带增益提升的套筒共源共栅运算放大器如图4。由于本设计的运放在两个时钟状态下都要工作,其开关共模反馈结构如图5所示。整个ADC的设计要求信号输出摆幅为2 V,套筒共源共栅运放也完全可以满足要求。

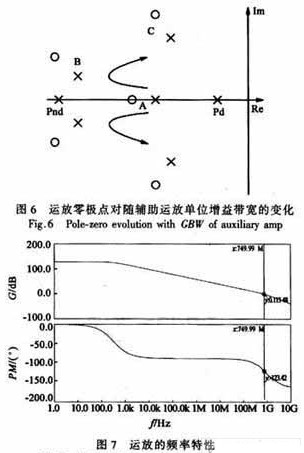

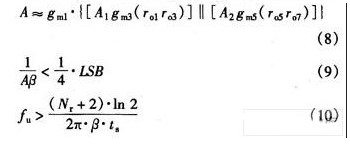

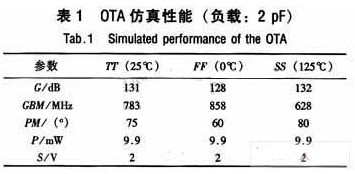

pbooster和nbooster分别为增益增强的辅助运放,采用折叠式共源共栅结构,增益增强技术引入辅助放大器极大地提高了主放大器的增益如公式(8)所示,但是它也在放大器的传输函数中引入了一对零极点对(pole zero doublet),它会影响放大器的时域响应,在跨导运算放大器的设计过程中,使用Matlab分析发现运放的极点随辅助运放带宽的增加,会由A到B到C变化如图6所示,仔细优化两个辅助运算放大器的单位增益带宽,把运放的极点推向较高的频率如图所示,可以减小增益自举运算放大器中零极点对对大信号阶跃响应的影响,使电路达到较快的稳定。对于12 bit 40 MS/s的要求,由公式(9)和(10)计算并留有一定的预度,运放需要84 dB增益、300 MHz的带宽。公式(9)中A为放大倍数,β为反馈系数。公式(10)中fu为单位增益带宽;Nr为有效位数;ts为半个时钟周期。负载为2 pF时,运放的整个频率响应如图7所示,直流增益为131 dB,单位增益带宽为783 MHz,相位裕度为75°,符合12 bit 40 MS/s的要求。

不同工艺转角TT,FF,SS和温度下,运放性能如表1所示。表中:G为增益;GBW为增益带宽;PM为相位裕度;P为功耗;S为摆幅。

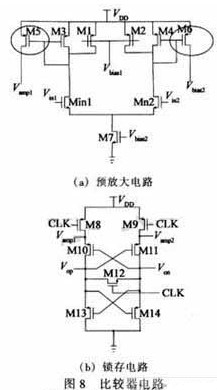

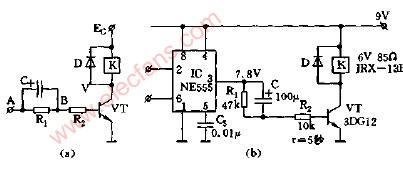

4 比较器

由于本设计要达到12 bit的精度要求,为了能够抑制回程干扰,在锁存器前面加了一级预放大器。为了消除预放大器自身的失调电压,可在比较器的锁存阶段将预放大器接成单位增益负反馈的形式,达到失调消除的目的。蒙特卡罗分析表明,该比较器输入失调电压10 mV,满足小于1/4 Vref,250 mV的失调范围要求。比较器电路如图8所示。

5 仿真结果

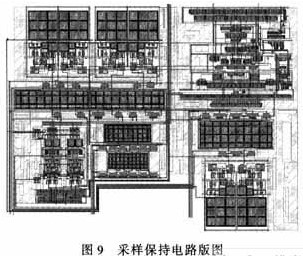

本设计的采样保持电路采用TSMC 0.35μmCMOS标准工艺设计。使用Cadence和HSPICE进行仿真验证,电路在0~125℃内,在各种Comer下均能正常工作。电路在40 MHz采样频率工作时功耗仅为14 mW。电路的版图如图9所示。

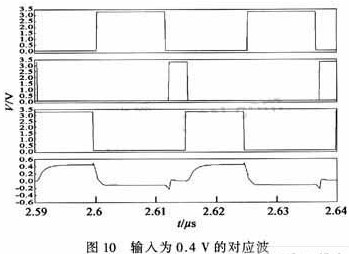

图10为在输入为直流0.4 V时,SMDAC模块的输出及所对应的时序,在PH相时输出应为0.6 V,PD相时输出应为0 V,PSA相时输出应为

Vout=2×Vin-Vdac(D)=2×0.6-1=0.2 V,输出值与计算值一致,验证了电路功能的正确性。

在采样频率为40 MHz,输入信号为19 MHz的满幅度正弦信号(Vpp=2 V)对电路进行后仿真。对所得的输出信号进行1024点快速傅里叶变换的频谱如图11所示,SNDR=73.22 dB,ENOB=11.87 bit,SFDR=89.34 dB。

6 结论

本文采用TSMC 0.35μm mix signal 3.3 V工艺没计了一个高性能低功耗的采样保持电路,可作为12 bit 40 MHz采样频率的流水线A/D转换器的前端模块。通过对运放的分时复用,一个电路模块既实现了采样保持功能,又实现了MDAC功能。而实现该指标的MDAC所需功耗为9 mW,与普通结构相比在达到同样指标的情况下,可减少了9 mW。通过对传统栅压自举开关改进,减少电路的非线性失真。通过优化辅助运放的宽带,设计了高增益快速稳定的OTA。在40 MHz采样频率下,以奈奎斯特采样频率满幅(Vpp=2 V)信号输入,其SFDR=85 dB,SNDR=72 dB,ENOB=11.6 bit。整个电路消耗的动态功耗为14 Mw。

-

运算放大器

+关注

关注

215文章

5037浏览量

174016 -

adc

+关注

关注

99文章

6565浏览量

546605 -

低功耗

+关注

关注

10文章

2432浏览量

104027

发布评论请先 登录

相关推荐

汽车ECU的低功耗高性能实现

一种基于视频处理系统的12位25MS/s低功耗采样保持电路介绍

基于ZU3EG的低功耗高性能嵌入式AI高性能计算模组

低功耗ADC实现高性能明智设计

在16位、100kSPS数据采集系统中实现低功耗和高性能

采用全差分结构的高性能采样/保持电路的设计

AD9251集成高性能采样保持电路和片内电压基准出

高性能低功耗的采样保持电路的设计与实现

高性能低功耗的采样保持电路的设计与实现

评论