Ku 波段频率合成器主要功能是提供具有一定隔离度的两路相参2 cm 波段的输出频率,经系统倍频后作为发射机的发射信号和接收机的本振信号。如何使Ku 波段频率合成器具有高频率稳定度、低相位噪声、低杂散、小体积以及高隔离度等特性,是当今设计人员主要的研究方向。

1、主要技术指标

( 1) 晶振频率: ( 略) 。

( 2) 输出射频频率: 本振信号,频率2 cm 波段; 发射信号,频率f R = f L - f I ( 检测信号频率同发射信号频率) 。

( 3) 本振信号和发射信号的单边带相位噪声: 小于等于- 96 dBc/ Hz@10~ 500 kHz。

( 4) 本振信号和发射信号无用频率分量: 小于等于- 70 dBc。

( 5) 隔离: 本振电路对发射信号的隔离大于等于105 dB; 发射电路对本振信号的隔离大于等于90 dB。

( 6) 发射电路预调制: 开关通断比大于等于85 dB。

2、主要技术途径

2. 1 频率合成的类型

通常频率合成器可以被分成直接式频率合成器、直接数字式频率合成器及锁相式频率合成器三种类型,其中最后一种频率合成器也被称为间接式频率合成器。很多情况下,频率合成器是由多种类型相结合形成的。

2. 1. 1 直接式频率合成器

直接模拟频率合成器是最先出现的一种合成器类型的频率信号源。这种频率合成器原理简单,易于实现。其合成方法大致可分为两种类型: 一种是所谓的非相关合成方法; 另一种是所谓相关合成方法。这两种合成方法之间的主要区别是所使用的参考频率源的数目不同而已。

直接式频率合成器的显着特点是: 分辨率高; 频率转换速度快( 小于100us) ; 工作稳定可靠; 输出信号频谱纯度高。缺点就是使用的元件太多,很难集成,而且功耗较大,很难用于移动通信中。

2. 1. 2 锁相式频率合成器

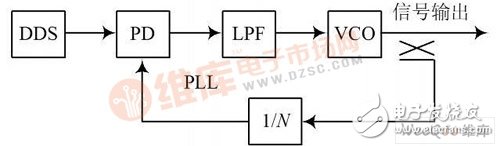

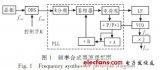

锁相环路( Phase Lo cked Loo p) 是一个闭环的相位控制系统,它的输出信号的相位能自动跟踪输入信号相位。锁相环路之所以能够进入相位跟踪,实现输出与输入信号的同步,是因为它是一个相位的负反馈控制系统。它由三个基本部件组成,分别是鉴相器( PD) 、环路滤波器( LPF) 和压控振荡器( VCO) 。其原理框图如图1 所示。

2. 1. 3 直接数字式频率合成器

直接数字式频率合成( Direct Digital FrequencySynthesis,DDS) 是近年来发展起来的一种新的频率合成技术。它将先进的数字处理理论与方法引入信号合成领域,标志着第三代频率合成技术的出现。其主要优点是相对带宽很宽,频率转换时间极短( 可小于20 ns) ,频率分辨率很高( 典型值为0. 001 Hz) ,全数字化结构便于集成,输出相位连续,频率、相位和幅度均可实现程控。因此,能够与计算机紧密结合在一起,充分发挥软件的作用。DDS 技术的实现完全是高速数字电路D/ A变换器*的产物。由于集成电路速度的限制,目前DDS 的上限频率还不能做得很高。但GaAs( 砷化镓) 材料在集成电路中的应用,使得DDS 上限频率不够高的缺陷正在不断地被克服。

2. 2 DDS+ PLL 方案的简单介绍

因为PLL 具有高频率、宽频带、频谱纯度好的优点,但其频率切换速度低,只能达到??s 级,而DDS 具备高速频率捷变能力( 可达到10 ns 级) ,相位分辨能力强,只要将二者相结合,可产生高精度,高速切换频率的频率合成器。现在的DDS+ PLL 混合频率合成技术主要有以下三种比较成熟的方案,并在工程研制中得到应用。

2. 2. 1 DDS 激励PLL 方案

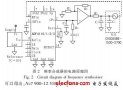

DDS 激励PLL 是最简单和最直接的组合方案,PLL 设计成N 倍频环,DDS 作为PLL 的参考信号,如图2 所示。输出信号的频率分辨率为N ?? ( DDS 的频率分辨率) ,DDS 在环路带宽以内的杂散将带入信号,且恶化20lo g N dB,频率变换时间取决于PLL,原理框图如图2 所示。

图2 DDS 激励PLL 方案原理框图

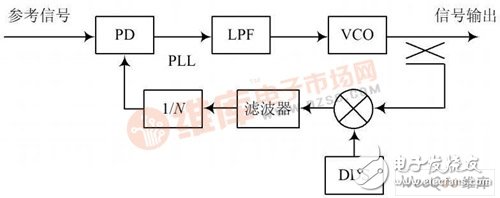

2. 2. 2 具有良好杂散性能的PLL 内插DDS 组合方案

为了解决DDS 杂散会被PLL 放大的问题,产生了PLL 内插DDS 方案。在本方案中输出信号的频率f OU T = f DDS + N f REF,DDS 的输出信号不经PLL 倍频,因而相位噪声和杂散不会在输出端恶化,具有低的相位噪声和好的杂散性能。方案中BPF2 需要滤除混频产生的多余频率分量,本身又会影响环路参数,具有一定的设计难度,且调频速率也受PLL 的限制。原理框图如图3 所示。

图3 PLL 内插DDS 组合方案原理框图

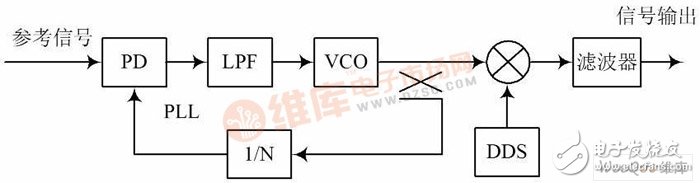

2. 2. 3 转换时间快捷的组合方案

DDS 与PLL 混频后的输出频率为f OU T = f DDS +N f L ,此方案中PLL 作为本振信号保持不变,频率转换时间只由DDS 决定,可以充分体现DDS 频率转换快捷的特点。此外DDS 的杂散不会在输出端恶化,具有较好的频谱质量。原理框图如图4 所示。

图4 原理框图

2. 3 方案选择

根据技术指标的要求,拟采用锁相方案。锁相方案也有两种: 第一种是直接对2 cm波段VCO 进行锁相,该方案的优点是输出频带较宽( 与2 cm 波段VCO 带宽相同) ,缺点是由于器件引入相位噪声的因素较多,分别受单片PLL 本底噪声,分频器以及压控振荡器噪声的影响,具有众多的恶化因素,相噪较差。第二种是在L 波段进行锁相,在Ku 波段进行上变频。该方案的输出频带较窄,但相位噪声性能好。由于该项目要求的输出频率带宽为100 MHz,故采用第二种方式,这对于相位噪声指标的实现是有利的。选用第二种方案,使得系统的大部分电路工作在Ku 波段以下的频段,便于进行小型化、集成化设计,此外,在这种方案中可以选择在L 波段频率合成源的输出端增加一级开关,以提高最终输出的Ku 信号的通断比。

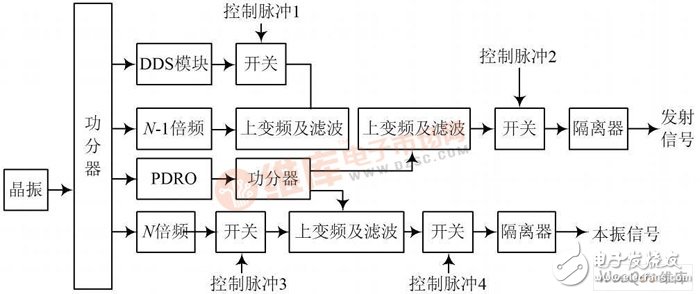

综合考虑硬件方面的实现难度及技术要求,在发射路中采用DDS 与PLL 混频的方案,该方案既可以实现较高的频率输出,又具有较高的频率分辨率。由于PLL 的频率与DDS 的频率相差太大,且有一定带宽,如果两者直接混频的话,杂波在信号带内无法滤除,所以DDS 先在一点频源上变频后再与PLL 混频,这样可以得到较好的杂波抑制。总体的设计框图如图5 所示。

图5 系统原理框图

3、详细设计

3. 1 L 波段锁相环的电路设计

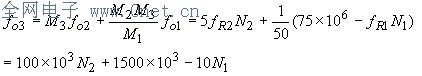

L 波段PLL 采用的是普通的分频锁相方案。该方案中参考晶振的相位噪声是- 154 dBc/ Hz@ 10 kHz,30 MHz DDS 参考输入的相位噪声基底为- 110 dBc/ Hz@10 kHz,在锁相环中鉴相器的相位噪声基底约为- 150 dBc/ Hz@10 kHz。

PLL 采用普通的分频锁相环,其分频比N 为179~ 199。晶振分频后的相位噪声远小于鉴相器的相位噪声基底,因此应当以鉴相器的相位噪声基底为参考来计算。

相位噪声为:- 150+ 20 lg 199= - 104 dBc/ Hz@ 10 kHz

3. 2 2 cm 上变频电路的设计

该上变频模块主要包括PDRO 以及两个上变频支路。考虑到指标要求本振信号和发射信号的隔离度要达到105 dB,将两路信号比较好的独立开来,尽量减少共用部分,以免相互串扰。对上变频模块来讲,最关键的问题是要采取良好的隔离和滤波措施。通过在功分器输出等地方增加滤波器,减少共用部分,在很大程度上避免相互串扰,使本振信号和发射信号的隔离度最终达到120 dB。另外针对杂波抑制要求,每路在变频之后,均采用介质滤波器。这种滤波器相对带宽窄,带内插损小和波动都较小,带外抑制很好,并且容易集成,方便调试,可以在保证通带的前提下,使其杂波抑制大于75 dB。所以通过优化设计,最终输出能满足系统对杂波抑制的要求。需要注意的是,L 波段信号的杂波已被频率源模块中的滤波器彻底滤除,否则将会给后面的输出滤波器带来无法克服的困难,导致寄生杂散。

上变频器采用普通的2 cm 混频器,其本振为2 cm波段PLO( PLO 采用取样锁相方案,该方案具有体积小、相位噪声特性好等优点) 。将本振信号一分为二,作为两个上变频器的本振输入,与两路中频端口的输入信号混频后分别得到两路2 cm 的输出信号。采用在功分器输出端加内置式隔离器,并通过衰减、放大的方式,减小两路信号通过功分器产生相互之间的串扰,增加两路之间的隔离。为了减小体积,将以上电路进行了一体化设计。

2 cm PLO 的相噪约为- 97 dBc/ Hz@ 10 kHz。这是由于2 cm PLO 的相噪与中频信号的相噪相差8 dB,所以混频后的2 cm 信号的相噪恶化1 dB 左右,即- 96 dBc/ H z@10 kHz。

3. 3 主要技术难点及采取的措施

( 1) 选用低相噪恒温晶振作为参考源,确保频率合成器的低相位噪声指标[ 9] 。采用成熟频率合成技术,通过巧妙地结合,在L 波段进行锁相,在Ku 波段进行上变频。该方案的相位噪声性能好,最终可满足Ku 波段频率合成器技术指标的要求。

( 2) 精心设计系统方案,并在方案设计中进行详细的分析、计算,注意频率选择、功率电平,减少混频交调产物,提高频谱纯度; 优化选择滤波器的形式,使得谐波及杂波的抑制度达到最佳性能。

( 3) 采用EMI 滤波器技术,降低电源干扰对输出信号频谱纯度的影响,同时降低Ku 波段频率合成器内部信号对外界的干扰,提高电磁兼容性。在电路设计中合理布局,采用表面贴装技术,采取良好的滤波、接地及屏蔽等措施,可以减小信号相互之间的串扰,从而进一步改善频谱性能,提高隔离度。在结构设计上采用多腔分隔及新材料屏蔽技术,提高屏蔽效能 。

( 4) 采用一体化设计技术和混合集成电路设计技术,实现产品的小型化。同时使得该产品使用维护方便,提高其可靠性和可维修性。

4、结 语

采用本方案设计的Ku 波段频率综合器使用于某型号雷达产品中,最终实现了本振信号和发射信号的隔离度可达到120 dB 以上,杂波抑制度达到了75 dB 以上,很大程度上减少了雷达因接收到泄漏的发射信号或杂波信号而截获虚假目标的概率,并且能有效地提高雷达的检测灵敏度。此外,采用此方案获得的发射信号及本振信号都具有很好的相位噪声特性,对提高雷达的多普勒频率分辨力也有很大帮助。

-

变频器

+关注

关注

252文章

6624浏览量

146578 -

频率合成器

+关注

关注

5文章

223浏览量

32477 -

雷达

+关注

关注

50文章

2986浏览量

118402

发布评论请先 登录

相关推荐

敏捷合成器的技术原理和应用场景

一种L波段频率合成器设计的详细介绍

基于DDS的频率合成器设计介绍

什么是频率合成器

MC145155在多环高分辨率频率合成器中的应用

射频锁相频率合成器的设计与仿真

应用于某型号雷达产品中的Ku波段频率合成器的设计

应用于某型号雷达产品中的Ku波段频率合成器的设计

评论