引 言

集成电路的生产成本以测试开发、测试时间以及测试设备为主。模拟电路一般只占芯片面积的10%左右,测试成本却占总测试成本的主要部分。所以,削减模拟部分的测试成本将有利于芯片的设计与生产。

数字电路有很多成熟的可测性设计技术( design fortest,DFT ),模拟电路测试还未发展到如此成熟,缺乏完善的模型进行自动化测试。随着集成电路的发展,混合信号芯片功能越来越复杂,但芯片I/ O 口数量跟不上芯片发展的规模,导致很多电路节点变得不可控制或( 与) 不可观察,加大了测试工作的难度。

典型模拟电路有放大器、滤波器等各种线性和非线性电路,通常包含若干串联结构的模块。本文从系统结构出发,针对串联结构电路提出一种可测性设计方案,增加较少的I/ O 口,使外部测试设备可以控制观察内部的各个模块,这些增加的I/ O 数目不随内部模块数目而变化,同时该结构还可以兼容边界扫描技术。

1 系统级的可测性设计

1. 1 控制观察模块

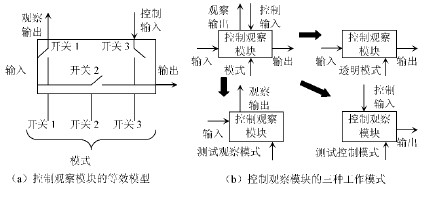

控制观察模块( contr ol observ e module,COM) 的等效模型如图1( a) 所示。由开关1、开关2、开关3 上的高低电平组成模块工作的指令码( Inst ruct ion Code) 。

如图1( b) 分别有透明模式,测试观察模式和测试输入模式。控制这三种模式的指令码分别为010,100,001。可使系统电路和嵌入式模块间建立各种通路连接方式。

1. 2 基本原理

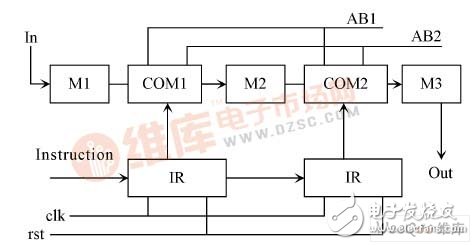

如图2 所示,In 是原始输入端,Out 是原始输出端,在M1( 模拟电路模块1) 、M2( 模拟电路模块2) 和M3( 模拟电路模块3) 之间插入COM,A B1 和AB2 是测试端口,其中AB1 为COM 观察输出端,AB2 为COM 控制输入端,IR( 指令寄存器) 与COM 模式端连接,所有IR 串联连接,在clk 作用下串行输入指令码,rst 为置零端。

图2 DFT 设计的基本原理框图

当COM1 和COM2 为透明模式时,输入In 的信号经M1,M2 和M3 到输出Out ,测试整个通路,指令码为010010;当COM1 为测试观察模式,COM2 为测试控制模式时,由通路In →M1 →COM1 → AB1 可以单独测试M1,由通路AB2 →COM2 →M3 → Out 可以单独测试M3,指令码为100001;当COM1 为测试控制模式,COM2 为测试观察模式时,由通路AB2 →COM1 →M2 →COM2 →AB1 可以单独测试M2,指令码为001100;当COM1 为透明模式,COM2 为测试观察模式时,由通路In →M1 → COM1 →M2 → COM2 → AB1 可以单独测试M1 与M2 组成的串联结构,指令码为010100;当COM1 为测试控制模式,COM2 为透明模式时,由通路AB2 → COM1 →M2 →COM2 →M3 →Out 可以单独测试M2 与M3 组成的串联结构,指令码为001010。

对于n 个模拟电路模块,通过合适的指令码也可以隔离若干内部模块进行单独测试。

2 DFT 结构的具体实现与仿真

2. 1 COM 模块和指令寄存器的实现

COM 模块内部的模拟开关选择双向传输性好的时钟控制CMOS 互补门实现。为了有效传输信号,传输门导通电阻不能随输入信号的变化而有太大的波动。

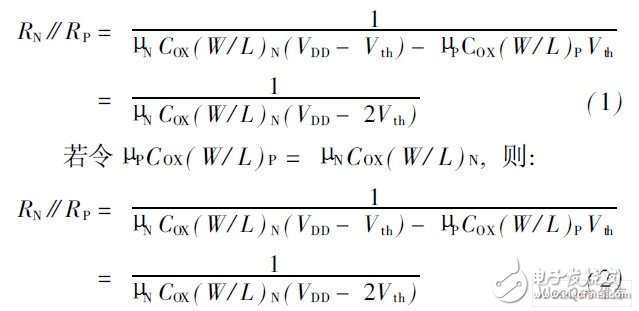

它的导通电阻计算如下:

传输门导通电阻基本不受输入信号的影响。经仿真,该互补开关的- 3 dB 带宽达到121. 8 MHz,可以满足大多数模拟电路的带宽要求。

指令寄存器模块用来实现指令移位传输以及存储的功能,它由D 触发器组成的移位寄存单元实现,并且加入了异步置零端。

2. 2 整体结构的实现与验证仿真

在模拟电路设计中多级运算放大器的使用很常见 ,作为验证,模拟电路模块M1~ M3 选择运算放大器缓冲模块,对电路进行DFT 设计,使用Cadence 软件,基于0. 5 um CMOS 工艺库对该DFT 结构进行功能仿真分析。

指令寄存器置零时所有开关断开,输入信号为偏置2 V,振幅1 V 的1 MHz 正弦波,各输出端被截止。

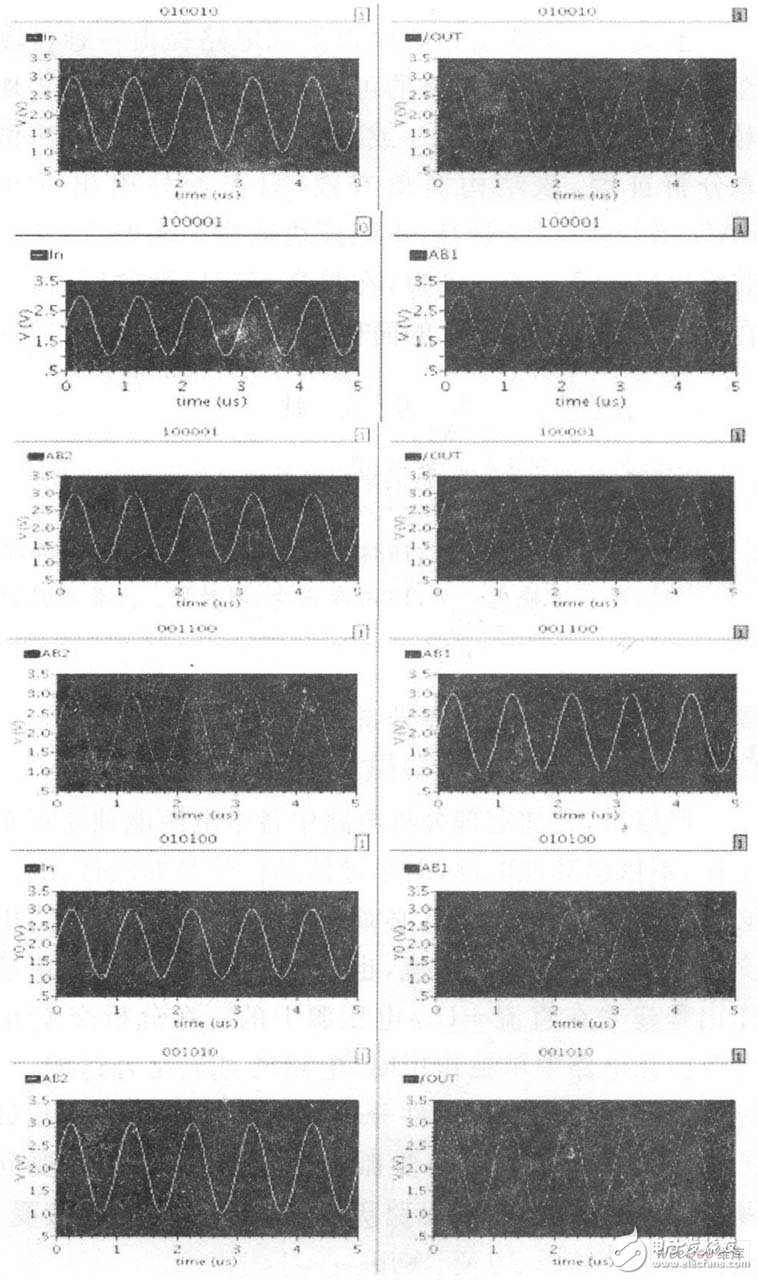

图3是在各种指令码下,电路信号传输的仿真分析,输入信号均能通过特定通路有效传输到指定输出端口。

图3 各种指令码下的电路整体仿真结果

3 与边界扫描技术的兼容性

边界扫描测试技术 在降低产品测试成本,提高产品质量和可靠性以及缩短产品上市时间等方面有显着的优点,目前在数字电路的测试中已得到很多应用。

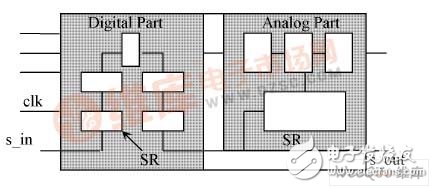

它也可应用于混合信号测试,图4 就是一种混合信号芯片测试方案。本文设计的DFT 结构中指令寄存器串接在IEEE 1149. 1 标准中的扫描寄存器后,共用时钟信号,可以进行联合测试,并且进一步减少了模拟部分额外引出的端口数。

图4 混合信号芯片测试的一种方案

4 结 语

本文针对串联结构的模拟集成电路提出一种可测性设计结构,提高了电路的可控制性及可观察性,实现对电路整体以及内部单一或几个相邻模块的测试。仿真分析证明,该结构简单有效,只需额外引出5 个PAD,数目少,灵活性高,不随模块数增加而变化,并可兼容边界扫描技术。不过,在提高可测试性的同时,会在一定程度上增加芯片的面积和功耗。

-

芯片

+关注

关注

463文章

54412浏览量

469177 -

集成电路

+关注

关注

5464文章

12681浏览量

375672

发布评论请先 登录

可测性设计结构提高电路内系统模块的可测试性

可测性设计结构提高电路内系统模块的可测试性

评论