由于成本低和集成度高等特点, CMOS技术正越来越多地应用于无线射频收发芯片的设计。低噪声放大器作为射频信号传输链路的第一级,整个系统的信噪比( SNR)很大程度上取决于低噪声放大器(LNA)的噪声系数(NF)和增益。因此,高性能的LNA成为射频前端电路设计的关键模块。其主要目的是提供较高的线性度以抑制干扰和防止灵敏度下降;提供足够高的增益使其可以抑制后续级模块的噪声以及良好的输入输出阻抗匹配;同时按照无线通信设备发展趋势所要求的, LNA必须尽可能低的功耗。

Inductive2degenerate cascade 结构式射频LNA设计中使用最广泛的结构之一,因为这种结构能够增加LNA的增益,降低噪声系数,同时增加输入与输出级之间的隔离度,提高稳定性。但是这种结构也有一些缺陷,首先它需要提供一个大感值的栅极电感,大电感不利于集成而且寄生阻抗比较大,相应产生热噪声也会比较大;而且共栅级的源端受到衬底寄生影响较大,导致信号损失,噪声系数恶化。为了实现低功耗的同时实现高增益,一种CS2CS cascaded电流复用结构得到了应用,第二级共享了第一级的偏置电流,第一级的输出通过一个耦合电容连接到第二级晶体管的栅极上,电路结构反向隔离比较差,导致电路稳定性弱。通过引入一个级间谐振电感可以有效地改善这个问题,在低功耗的同时实现了高增益,改善了稳定性。

本文采用LC并联网络来取代栅极大电感,降低噪声,节省芯片面积。同时采用了电流复用技术的两级共源结构,而且两级间采用了级联的谐振匹配网络来提高增益,降低功耗。第二部分从理论上分析了所采用的新型结构以及级间谐振电感的作用,第三部分设计了低噪声放大器电路并给出了仿真结果,最后一部分是结论。

1理论分析

1. 1新型输入匹配

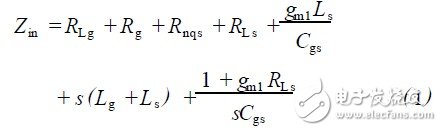

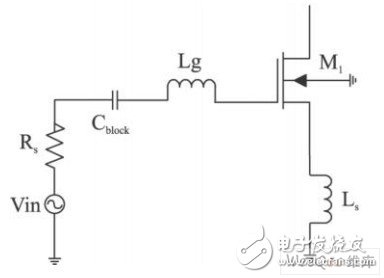

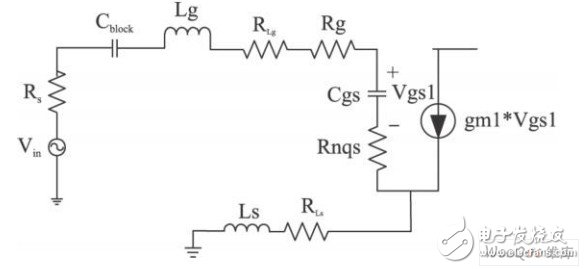

图1为传统的Inductive2degenerate cascade结构的输入匹配电路,这种结构在不恶化噪声性能的情况下很容易实现匹配,其等效小信号模型见图2,输入阻抗见式(1):

图1传统电路的输入匹配结构

图2传统输入匹配电路的小信号等效模型

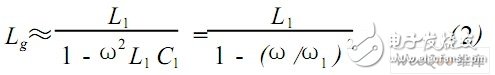

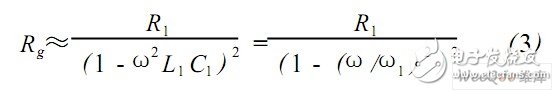

从上式可以看出,要降低Lg ,有几种简单的方法,其一是增加输入管的宽度W,这样Cgs就变大,从而Lg下降,但是这样会增大漏极电流, 从而增加LNA的功耗,这显然是不符合低功耗的要求;另一种方法是在输入管的栅源端增加一个电容,但同样降低了输入端的品质因数, 降低了电路性能。还有一种是使用一个并联的LC网络来代替大电感,图3是LC并联网络及其等效电路,为了方便推导,我们将电感的模型等效为一个理想电感L1 和理想电阻R1 的串联。这个并联的LC网络的等效阻抗为:

其中:

图3并联LC网络及其等效电路

公式中是并联LC网络的谐振频率,ω为电路工作的频率。通过式( 2) ( 3) 可知, 当0 <1 - (w/w1)平方< 1时, 这个小的LC 并联电路可以产生一个大的电感和大的电阻。由于电阻R g是由电感的寄生电阻等效而来, 并不是一个实际的物理阻抗,因此其产生的热噪声比相同阻抗值的实际物理电阻产生的热噪声要小, 理论上既可以实现阻抗匹配,同时降低LNA的噪声系数。

1. 2级间谐振电路

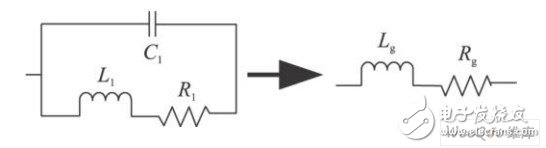

如图4所示为一个包括级间耦合电容以及级间谐振电感的两级共源放大器结构, 这种结构受到衬底寄生效应比较小, 在提高增益的同时改善了稳定性。C3 是级间耦合电容,级间谐振电感Lg2用来与第二级MOS管的输入电容谐振, 这个感值可以采用中的方法来计算。

图4带级间匹配的两级电流复用放大器

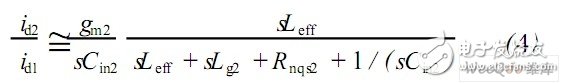

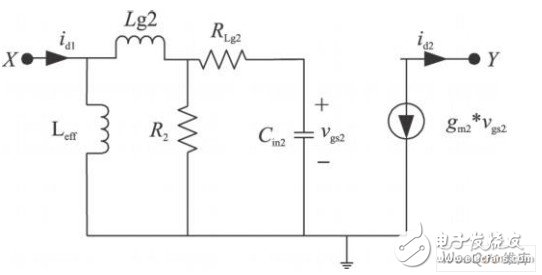

图5是X 节点到Y 的节点之间的小信号等效电路图,其中RL g2是电感的寄生电阻, Cin2是包含了M2 管的栅源电容以及Miller电容, Leff是并联网络Ld1 , Cd1的等效电感, R2 是一个大电阻,为M2 管提供直流偏置,其影响很小可以忽略不计。从该小信号电路图可以得到第一级到第二级的电流增益的表达式,见式(4):

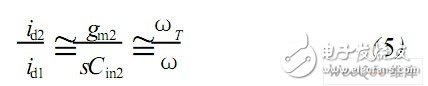

考虑到s·Leff对射频电流来说是一个大的阻抗, 于是上式又可以简化为:

上式表明通过级间耦合与级间谐振, 从第一级到第二级获得了可观的电流增益, 从而可以提高功率增益(例如在本设计中,ωT > 20 GHz) 。

图5XY两点间的等效电路图

2电路设计及仿真结果

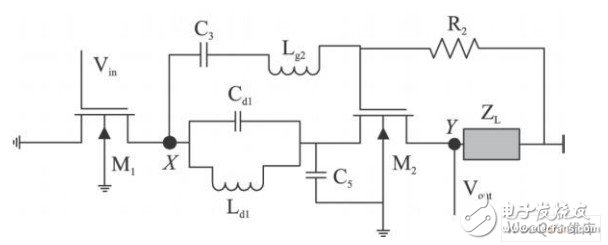

采用改进的匹配结构以及级间耦合,基于SMIC0118μm RF CMOS工艺设计了一个频率为2. 4 GHz的低噪声放大器。如图6所示就是本文的电流复用两级共源低噪声放大器的拓扑结构。Ld1 ,Cd1和Ld2 ,Cd2分别是两极共源管的负载阻抗, R1 , R2 是两个大电阻分别给两极共源管提供偏压,取4 kΩ; C1 , C3 是大电容,起隔直的作用,C5 也是一个大电容,在M2 的源级作为一个旁路电容提供交流地; Lg1 , C2 ,Ld1 , Cd1这两个并联的网络取代大电感实现阻抗匹配,减小芯片面积。

图62. 4 GHz LNA拓扑结构

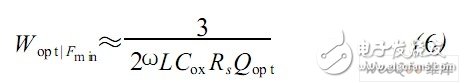

LNA的第一级对噪声影响至关重要, 根据文献中的功耗受限情况下放大管的最优栅宽计算公式来计算, 式中关于各个参数的定义见文献[ 3 ]:

M2 管的栅宽一般为M1 的一半或者相同尺寸,这需要在抑制M2 的噪声贡献以及增益线性度等方面来折衷,M3 与M1 组成一个电流镜为M1 管提供偏压,一般取W1 = 10W3。为了限制整个电路的功耗, M3 的偏置电流为180 μA, 主体电路消耗1. 8 mA,整个电路共消耗2 mA,供电电压为1. 8 V。

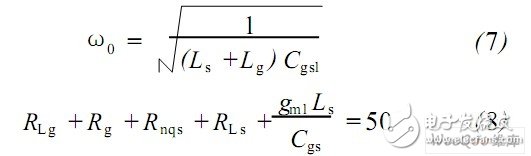

输入匹配按照式(7) 、式(8) ,其中Lg 是并联的LC网络等效感值,级间谐振电感按照文献[ 9 ]中的方法计算,值得注意的是, 因为密勒效应的影响, 输入匹配会受到级间匹配元件的影响, 因此需要反复调整各元器件的值以达到良好的匹配。

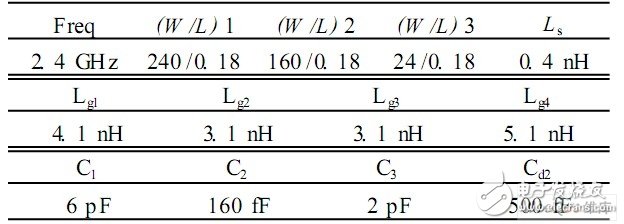

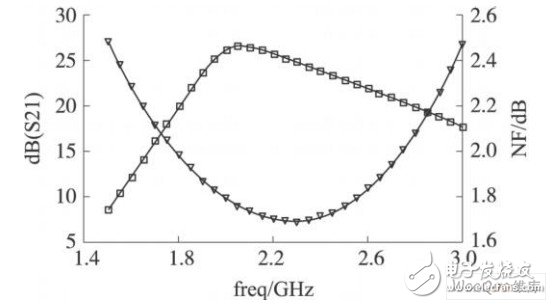

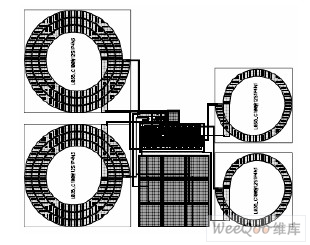

基于SM IC 0. 18μm RF CMOS工艺设计的频率为2. 4 GHz的低噪声放大器的各个性能参数由ADS( advanced design system)仿真给出,关键的电路元件参数见表1。图7表明在达到高的功率增益的同时(23 dB@2. 4 G)实现了低的噪声系数(1. 7 dB@2. 4 G) , 图8 表明实现了很好的输入输出匹配( S11, S22 < - 30 dB) ,同时隔离度大于40 dB。图9为该低噪放的版图,面积为0. 88 mm ×1. 3 mm。

表1电路中管子参数以及各个电感的值

图7低噪放的噪声系数与功率增益。

图8低噪放的输入输出反射系数

图9低噪放的版图

3结论

本文提出了一种新型的全集成的电流复用两级共源低噪声放大器,采用了新型输入匹配以及感性级间匹配结构。为了降低芯片面积,两个LC 并联网络代替了传统的大电感。这种新型的电流复用结构更有利于输入匹配,降低噪声和功耗。采用SM IC0. 18 μm RF CMOS 工艺制作了一个频率为2. 4 GHz,噪声系数1. 7 dB, S11为- 30 dB, S22为- 36dB,功率增益为23 dB ,反向隔离度小于- 35 dB,在1. 8 V的供电电压下仅消耗2 mA 。

-

CMOS

+关注

关注

58文章

5705浏览量

235317 -

放大器

+关注

关注

143文章

13570浏览量

213305 -

射频

+关注

关注

104文章

5563浏览量

167666

发布评论请先 登录

相关推荐

CHA3666-99F低噪声放大器UMS

低噪声放大器,低噪声放大器型号参数

【转帖】正确选择低噪声放大器

怎么设计低噪声放大器?

CMOS多频带低噪声放大器设计

利用Cadence设计COMS低噪声放大器

采用LC并联网络实现CMOS电流复用两级共源低噪声放大器的设计

采用LC并联网络实现CMOS电流复用两级共源低噪声放大器的设计

评论