引言

TD-SCDMA是英文Time Division-Synchronous Code Division Multiple Access(时分同步码分多址) 的简称,是一种第三代无线通信的技术标准,也是ITU批准的三个3G标准中的一个,相对于另两个主要3G标准(CDMA2000)或(WCDMA)它的起步较晚。

使用CMOS收/发开关取代GaAs MOSFET收/发开关的好处之一是CMOS开关电路不需要负的控制电压。而且,如果能用标准CMOS工艺来完成,开关电路就可以和收发器中其它RF模块集成在一起,这将降低成本。

TD-SCDMA作为中国提出的第三代移动通信标准[2](简称3G),自1998年正式向ITU(国际电联)提交以来,已经历十多年的时间,完成了标准的专家组评估、ITU认可并发布、与3GPP(第三代伙伴项目)体系的融合、新技术特性的引入等一系列的国际标准化工作,从而使TD-SCDMA[3]标准成为第一个由中国提出的,以我国知识产权为主的、被国际上广泛接受和认可的无线通信国际标准。这是我国电信史上重要的里程碑。(注:3G共有4个国际标准,另外3个是美国主导的CDMA2000、WiMAX和欧洲主导的WCDMA.)

TD-SCDMA系统规划使用的频段主要为1900MHz-1920MHz和2010MHz-2025MHz.本文采用TSMC 0.35m CMOS工艺来制作射频收/发开关。通过优化设计,该开关电路在2GHz处取得了较好的仿真结果。

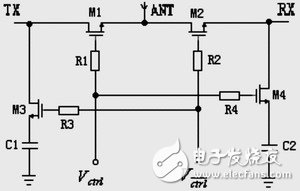

图1对称式收/发开关电路示意图

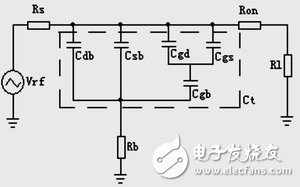

图2MOSFET导通时的等效电路图

图3开关截止一侧的小信号等效电路

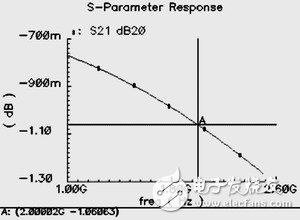

(a) 插入损耗

(b) 隔离度

优化设计

图1是对称式串并结构NMOS射频开关的电路示意图。串联的晶体管M1和M2完成主要的开关功能。控制电压Vctrl 和用于控制晶体管M1和M2的开与合。当Vctrl为高电平时,M1导通,M2截止,开关处于发射状态;当为高电平时,M1截止,M2导通,开关处于接收状态。该开关电路还包括旁通电容C1和C2,它们提供了开关电路中TX和RX端口的直流偏置。MOS管栅极上的偏置电阻R1、R2、R3和R4的作用是提高隔离度和线性度。本设计中,串联MOS管栅宽取200?m,并联MOS管的栅宽取100?m,旁通电容C1和C2取5pF,栅极偏置电阻R1、R2、 R3和R4均取10K.

射频收/发开关的重要性能指标为:插入损耗(IL)、隔离度(Isolation)和线性度(通常用1dB压缩点P1dB来表示)。其中插入损耗是设计的重点。

插入损耗

插入损耗表示当开关导通时射频信号通过射频开关的功耗。

管子的导通电阻是影响插入损耗的关键因素之一。因此,在本设计中只使用nMOSFET.由于硅衬底的导电特性,管子的漏极和源极对衬底的结电容及相关的寄生电容也是影响插入损耗的主要因素。

为了简化,只分析包含单个MOS管的电路,图2为其导通时的等效电路图。图2中,Vrf、Rs分别为等效信号源及源内阻,Ron为MOS管的导通电阻,Rb为其衬底电阻,Rl为负载电阻,Ct是其等效电容(虚线部分),其等效式为:

如果负载端和源端都与特征阻抗(Z0)匹配,则插入损耗可以用正向传输系数的幅度平方(|S21|2)的倒数来表示。

由该表达式可以看出,导通电阻Ron越大,插入损耗越大;寄生耦合电容Ct越大,插入损耗越小;衬底电阻对插入损耗的影响并不呈简单的线性关系。实际上,有一个使插入损耗最大的衬底电阻Rb(max)

因此,用CMOS技术制作的RF开关电路要获得较低的插入损耗,就要注意避免衬底电阻接近Rb(max)。然而,如果不对衬底电阻做特殊处理,这个值基本上属于RF开关电路中晶体管的Rb值的典型范围。对于标准CMOS工艺,取得较大的衬底电阻是不容易做到的,因此,降低衬底电阻是更好的方案。在版图设计中,可通过增加衬底接触来减小衬底电阻,从而达到进一步减小插入损耗的目的。

IL还可以用管子的栅宽(W)来表示,如(3)式。

一般来说,对于给定的工艺和版图类型,Rbo、Cto和Rono可以被认为是固定的。所以栅宽的大小对插入损耗起着重要的影响:随着栅宽的增大,导通电阻 Ron减小,从而使插入损耗减小;如果栅宽继续增大,通过电容Ct耦合到衬底的信号也会增大,则插入损耗会随着栅宽的增大而增大。

取并臂M3和M4的栅宽(WM3和WM4)接近WM1的一半。仿真结果表明,当WM1和WM2取200?m且WM3和WM4取100?m时,插入损耗最小。

另外,在MOS管的栅极增加电阻R的阻值也可降低插入损耗。仿真显示,随着栅极电阻的增大,插入损耗减小,但增加到10K?以后,插入损耗减小的幅度就很小了,所以考虑到版图面积,取栅极电阻的阻值为10K?.

隔离度

截止状态下,开关的小信号等效电路如图3所示。

图3中,Ron表示并联MOS管的导通电阻,Coff表示串联MOS管在截止状态下的漏/源极间电容。

依据S与Z参数之间的变换公式,可得到发射端(TX)和天线端(ANT)间的隔离度表达式:

(4) 式表明,通过使并联的MOS管的导通电阻远小于信号源的特征阻抗,使得从串联的、处于截止状态的MOS管泄漏出来的信号,可以通过并联的MOS管导通到地,而不是泄漏到发送端,从而大大提高了隔离度。从仿真的结果看,加上并联MOS管后,

可以将隔离度提高10dB以上,而由此带来的插入损耗的恶化却可以忽略。此外,增加并联MOS管的栅宽,也可以提高隔离度,但同时也会降低插入损耗和线性度,所以不宜取较大的栅宽。

性度线

线性度,即功率处理能力,通常用P1dB来表示。CMOS开关的线性度通常受到以下两种情况的制约:1.应截止的MOS管发生了导通,对于M3管,这种情况最严重;2. MOS管栅极电介质性能不够稳定。

为了提高开关的线性度,本设计采用了两种措施:1)在MOS管的漏、源极两端都加上直流偏置电压;2)给4个MOS管都加上栅极电阻R.

从仿真的结果看,增加栅极电阻可以使线性度改善5dB左右。

仿真结果

利用模型复现实际系统中发生的本质过程,并通过对系统模型的实验来研究存在的或设计中的系统,又称模拟。这里所指的模型包括物理的和数学的,静态的和动态的,连续的和离散的各种模型。所指的系统也很广泛,包括电气、机械、化工、水力、热力等系统,也包括社会、经济、生态、管理等系统。当所研究的系统造价昂贵、实验的危险性大或需要很长的时间才能了解系统参数变化所引起的后果时,仿真是一种特别有效的研究手段。仿真的重要工具是计算机。仿真与数值计算、求解方法的区别在于它首先是一种实验技术。

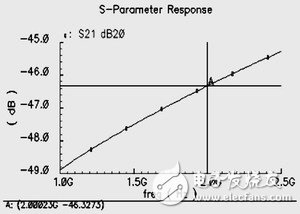

采用Cadence Spectre / Spectre RF仿真器进行仿真。在仿真过程中,分别对MOS管的栅宽和栅极电阻的阻值进行了优化选取,并确定了偏置电压和偏置电容。最终确定串联MOS管M1和M2 的栅宽取200?m,并联MOS管M3和M4的栅宽取100?m,栅极电阻R 取10K?,偏置电容C1和C2取5pF.仿真结果如图4所示。

结语

本文分析了影响对称式射频收/发开关性能的因素,包括栅宽、导通电阻、衬底电阻、栅极电阻等。采用TSMC 0.35m CMOS工艺进行设计和实现。经过优化设计和仿真,获得了插入损耗为1.0 dB、隔离度46.3 dB和1 dB压缩点12.8 dBm的电路。该射频收/发开关可以与应用于TD-SCDMA的全集成CMOS收发器集成在一起,构成集成度更高、价格更低的收发器。

-

射频

+关注

关注

104文章

5573浏览量

167693 -

天线

+关注

关注

68文章

3196浏览量

140778 -

MOSEFT

+关注

关注

0文章

35浏览量

4412

发布评论请先 登录

相关推荐

基于0.35μm工艺的Delta-Sigma ADC实现

怎么采用标准CMOS工艺设计RF集成电路?

如何在O.5μm CMOS工艺条件下设计采用电流反馈实现迟滞功能的旁路电压控制电路?

如何用0.6μm CMOS工艺实现功率放大器?

用于TD-SCDMA系统的集成CMOS对称式收/发开关的设计

基于CMOS工艺的WLAN线性功率放大器设计

0.35μmCMOS光接收机前置放大器设计

采用CMOS工艺的射频设计研究

采用RFSOI工艺来设计射频开关

基于0.35μmCMOS工艺的射频压控振荡器设计

采用TSMC 0.35m CMOS工艺实现射频收/发开关的设计

采用TSMC 0.35m CMOS工艺实现射频收/发开关的设计

评论