摩尔定律告诉我们硅制造业的改进可使我们在同样的成本下,每两年就使晶体管的数量翻一番。换个观察的角度就是硅晶圆的价格从未上升,并且硅晶圆的固定价格使我们不得不去构想如何最好地使用每两年翻一倍的晶体管。

然而,欧姆定律说明了模拟设计的规格不会随着几何尺寸的缩小而改变,并且由于电源电压降低,信噪比(SNR)很难维持,更不用说提高。的确,如果信号振幅减半,为了维持信噪比,我们需要将噪声减小一半,这要求回路中的电流增长四倍,结果是导致双倍的功耗。因此,我们处于了自相矛盾的尴尬局面,虽然小几何尺寸工艺通过降低信号振幅显着地减少了功耗并改善了数字电路的性能,但它们恰恰与模拟电路相反(为了便于描述,在此忽略了模拟电路的快速改进)。

更为重要的是,晶体管数量的倍增同样增加了设计的复杂性,要求过去常用来实现这些复杂设计的方法和工具都需加以改变;在重要设计中都了解芯片上每个晶体管作用的时代已经过去了。

尽管在设计环境中有这些显着的变化,但只需对我们身边的物理世界做一个简单的测试就可提醒我们现实世界是模拟的,并且比以前需要更多的真实世界界面(RWI)。模拟设计在任何时候都不会立刻消失,但是现在大量被实施的模拟设计的目标都在于实现这些真实世界接口,也就是典型的模数转换或数模转换的无穷尽的不同形式。

这些问题的一些反应使模拟设计师们意识到:在模拟设计问题不能从根本上得到改变的同时,为了利用设计经济学变化而产生的这些新规则所带来的实际机遇,设计架构和模式都需要改变。

从这个新兴的设计模式来看,既可以改变电路的架构来直接实施数字域的功能(这个时候模拟电路变成了 这种信号处理的ADC和DAC界面),或者也可以使用"数位增强模拟"技术。用这种方法,一种模拟功能将由其他可能相当差的执行电路技术来实现,但是它随后将被诸如校准或校正功能等数字电路包围,以帮助实现模拟性能的一种全面改善。

音频电路就呈现了采用这两种方法的几个好的例子。正如前面所提及到,模拟信噪比对功耗非常敏感,典型情况下信噪比改进3dB要求功率增长6dB.

但是在数字域,信噪比得到一个6dB的改进只需要在字长中增加一个比特,比起平常就处理20 24字节典型设计,它具有着难以置信的高价值。此外,在模拟域中如果有两个级联的两个模拟平台,它们每个大概有100dB的信噪比,它们相结合的结果是一个仅有97dB的信噪比的信号路径。因此,很明显将音频信号处理尽快移到模拟域中是很符合需要的。

快速扫描一些当今大多数音频系统架构,就可以发现这的确是正在采用的方向;信号总是在芯片输入端尽可能快地被数字化,并且仅在芯片最终输出端才转换回模拟信号。在大多数复杂的音频系统中,在多个异步时钟域中将会有几个音频流。把这些信号混频在一起需要采样速率转换到一个单一的采样域,它曾经相对昂贵直到摩尔定律给了我们所有的这些"免费"晶体管。第一代音乐播放移动电话在一般来讲在模拟域中将音乐和语音信号混合到一起,因为相对于使用相对更大线宽的数字门,这比数字方式的成本更低。其结果是恶化了整个信号路径的信噪比,当它们按路线从电路板被发送到模拟混频器时,会带来模拟信号衰落等额外潜在问题。同时,模拟解决方案在那时候是一个可接受的解决方案,在数字域中实现这种功能无论是在性能还是在成本上都明显更加可取,当然这种数字优势只会随着技术的发展而变得更广泛。

直流偏压是音频电路中的一个常见问题,当信号上电和关断时会引起爆破声和滴答声。在较老的模拟信号路径实现方式中,这些偏移一般要求通过使用外部的交流(AC)耦合电容器来被消除,从而带来与电路板面积和元器件数量等相关的成本。如今,遗留的模拟平台通常被设计为接近零直流偏移,以消除对这些额外元器件的需求。这通常通过使用一个直流(DC)伺服路径就可以达到,它在一个模数转换器中将输出信号与零做精确的比较,剩余的直流偏压在一个数字低通滤波器中进行计算,然后在模拟平台的输入端通过使用一个数模转换器计算出的偏压的倒相版本作为补偿输入,从而被消除掉。这种"数字增强模拟"解决方案使用的晶体管数量必须多达万计,仅仅是为了取代了一个独立的外部电容器,但这就是先进的芯片制造经济学带来的更佳解决方案。

这种采用数字电路来增强模拟的方法是如此令人感兴趣,它现在通常被看成是模拟电路,其实这些电路才是真正的"混合信号".同样,现在用来实现模拟电路的所需设计工具,都要求支持相当的数字电路内容。当然,传统的SPICE类型仿真工具,通常由原理图用户界面驱动,是模拟设计师在他的工具箱中选择的第一种工具。但是现在这些工具都被要求支持更高级的数字设计方法,如典型的Ver i log语言或类似的协同仿真。一旦这种混合信号方式得以确立,一位传统的模拟设计师可能认为是潘多拉的盒子已经被打开,摆在他面前的是所有与当前数字设计实践相关的设计活动,如代码驱动设计、综合、可测性设计及验证等。一旦采用这样的数字设计技术,晶体管的数量不可避免地会进一步增长;因为额外的器件被用以支持这样的设计,通常用以改善测试范围、或设计时间和可重用性。然而,当一个独立的电容器被数以万计的晶体管高性价比地取代时,这些额外的"免费"数字晶体管使模拟设计师能实现更好的结果。

很明显,现在模拟设计师的一部分主要任务就是在数字域内或外进行翻译。发明新的方法来完成该项工作会带来越来越高的精确度和效率,同时利用或替代性地利用各种新工艺技术的极限是模拟设计师的全职活动。

不同的模拟设计风格正被采用以更好地适应这些小几何尺寸工艺的优势,使ADC和DAC的性能等级正在得到进一步的提高,尽管这些工艺支持的低电压也会带来麻烦。例如,在过去,非常高品质的内置电容可用模拟CMOS工艺实现,通常使用双多晶硅层电容器(PIP)或双金属层电容器(MIM)方法来实现。这些电容器匹配得很好,利用开关电容器技术可使非常精确地实现各种ADC和DAC.然而,这些电容器在大小上并不能很好地适用于各种工艺技术,并且通常需要额外的生产步骤来构建它们。在工艺技术变得更加精细的时候,诸如开关电流或电阻器技术等其他可选方法的大小能更好地与工艺配合,并且目前是深亚微米模拟设计中一种更常见的设计方法。也许还有更好的技术就是拿电压的精确性来换取时间的精确性,充分利用永远高速前进的硅加工工艺。

几何尺寸更小的芯片能使数字电路有更高的时钟频率,同样的模拟电路可以通过更宽带宽或更高的开关速度来构建。这为模拟设计师们,尤其是那些对射频(RF)电路感兴趣的人带来了实现直到天线接线的高频电路的机会。

此外,不断提高的模拟电路速度使更高速度的ADC和DAC转换器得以实现,使RF设计师们能够对他们的电路架构进行演化,利用相似的优势尽快地进入数字领域,正如音频设计师们所做的那样。

总之,永远需要模拟设计师,但是他们确实需要逐步发展他们的技能,以适应对新技术和新工具的使用。尤其,他们需要把握机遇将数以千计的几乎是"免费"的数字晶体管放入他们的电路中。为了做到这一点,他们需要了解如何使用这些数字晶体管来发挥最好效果,以及如何在他们的架构中协调设计这些数字电路,其中最好的模拟设计师将生产出总体系统性能比以前更好的电路。

发布评论请先 登录

相关推荐

SoftServe借助OpenUSD实现虚拟设施集成

MQTT调试助手中文版(物联网开发必备)

理解机智云虚拟设备与实际设备的关系

数字信号和模拟信号的特点及应用

plc的模拟量输出一般用在哪里

技术巅峰!探秘国内高性能模拟芯片的未来发展

数字信号转模拟信号是调制还是解调

光伏微电网模拟设备测试方案

新思科技物理验证解决方案已获得台积公司N3P和N2工艺技术认证

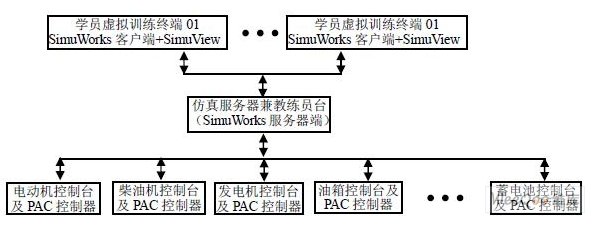

某型舰艇动力系统训练模拟器的组成与基本工作原理

模拟设计的未来

模拟设计的未来

评论