差分输入ADC特性

目前许多高性能ADC设计均采用差分输入。全差分ADC设计具有共模抑制性能出色、二阶失真产物较少、直流调整算法简单的优点。尽管可以单端驱动,但全差分驱动器通常可以优化整体性能。

差分输入ADC的一种最普通的驱动方法是使用变压器。不过,因为许多应用中频率响应必须延伸至直流,从而无法使用变压器来驱动。这类情况就需要使用差分驱动器。本教程重点介绍如何驱动高达10 MSPS采样速率的高分辨率16至18位ADC.输入信号带宽一般限于数MHz.MT-075教程阐述适用于驱动更高速ADC的差分放大器。

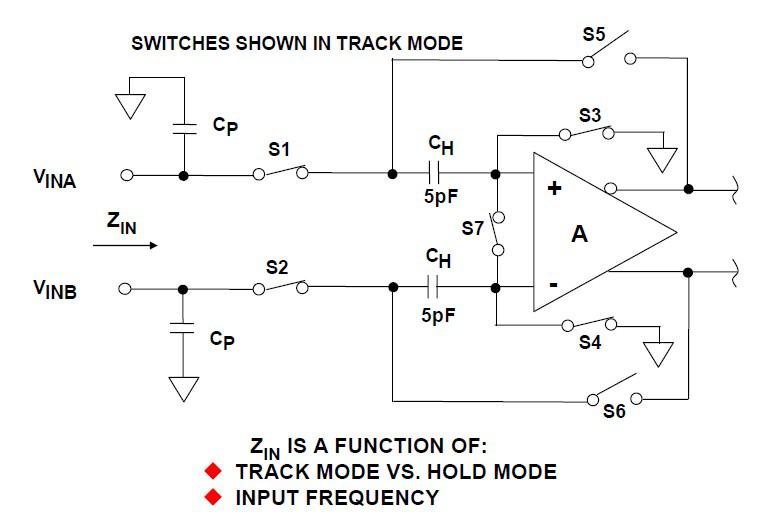

大多数高性能CMOS开关电容流水线式ADC的差分输入均类似于图1.

图1:典型非缓冲开关电容CMOS采样保持的简易输入电路。

大多数ADC都采用该差分结构。这既简化匹配要求,又减少二阶产物。此外,差分结构还有利于抑制共模噪声。

注意,SHA开关直接连接至每个输入。因为没有隔离缓冲器,开关瞬态问题可能十分突出。驱动放大器的瞬态建立时间必须足够快,否则放大器无法在半个采样周期内稳定至所需精度(该建立时间必须包括外部串行电阻的效应)。

此结构的差分输入阻抗呈动态,并在SHA切换采样模式和保持模式时变化。此外,阻抗和模拟输入频率成函数关系。

在跟踪模式(如图所示),输入信号对保持电容CH进行充放电,当电路切换至保持模式时,开关反转位置,并将保持电容上的电压传送至输出。

十分推荐这类输入采用差分驱动以实现开关瞬态的共模抑制。虽然可单端驱动它们(一个输入连接至适当的共模电压),但因为无法再抑制偶数阶失真产物,SFDR性能会下降。

图2 (A)所示为典型非缓冲CMOS ADC的每个差分输入以及采样时钟。这些输入使用一个50Ω源电阻来驱动。注意,因为前述开关动作,在每个采样时钟的边沿会出现一次瞬态。图2(B)所示为在与(A)相同的条件下的ADC差分输入信号。注意,瞬态电流毛刺属于共模信号,故大多数会被消除。注意,为了达到最佳消除状态,必须从一对平衡的源阻抗驱动两个输入(阻抗的实部和虚部都必须匹配)。

图2:典型单端(A)和差分。

(B) CMOS开关电容ADC的输入瞬态。

驱动精密16和18位差分输入ADC

图3所示为ADA4941-1驱动具有开关电容输入的18位PulSAR系列ADC.这是一种单端双极性信号、差分ADC输入的常见应用。为了实现高分辨率,驱动放大器必须具有低失真、低噪声、高直流精度以及具备单端至差分转换功能的特点。ADA4941-1是一款低功耗(2.2 mA@ 3.3 V)、低噪声(10.2 nV/√Hz @ 1 kHz)、低失真(110 dBc @ 100 kHz)的高达18位ADC的差分驱动器。小信号带宽为31 MHz.该放大器还具有轨到轨输出、高输入阻抗和用户可调节增益的特性。

ADA4941-1由两个运算放大器组成。图中下面一个配置成一个非定向同相缓冲器(带外部反馈电阻)并驱动一个反相放大器。反相放大器的前馈和反馈电阻包括在IC中。尽管反相放大器会产生额外的相移和延时,但这不会在相关频率处引入显着的误差(最高1MHz或2MHz)。

图3:在+5V应用中ADA4941-1驱动AD7690 18位PulSAR? ADC

在此应用中,两个电阻分压器将ADA4941-1的输出共模电压设为+2.1 V,这样输出只能在离地电平的100m V内。这使放大器轨到轨级具有充足裕量并允许整个电路采用+5 V单电源工作。

AD7690和AD7691的输入范围为2.VREF p-p差分。所用基准电压源为ADR444,这是一个4.096 V基准电压源。截止频率为1 MHz的低通滤波器的41.2 电阻和3.9 nF电容适合搭配输入带宽为9MHz的AD7690使用。对于所选配置,ADA4941-1输出噪声频谱密度为10.2 nV/√Hz.在滤波器带宽上积分后此值变成13 uV rms.这对应于运算放大器的107dB SNR,比ADC的100 dBSNR好7 dB.

图4所示为驱动高性能iCMOSTM PulsarTM ADC(如AD7634)的另一个示例。许多工业应用的信号高达±10 V.iCMOS系列ADC被专门设计来满足此类应用。大多数iCMOS Pulsar ADC具有差分输入。这里,ADA4922-1驱动一个16位或18位iCMOS PulSAR ADC.它执行单端至差分转换。

图4:在±12V工业应用中ADA4922-1驱动AD7634 18位PulSAR? ADC.

ADA4922-1是一款16至18位ADC差分驱动器,差分输入范围高达40 V p-p.小信号带宽为38MHz.ADA4922-1采用ADI公司专有的第二代XFCB工艺制造,使放大器可以在高电源电压条件下实现出色的噪声和失真性能。

针对该运算放大器使用1MHz低通滤波器进行噪声计算可得15uV rms.ADC的信号范围为40 V p-p,即14.14 V rms.这由于运算放大器自身会产生119 dB的SNR.

使用100 dB的AD7634 SNR,ADC均方根输入噪声可计算为141 V rms.因此,组合输入ADC噪声为142 V rms,运算放大器所贡献的噪声几乎可以忽略不计。

发布评论请先 登录

精密ADC用差分驱动器

精密ADC用差分驱动器

评论