1 引言

随着数字信号处理技术在无线通讯等领域的广泛应用,人们对于模/数转换器(ADC)速度与精度等方面要求也越来越高。但出于功耗和成本等方面的考虑,器件尺寸和电源电压的降低使得高速高精度ADC的设计变得越来越具有挑战性。在各种不同类型的ADC中,流水线结构(pipeline)的ADC很好地协调了面积与速度之间的矛盾。他具有相对低的功耗和芯片尺寸,同时可以实现较高的转换速率。但是在实现高分辨率的流水线ADC时,由器件失配等因素引起的误差(如比较器电压失调引起的阈值偏移,电容失配等)如果不消除,将对ADC的性能产生严重的影响。因此,为了减小误差,使ADC达到更高的有效精度以满足人们对高精度的现代数据采集系统的需求,许多的片上校准技术被开发出来,这些校准技术虽然各具特点,但总体上可以分为以下2大类:片上模拟校准;片上数字校准。此外,还有一类重要的校准技术——电容误差平均(CEA)技术。CEA技术之前一直被认为是模拟校准中的一种方式,但2006年数字电容平均技术的提出,使其现有的实现方式中既有模拟校准,又有数字校准。本文就电容误差平均技术中的各种方法的原理及特点做一简单的介绍,并由此展望其发展趋势。

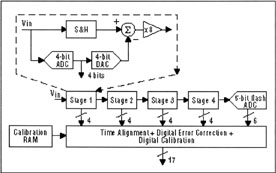

2 流水线ADC的结构

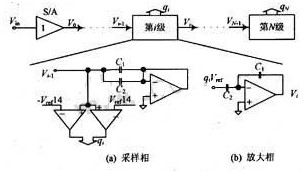

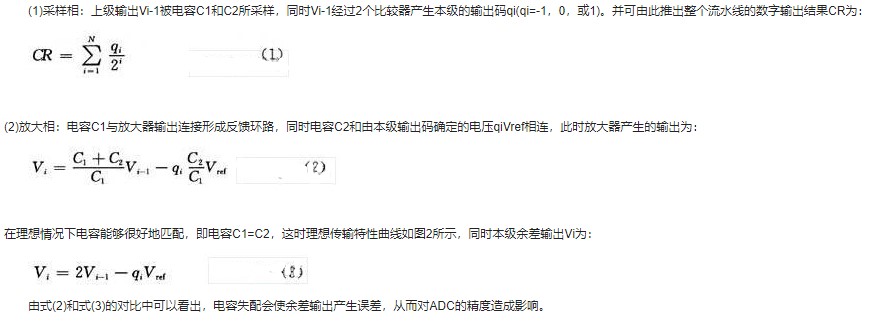

虽然实际的流水线ADC应为全差分结构,但是由于电路的对称性,本文只对单端进行原理分析(有源误差平均技术除外)。如图1所示,整个电路由1个采样保持电路和N位相同的子级电路构成。其每一个子级的工作原理相同:

3 电容误差平均技术介绍

电容误差平均技术是一种重要的对温度和老化不敏感的校准方法。其基本思想是利用电容交换得到2个带有互补误差的输出,然后进行平均使原先的误差由一阶变为高阶,从而得到较为精确的输出。

3.1 有源电容误差平均技术

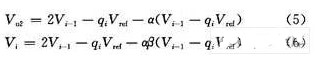

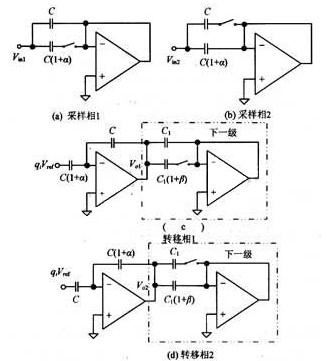

有源误差平均技术(Active Capacitor Error-aver-aging technique,ACEA),其电路结构同标准流水线型ADC基本相同,不同的是其在冗余放大器之后增加了一个误差平均放大器。同时,时钟由2相变为3相,分别为采样相、放大相以及平均相。工作过程如图3所示。由于在实际电路当中电容之间均存在不匹配,在这里假定冗余放大器和平均放大器输入端相连的电容值分别为电容C和C(1+α)以及C1和C1(1+β),α和β分别为电容的失配系数。

在采样相,输入电压Vi-1被电容C和C(1+α)所采样;然后在放大相,电容C(1+α)同电压qiVref相连,这时冗余放大器产生的冗余输出与实际的理想值存在一个差额,由式(2)可知此输出Uo1实际是未加校准时的级间输出,同时Vo1被后面的电容C1和C1(1+β)交叉采样,其表达式为:

最后进入平均相,由于电容C和C(1+α)连接关系互换,并且电容2C1同平均放大器输出连接形成反馈环路,此时冗余放大器产生的冗余输出和最终平均放大器的输出为:

从以上分析可以看出,最终输出表达式(6)与未加校准时的输出相比,误差由一阶变为二阶。假设失配系数β为3%,可以看到校准后误差降为未校准前的3%,从而达到校准的目的。

3.2 无源电容误差平均技术

虽然通过ACEA技术可以得到正确的输出,但是这是以电路的复杂度倍增为代价的。由此,Chiu提出一种无源电容误差平均技术,简称PCEA技术,他使用双采样代替ACEA技术中的误差平均电路,使电路规模大为降低。

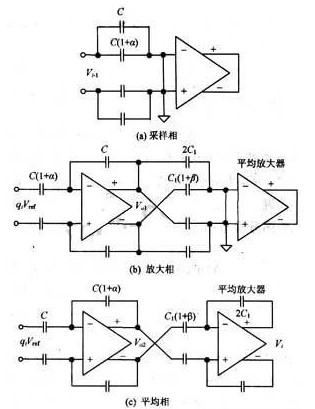

图4为这种PCEA技术的原理图。其电路基本结构与未加校准时完全相同,但每一个转换周期由2个采样相和2个转移相构成。图中的输入Vin1和Vin2为前级电路转移相的2次误差互补输出,如果是第一级电路则输入Vin1=Vin2,为采样保持电路的输出。

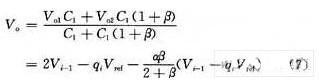

为方便解释,假设Vin1=Vin2=Vi-1。分析可知,第i级在转移相1和转移相2的两次输出Vo1和Vo2电压值同有源电容误差平均原理分析中的Vo1和Vo2相同,分别为式(4)和式(5),显然Vo1和Vo2两者的误差互补。因为同时Vo1和Vo2分别被下一级的电容C1和C1(1+β)所采样,所以在电荷共享后C1和C1(1+β)上的等效输出余差电压为:

显然可以看出误差电压由式(4)和式(5)中的一阶变为式(7)中的二阶,从而达到电容误差平均的目的。同有源技术相比,无源技术将电路的规模减小近一半,因此可以达到减小功耗、面积和噪声方面的目的。但是,由于一个转换周期需要4个时钟相,使得模/数转换速度比未校准时要慢一倍,因此适用于速度要求不高而功耗和分辨率要求较高的场合。值得一提的是,由于PCEA技术在速度方面的性能较低,文献[5,6]提出一种改进的PCEA技术,使速度等方面的性能得到了一定的提高。

3.3 数字电容误差平均技术

由于ACEA技术和PCEA技术在工作时都需要增加额外的时钟相,降低了转换速度,O.Bernal等人提出一种数字电容误差平均(Digital Capacitor Error-averagingtechnique,DCEA)技术。这种技术采用上述模拟电容误差平均技术的思想并使其在数字域中实现。他采用电容误差平均的原理得到校对系数,在校对过程中,再根据各级输出调用这些常数。因为DCEA技术不用增加额外的时钟相,所以其速度可以达到PCEA技术的2倍(如表1所示)。以下为DCEA技术的工作原理。

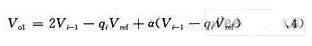

根据式(2),令C1=C(1+α),C2=C(1-αi),出于算法阐述方便性的考虑,这里的电容失配系数定义为2αi。由此可以得出:

DCEA技术的校准过程与文献中的查表校对法类似,从最低位开始到最高位结束。他将CEA技术中模拟域的矛盾成功的转移到了数字域。并通过有效的数字运算将其解决,使得电路的性能得到提高。

4 总结与展望

本文主要介绍3种不同的电容误差平均技术在流水线ADC中的应用。其中ACEA是典型的模拟校准技术,需要增加额外的模拟电路以及额外的时钟来实现;PCEA虽然不用加入额外的模拟电路,但相对于ACEA需要更多的时钟来处理,因此从本质上来说也属于模拟域的范畴;而DCEA技术则属于数字校准方法。从ACEA技术发展到DCEA技术,校准方法也由模拟校准过渡到数字校准,电路性能的提升是显而易见的。随着人们对流水线ADC精度与速度要求的不断提高,其误差校准技术的研究也是日新月异。由于数字校准相对可以带来更低的功耗、更小的面积和更大的设计灵活性,因此可以给校准技术的发展提供更为广阔的空间。总之,随着新的校准技术的运用以及集成电路工艺的发展,流水线ADC必将沿着低功耗、高速度和高精度的的方向不断进步。

-

adc

+关注

关注

98文章

6498浏览量

544612 -

比较器

+关注

关注

14文章

1651浏览量

107216 -

数字信号处理

+关注

关注

15文章

560浏览量

45856

发布评论请先 登录

相关推荐

流水线ADC结构解析 流水线ADC和其它ADC的比较

FPGA中的流水线设计

现代RISC中的流水线技术

流水线ADC

流水线中的相关培训教程[3]

流水线中的相关培训教程[4]

流水线ADC的行为级仿真

嵌入式_流水线

CEA技术的原理特点及在流水线ADC中的应用

CEA技术的原理特点及在流水线ADC中的应用

评论