1 引 言

由于数字电视能提供更清晰的图像、更逼真的声音、更大的屏幕,以及数字化传输方式所特有的高效数据传输率,可以在有限的传输频带内传送更多的电视节目,正成为数字化视听技术发展的一个新方向。作为数字电视前端设备中的卫星数字电视码流转发器,简称为码流机,其主要功能就是接收频率为950~2 150 MHz的国内外数字卫星节目信号进行QPSK解调,并转换成ASI格式的MPEG-2传输流,输出给TS流复用器、QAM调制器等前端设备处理后发射到数字电视终端用户,即相当于有线电视台转播节目的信号源;同时他还输出模拟视频和音频信号,供管理人员监控使用。本文主要讨论如何把调谐器输出的TS流转换为ASI格式的MPEG-2传输流。

2 系统硬件组成及ASI接口

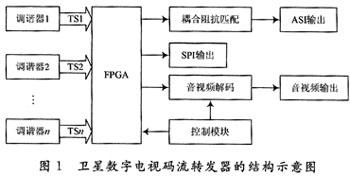

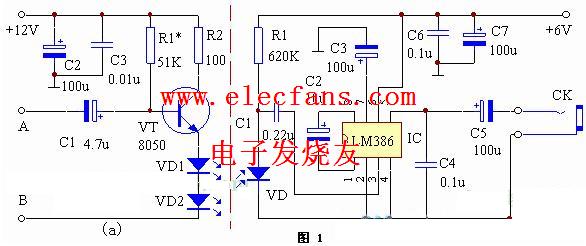

卫星数字电视码流转发器主要由调谐器,FPGA,ASI输出,SPI输出以及音视频解码输出部分构成,其中调谐器部分负责接收来自卫星的节目信号;音视频解码输出是供管理人员监控使用;FPGA主要负责ASI的数据链路层的具体实现、SPI输出以及TS流的转接到音视频解码芯片上;控制部分主要负责码流路由选择和音视频解码部分的控制。其内部结构如图1所示。

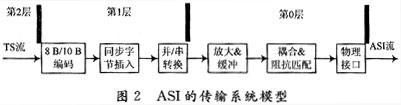

由于SPI接口采用的是低电压差分信号,其传输距离短、抗干扰性差,因此当今数字电视前端设备的输入输出接口一般都要求配有ASI接口。DVB-ASI是一种传输速率恒定,允许具有不同数据速率的串行编码传输系统,我国的ASI接口没有采用ISO/IEC规定的265.625 Mb/s传输速率,而是采用了270.000 Mb/s的传输速率。DVB-ASI接口协议是基于MPEG-2传输包的分层结构,共分3层,如图2所示。

第0层:物理层,传输介质可以是电缆或光纤;

第1层:数据链路层,主要定义了8 B/10 B编码,同步

字节插入以及串并转换;

第2层:传输层,采用MPEG-2的传输包,有两种传输数据格式:一种是每个TS包中的188 B是连续的,同步字插在两个包间,称为突发模式(burst);另外一种是同步字随机均匀地插在TS数据之间,称为非突发模式,一般设备只支持非突发模式的传输。

下面主要讨论数据链路层的。FPGA的具体实现。

3 8 B/10 B编码的理论基础

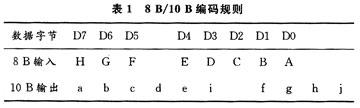

DVB-ASI的8 B/10 B编码[2,3]主要包括数据编码,插入特殊字符和误差控制。通过8 B/10 B映射保证发射信号正负均衡,即‘O’和‘1’为1∶1的直流信号,并且不会有连续的‘0’或连续的‘1’。每8 b分成3 b和5 b两组,分别映射成4 b和6 b两部分,合起来就是10 b。其中每部分按照‘0’和‘1’的数量关系有惟一的奇偶特性,称之为RD(Running Disparity),当‘1’的个数大于‘0’的个数时,RD为正,反之为负。个数相等时,RD保持不变[4]。具体的编码规则见表1。

每个编码字符可表示为Dx.y或Kx.y,D表示是数据信号,K表示是字符信号。

其中x,y为十进制数,编码中依次对一个信息字符的x和y部分进行编码,其编码的结果取决于当前x或y的值和前一次编码结果的RD。若前一次RD为正,则后一次编码采用RD为负的码字编码,反之亦然。这样编码的结果保证传输信号的电平统计上的直流特性。

在这种编码控制下,根据RD的变化一方面可以保证比特流的直流特性且不会存在多个的连续‘O’或连续‘1’;另一方面可以进行自动检测,实现误差控制。ASI传输系统中的误比特率小于10-13。系统中插入的特殊符号实现控制功能,包括同步信号K28.5,在接收端的字节同步正是依靠检测到连续两个K28.5的同步信息且满足奇偶校验,在同步信号后的比特被依次组成字节,完成字节同步。

4 FPGA部分的详细设计

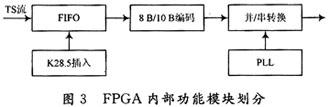

在FPGA的设计中,我们选用Altera的EP1C3T144C8。按照自顶向下的设计思路,我们把FPGA的ASI部分详细设计化分为5个子模块,如图3所示。

4.1 输入FIF0的设计

由于从调谐器输出的TS流与实际FPGA处理的TS流速度并不是同步的,因此在FPGA内部建立一个FIFO对输入的TS流进行数据缓冲处理是必需的,但FIFO的深度是一个不容忽视的问题,FIFO的参考设计深度为一帧TS流长度的2倍,由于一个TS包的长度可能是188 B,也可能是204 B,同时,由于8 B/10 B模块读FIFO的速度是恒定的27 MHz,大于TS流的数据速率,因此FIFO是永远都不会上溢的。综上所述,FIFO的深度选用512 B是比较合适的。

4.2 8 B/10 B模块设计

在该部分设计的过程中,参照上述的8 B/10 B理论基础[4],我们没有选用CYPRESS公司的CY7B923[5]HOTLinkTM专用芯片,也没有选用Altera的8 B/10 B的IP Core,而是自己开发的8 B/10 B模块,按照自顶向下的设计思路,我们把该部分又分为6个子模块,其对应的Verilog接口如下:

8 B/10 B顶层模块:module top——8B10B(clk,rst,din,dout,invalidK);

3 B/4 B模块:module e3Bto4B(clk,rst,din,kin,dout,dsp4b);

5 B/6 B模块:module e5Bto6B(clk,rst,din,kin,dout,dsp6b);

K字符检测模块:module k_detector(clk,rst,din,kin,invalidK);

特殊3 B字符处理模块:module dec_spec3b4b(clk,rst,din3b,din4b,kin,rdp,rdn);

RD控制模块:module RD(clk,rst,kin,din4b,din6b,dsp4b,dsp6b,out6b,out4b,rdp,rdn);

4.3 同步字节插入模块设计

当TS流的数据速度始终小于8 B/10 B编码模块读取数据的时候,FIFO就有可能下溢,当FIFO为空时,并/串转换模块的输入数据为K28.5同步字节(8 B/10 B编码后为:0011111010或1100000101)[6],以达到ASI的固定的270.000 Mb/s的传输速率。同步字节的插入方法有两种:

(1) 由TS流中的数据有效信号来确定是否向FIFO中插入K28.5同步字节;

(2) 由FIFO的EMPTY信号和来确定并串转换模块的的输入数据为0011111010或1100000101,即不通过8 B/10 B编码模块。在本设计中,我们选用了方法(1)插入K28.5同步字节。

4.4 并/串转换模块设计

该模块对10 B的并行数据进行并/串转换,在实际的设计中,采用1个移位寄存器和1个计数器即可完成并/串转换操作。

4.5 PLL模块设计

由于ASI的标准输出速率是270.000 Mb/s,因此为整个并/串转换的最小时钟就是270 MHz,而系统FPGA的外部时钟选用的是27 MHz的有源晶振,所以可以采用EPlC内部自带的锁相环来提供270 MHz的内部时钟,实际的操作方法就是例化一个PLL模块,把倍频系数设置为10即可。

5 系统测试与仿真结果

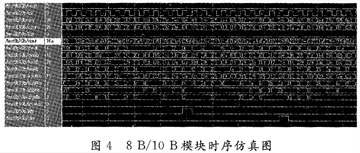

对数字卫星码流转发器ASI输出的测试可以采用标准MPEG-2码流分析仪AD953,也可以直接选用DVB解码器,以观看能否正确收视节目来确定ASI流是否正常。FPGA部分设计的软件平台选用Quartuns和仿真工具ModelSim,部分仿真结果如图4所示。

6 结 语

本方案经硬件实现后,接上卫星信号,ASI接口输出的信号经过DVB解码器后,得到了稳定连续的音视频信号。采用一块FPGA代替传统的CY7B923+CPLD方案,由于省去了价格昂贵的CY7B923HOTLinkTM芯片,大大降低了该部分的物理成本和硬件电路原理设计的复杂性,因此,本方案具有很强的实用价值。

-

FPGA

+关注

关注

1664文章

22508浏览量

639465 -

视频

+关注

关注

6文章

2014浏览量

75195 -

卫星

+关注

关注

18文章

1877浏览量

70395 -

调谐器

+关注

关注

1文章

183浏览量

30637

发布评论请先 登录

如何采用FPGA芯片实现卫星数字电视码流转发器电路原理设计

如何采用FPGA芯片实现卫星数字电视码流转发器电路原理设计

评论