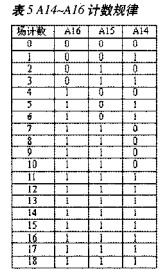

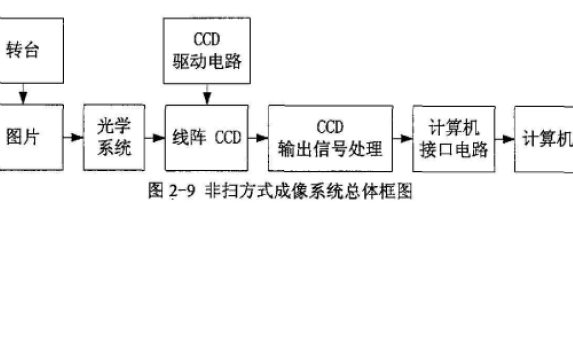

CCD驱动电路的设计是CCD应用的关键问题之一。由于不同厂家生产的CCD的驱动时序不尽相同,同一厂家不同型号的CCD驱动时序也不完全一样,因此CCD用户必须面对驱动电路的设计问题。以往采用不同功能的数字芯片搭成的驱动电路,调试困难,灵活性较差。而采用EPROM设计驱动时序,虽然设计的系统性能稳定,但是器件要工作还需要地址发生器,不但增大电路板面积,存储的数据也不能在系统修改。本文以TCD1208AP为例,说明CCD时序发生器的设计原理,基于在系统可编程(ISP)技术和ispLSI器件实现了系统设计和仿真。ispLSI系列器件提供编程口,可直接修改其内部程序。

CCD的时序分析

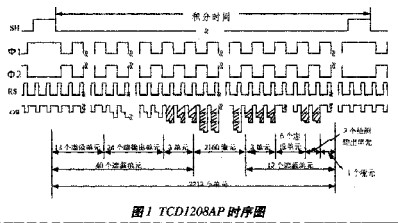

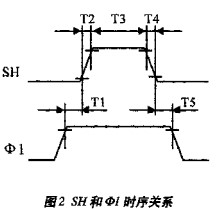

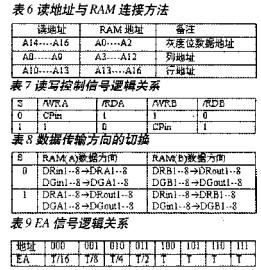

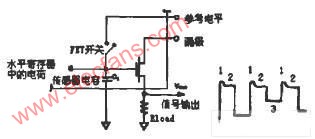

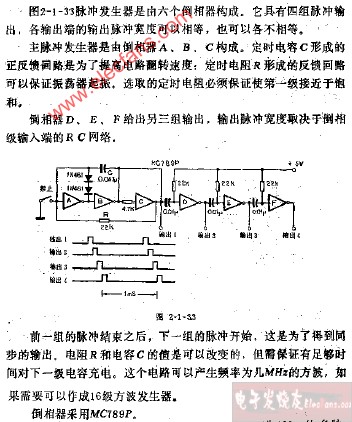

二相线阵CCD图像传感器TCD1208AP,时序关系如图1所示。需要4路驱动信号,即:转移信号SH,脉冲宽度标准值为1000ns,其周期为光信号积分时间;复位信号RS,时钟频率标准值为1MHz,复位一次输出一个信号;两相移位时钟信号F1与F2,时钟频率标准值为0.5MHz。TCD1208AP是2160像元CCD,正常工作时,要输出52个虚设单元(含暗电流信号)信号。因为该器件是两列并行传输,所以在一个周期内至少要有1106个F1脉冲,即TSH》1106T1。时序图中需要特别关注的是SH与F1、F2的关系,当SH高电平期间,CCD积累的信号电荷包通过转移栅进入移位寄存器。这期间,移位脉冲F1、F2要求保持一个高和低的电平状态。其中SH与F1时序关系如图2。

ISP技术及ispLSI器件

在系统可编程打破了传统可编程逻辑器件(PLD)的局限,使硬件设计变得象软件一样易于修改,从而缩短了系统的调试周期,而且不需要编程器,更不需要编程高压。

ispLSI系列器件是Lattice公司推出的高性能大规模可编程逻辑器件,集成度在1000门到25000门之间,引脚至引脚延时最小可达3.5ns,系统工作速度最高可达180MHz。ispLSI1016由可编程宏逻辑单元组成,而每个宏逻辑单元既可以定义成组合逻辑,又可以定义成时序逻辑。它有2000个等效逻辑门,32个通用I/O单元能定义成输入、输出、三态或双向端口,另外还有4个专用的时钟输入端。

CCD时序发生器的设计

基于ispLSI1016的设计流程

Synario软件能够支持ispLSI器件的设计、编译和逻辑模拟,能够进行原理图输入和ABEL-HDL硬件描述语言输入,并且还提供了功能仿真器,可以用报告形式或波形观察器检查仿真结果。Synario的混合式设计输入方式允许在同一器件的设计中同时采用原理图、高级语言、真值表和状态机输入方式。基于ispLSI1016器件设计CCD时序发生器时,逻辑设计流程包括下列步骤:设计输入、设计实现、器件编程、设计校验等。

* 设计输入:首先按CCD时序发生器的原理将其分成高低几个逻辑关系层。利用模块化的设计方法,对各部分逻辑关系使用原理图与硬件描述语言混合进行描述。

* 设计实现:从设计输入文件到熔丝图文件的编译实现。包括:逻辑、合并、映像、布局、布线、生成编程数据文件(JEDEC)。为方便设计需要,使用软件的引脚锁定功能将信号连接在指定的引脚上。除端口锁定需人工干预外,所有的布局和布线过程均可自动完成。

* 器件编程:把JEDEC形式的文件传送到器件中。ispLSI的编程和改写由片内的状态机控制,状态机的输入即为片内的5个编程接口信号。

* 设计校验:设计校验过程与设计过程是同步进行的,针对设计输入、设计实现和器件编程,设计校验可分为前仿真、后仿真和实验验证三个部分。在设计输入阶段,进行的功能仿真验证逻辑功能,所以又称功能仿真;后仿真又叫时延仿真,是在选择了具体器件并完成布局布线后进行的定时关系仿真。

设计实现与仿真

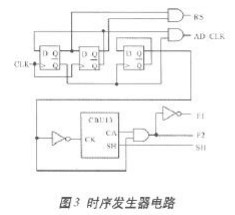

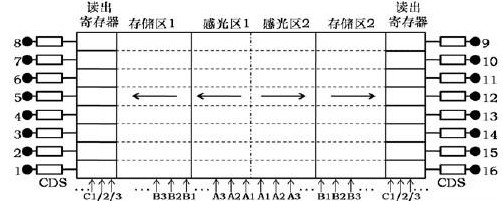

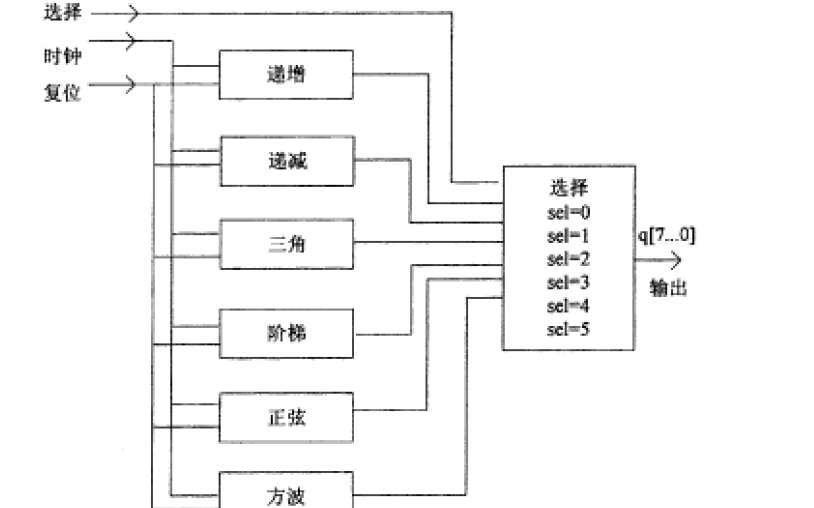

时序发生器电路如图3所示,4MHz时钟信号CLK经4分频及逻辑组合电路产生频率为1MHz的复位脉冲RS和A/D控制信号AD_CLK(采样脉冲);再经2分频产生0.5MHz的计数脉冲。这个计数脉冲送入计数器CBU13,CBU13是13位计数器,此模块由ABEL-HDL硬件描述语言编写完成。根据CCD时序分析,计数器最低计数值为1106,增加计数值就延长了积分时间;计数器计满则产生转移脉冲控制信号SH。CBU13的功能就是完成积分时间控制,即通过计数器输出控制逻辑,产生SH信号和两相移位脉冲信号的控制信号CA,信号CA与计数脉冲经过与逻辑就得到F2(F2),而F2取反就得到F1(F1)。信号CA主要是控制SH高电平时与F1(F1)的关系,如图2所示。具体设计时,只需当计数器满时让组合逻辑电路产生一个持续时间为1个计数周期以上的高电平信号(其它时间为低电平),就可作为SH。另外产生一个持续时间≥2个计数脉冲周期的低电平信号,这个信号和0.5MHz的计数脉冲经过与门后就得到需要的F2。

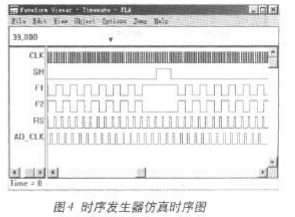

时序发生器设计完成后,经过软件仿真,得到如图4所示的波形,图中所示的时序关系满足图1的要求。用Synario软件设计驱动电路时,可以采用原理图、ABEL-HDL等多种方式。设计CCD驱动电路时,先将系统划分为不同的功能模块,功能复杂的模块均采用硬件描述语言设计。因为应用时只需根据具体CCD器件的要求修改积分时间等参数即可,如果采用原理图则需修改连接线路。

结语

CCD驱动电路一般有四种设计方法,分别为存储器驱动、IC驱动、单片机驱动、以及可编程逻辑器件驱动。采用ispLSI器件设计CCD时序发生器,使得电路由原来复杂的设计变成主要只用一片ispLSI1016来实现。独立的单元测试与系统联调结果均表明:采用ISP技术实现CCD时序发生器,提高了系统的集成度;系统抗干扰能力和稳定性也增强了;同时还使设计与调试周期缩短至小时数量级

-

传感器

+关注

关注

2577文章

55498浏览量

793888 -

发生器

+关注

关注

4文章

1431浏览量

64672 -

仿真

+关注

关注

55文章

4535浏览量

138659

发布评论请先 登录

基于FPGA与的VHDL语言驱动时序发生器与数据缓存器的一体化设计

如何完成基于FPGA技术的驱动时序发生器与数据缓存器的一体化设计?

CPLD设计的CCD信号发生器技术

基于FPGA的DDS波形信号发生器的设计

采用FPGA设计科学级CCD相机时序发生器

采用3级LFSR实现Gollmann流密码发生器的设计并进行仿真验证

如何使用智能函数发生器进行VHDL的设计与仿真

CCD的工作原理和几种产生CCD驱动时序方法

ADDI9020:带V驱动器和精密时序发生器的60 MHz CCD信号处理器数据表

采用ispLSI器件设计CCD时序发生器并进行仿真验证

采用ispLSI器件设计CCD时序发生器并进行仿真验证

评论