随着社会的发展,无线通信已成为日益重要的信息传递方式。伴随着深亚微米CMOS工艺的成熟,采用蓝牙技术接收发送射频电路已可实现单片集成。然而,一个好的射频接收发送芯片必须有尽可能低的成本和优良的性能,后者通常需要通过合适的测试方法来检测和保证。在传统的设计流程中,往往在芯片设计接近尾声的时候才会考虑到可测性设计。再加上射频电路本身难以测试的特点,不佳的可测性设计不但会大大增加后期芯片测试验证的难度,还会使得芯片的整体制作成本显著升高。为了能有效控制测试成本,必须在设计开始阶段就考虑系统的可测性,甚至在确定系统架构和规范之前,就应将各种可测性问题、测试设备的成本以及测试所需要的时间考虑在内。通过对系统架构和规范的调整,合理的可测性设计可以内嵌于系统之中,这样不仅可以有效控制因测试而导致的硬件成本增加,而且还大大提升了芯片的可测性。

本文介绍了一种基于蓝牙射频电路可测试性设计的8位逐次逼近型ADC,该电路结构简单紧凑,功耗较低,专门针对将可测性设计嵌入系统架构而设计。通过ADC可以方便地检测蓝牙电路中各模块的直流工作点,在输入中加以简单的激励信号,还可以对部分模块的性能参数予以检测。该方法使得芯片的可测性问题变得易于实现,并且只是有限地增加了芯片的整体硬件成本。

ADC的体系结构

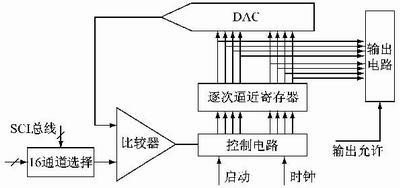

针对可测性的设计,本文中的ADC体系结构示意图如图1所示。

图1 ADC体系结构

整个电路工作原理比较简单:由数字电路组成的逐次逼近寄存器和控制电路将DAC每位依次置1”,DAC的输出值与输入模拟电压通过比较器进行比较,并确定“1”是否保留。当8位完全确定后,就可以得到一个最逼近输入模拟电压的数字值。与传统的逐次逼近型ADC的不同之处在于,为了能对多路信号进行测试,用一个十六选一的选择器代替原本的采样保持电路,在系统SCI总线控制下,可以选择不同通道的信号进行测试。

rail-to-rail输入比较器和R-2R网络DAC的设计

比较器设计

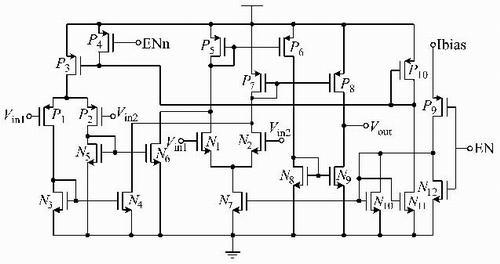

由于测试信号本身幅度的关系,ADC的动态输入范围必须在0~3.3V,为此,在本设计中对比较器采用了rail-to-rail的输入设计。图2是比较器的电路图。

图2 rail-to-rail输入比较器

该比较器电路由22个MOS晶体管构成。电路采用折叠对称结构,P9、N12作为开关控制电路的偏置电流。对于PMOS差分对,其共模输入范围VCM可表示为:

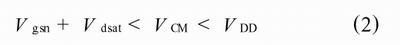

式中VCM为共模输入电平,VDD为电源电压,Vdsat为差分输入级中源漏饱和压降,Vgsp为PMOS输入管的栅源电压。同理,对于NMOS差分对,其共模输入范围可表示为:

式中Vgsn为NMOS输入管的栅源电压。将上述PMOS和NMOS差分对并联起来,则整个电路的共模输入范围可写成:

从而实现了输入级的rail-to-rail,工作电压的最小值为:

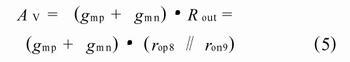

当共模输入电平接近VDD或0时,只有NMOS或PMOS差分输入对处于放大状态;当共模输入电平处于中间状态时,PMOS和NMOS差分对都处于放大状态。因此,比较器的增益可以表示成:

N管和P管跨导的叠加,可以大大提高增益,从而使得比较器的精度也显著提高。但是当共模输入电平从0到VDD变化时,总的等效跨导gmeff变化很大,会使电路的单位增益带宽受到一定影响。

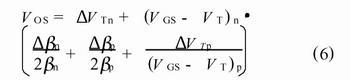

比较器的分辨率还与差分输入对的失调电压有很大关系,在现在的CMOS工艺中,一般为几~几十毫伏,这会严重影响比较器的精度。一般失调可分为系统失调和随机失调,前者可以通过采用合适的结构来消除;后者由于受工艺条件限制,往往较难避免。以N管差分对为例,随机失调可近似表示如下:

通常人们使用数字校正,自动补偿等方法来减少失调,但这样会引入额外的硬件消耗和功耗。为了降低成本,便于实现,本设计主要通过对管子的优化设计来减少随机失调。在式(6)中(VGS-VT)n、(VGS-VT)p分别为N管和P管的有效偏置,ΔVTn、Δβn和ΔβP都跟√WL成反比。显然采用较大的管子面积,较小的输入管(VGS-VT)和较大的负载管(VGS-VT)可以有效减少失调。因此,在设计中,差分输入对都取了较大的尺寸,并通过设置合适的工作点,使得输入管的(VGS-VT)保持在0.2V左右。

在版图设计时,则采用几何共中心的交叉结构,使得差分输入对尽可能对称,并且添加了Dummy管,使管子的周边环境保持相同。此外,在比较器的输出端还增加了两个反向器,使得高低电平分别趋向于VDD和0仿真结果显示,仅用一级放大的比较器增益可达52dB,最小分辨率达4mV,足以满足蓝牙射频电路可测性设计的要求。

DAC设计

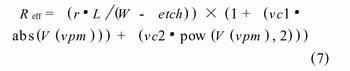

为了使电路尽可能的简单,本设计中DAC采用经典的R-2R梯形网络结构。由于整个ADC内嵌入蓝牙接收发送系统,电路的参考电压可由公共通道中的带隙基准源统一提供,这样既减少了ADC的功耗,又保证了精度.R-2R网络的最大缺点是由于工艺制作中存在的偏差,诸如杂质扩散,温度漂移等问题会使得电阻的阻值产生一定误差。通常多晶硅电阻可以做到较为精确,但由于在本工艺中该方块电阻只有2欧姆左右,会使得面积太大。而阱电阻虽然方块电阻很大,但精度较差。因此,在考虑面积和性能折衷的情况下,我们选用受工艺因素影响相对较小的P型扩散电阻,其方块电阻为153欧姆。单位电阻条宽取为5μm.该电阻受扩散腐蚀引起的误差可由下式计算:

式中etch,vc1和vc2都是工艺提供的参数。通过计算可知由工艺产生的电阻值绝对误差虽然有15%左右,但相对1μm或2μm的工艺,采用TSMC0.35μm的工艺,在5μm条宽的情况下,可以将相对误差做到±0.4%以内。同时,在版图设计时采用单位电阻及增加Dummy填充电阻的方法,可以有效地提高R-2R网络中电阻的匹配性,从而满足8位的精度要求。

ADC在蓝牙射频电路中的可测性应用

测试芯片是否符合设计规范有两种方法:即基于构成系统的独立模块级的测试和系统级的测试。本设计综合两者优点,将测试内嵌于接发器架构中,通过一个结构简单,实现容易的ADC,就可完成芯片部分功能的测试。

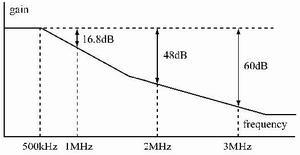

ADC的应用有两方面:第一用于检测各模块的直流工作点。在电路工作时,高频信号的干扰及其他因素会影响带隙基准源的准确性。一旦偏置电压或偏置电流不准,会直接导致各模块不能正常工作。通过ADC的多通道就能直接检测各模块的直流工作点。第二用于测试一些在高频情况下无法直接测得的性能参数,如信号幅度、噪声等。通过输入简单的激励信号,可以将被测参数转为直流电平,经模数转化后就可方便读出。例如可以用ADC检测蓝牙射频接收通道中的带通滤波器是否符合图3所示的蓝牙协议定义的滤波器的部分指标。将图中特殊点的信号幅度用直流电平表示,通过ADC的模数转换,就可以方便地观测到不同点的衰减是否符合要求。但是,在2MHz和3MHz频率时,信号幅度很小且很接近,给观测带来困难。这种情况可以通过调节自动增益控制,适当增加增益,使信号幅度增大且易于区分,但要求不能使ADC饱和。

图3滤波器性能

测试结果

图4是ADC的芯片照片,该芯片由0.35μm标准CMOS工艺制造,芯片面积是0.5mm×0.3mm.

图4ADC芯片照片

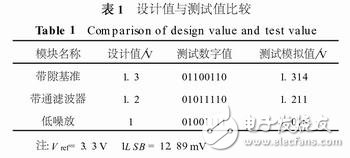

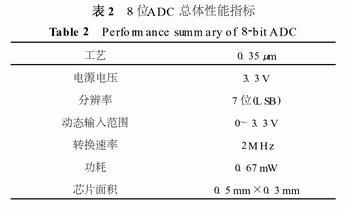

表1给出了蓝牙射频电路中带隙基准源,带通滤波器以及低噪放的理想直流工作电压与经ADC测试到的值,从中可以看到ADC的精度基本达到要求。表2给出了ADC的总体性能指标。

结论

本文设计了基于蓝牙射频电路可测性设计的8位逐次逼近型ADC.芯片测试结果显示,在3.3V工作电压下,ADC的分辨率可达7位。在设计中,输入级采用rail-to-rail结构,利用PMOS差分对和NMOS差分对并联的方法有效提高了电路的共模输入范围。通过对比较器电路和版图的优化设计使失调影响减到最小,大大提高了精度。针对可测性设计的要求,整个电路结构简单,易于实现,与同种功能ADC相比,芯片面积较小,仅0.5mm×0.3mm,功耗也较低。该ADC可以方便地内嵌入蓝牙射频电路的体系结构中,以用于检测各模块电路的部分功能与性能,这样的可测性设计,在使射频电路变得易于测试的同时,也大大减少了测试成本。由于在版图设计中较好地采用了隔离技术,电路在2.4GHz的高频环境下正常工作,表现出了良好的抗干扰能力。另一方面,测试结果显示ADC实际精度为7位,第8位在测试时跳动不确定,造成该结果的原因可能是由于参考电压对地有一定波动并且比较器的输入存在失调。在今后的工作中,将采用比较器的输入失调电压补偿等技术,使得电路和版图进一步优化,从而使结果更理想。同时,怎样更好地利用ADC进行蓝牙射频电路的可测性研究也将成为下一步研究的工作.

-

芯片

+关注

关注

457文章

51345浏览量

428262 -

射频

+关注

关注

104文章

5627浏览量

168330 -

蓝牙

+关注

关注

114文章

5884浏览量

171421

发布评论请先 登录

相关推荐

CSR BC05立体声蓝牙模块

如何利用DSP Builder设计一种适合于软件无线电使用的可控数字调制器

这种高密度工艺特别适合于 最小化导通电阻

如何设计一款适合于果园应用的激光雷达

适合于嵌入式系统的C语言单元测试框架是什么

基于蓝牙的远程控制方法的实现

NJR开发GaAs MMIC NJG1139UA2,适合于便

适合于温室控制系统的CAN总线应用层协议开发

适合于片上PWM模块的一种易于实现中心对齐SVPWM的方法详细概述

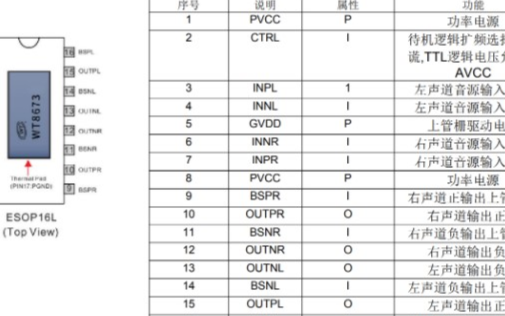

适合于蓝牙音响的功放芯片WT8673介绍

基于ADC适合于蓝牙射频电路的测试方法

基于ADC适合于蓝牙射频电路的测试方法

评论