由于具有较好的频带利用率和抗噪声性能,QPSK已成为一种在测控和通信领域广泛使用的数字调制方式。随着软件无线电的不断发展,直接中频数字解调已变得越来越容易,而时钟同步和载波同步是解调的关键问题。因而在全数字接收机中,同步过程通常通过算法在FPGA或DSP中实现,其通用性、互换性和移植性较强。

1 QPSK全数字接收机结构

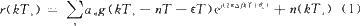

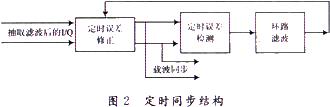

QPSK调制信号是抑制载波的信号,无法用常规的锁相环或窄带滤波器直接提取参考载波,但其载波相位变化只能提取有限的几个离散值,因而可通过非线性处理恢复载波信号,从而完成相干解调。图1是QPSK全数字接收机的框图,首先中频信号经抗混叠滤波后进入A/D变换器采样。在满足奈奎斯特采样定理的条件下,应尽可能提高采样率,以获得较高的采样信噪比,同时,模拟抗混叠滤波器也更易于实现。数字下变频将中频信号搬移至零频,得到基带的I(In-phase),Q(Quadrature)信号。由于采样率相对于信号带宽较大,因此需要进行抽取,降低数据率到一个合适的程度,以便于后续的信号处理。假设下变频及抽取后的复基带信号为:

其中,an是传输的数据,g(t)是系统脉冲响应,除去码元信息an后还存在3个未知参数:时钟误差ε,载波相位误差θ0和载波频偏△f。这3个参数的分布是随机的,只有恢复了这3个参数,an才能被正确地估计出来。

具体实现上要求解调的本振频率振荡在固定频率上而频差、相差和定时误差的消除通过同步算法在数字信号处理器中完成。

2 同步算法

2.1 定时同步

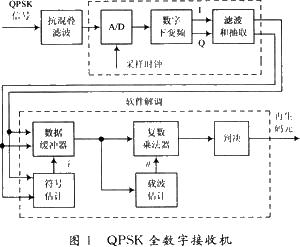

在载波同步和定时同步中,本文首先进行定时同步从而得到近最佳采样点,以减少随后进行的载波同步过程的计算量。也因为如此,使得定时同步时受到相位变化的影响,所以应选用对载波相位不敏感的定时同步算法,其结构如图2所示。

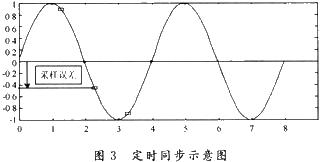

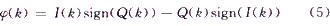

如图2所示,下变频后的数据经过滤波和抽取,I/Q两路信号速率已降到2倍码元速率,即1个码元2个采样点。而定时误差检测算法如下:

图3中,设星号位置为最佳采样点,1个码元2个点。其中奇数位置是峰值,偶数位置是中间点,即过零点。而图中的矩形点位置为实际的采样点,可知实际采样时钟滞后。式(2)用幅度上的误差来表示定时上的误差,根据式(2)即可提取得到误差信号。

得到的误差信号经过环路滤波即可反馈对I/Q两路进行修正。本文采取通过3点的二次插值运算,即抛物线插值得到近最佳采样点,此时I,Q两路1个码元只有1个采样点,从而有效地减少了后一阶段载波同步的计算量。

2.2 载波同步

硬判决型COSTAS环是算术运算和逻辑运算的方法,对正交解调输出的两路基带信号进行非线性处理,产生相位误差控制信号,通过环路滤波,控制载波恢复锁相环路。硬判决型COSTAs环具有入锁信噪比低,误码率性能好的优点,适合信噪比低的PSK信号的解调。

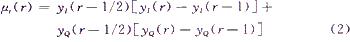

设经过定时同步后的I,Q两路信号分别为:

式中,△φ表示本地载波和接收信号的相位差,包括式(1)中的θ0以及由载波频偏△f产生的相位差。然后经过鉴相器得到相位误差,如式(5)所示:

鉴相曲线如图4所示,其中横坐标为弧度。

鉴相得到的相位误差接着进行环路滤波,在定时同步时选用的是一阶的滤波器,而载波同步时采用了二阶环路。将得到的误差估计值与经过定时同步的信号进行复数乘法以消除相位差的影响。但是这样估计得到的结果存在四维相位模糊度,需通过差分编译码消除。

3 计算机仿真

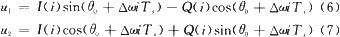

在Matlab中,系统首先生成PN 9的伪随机码作为基带信号。进行格雷码的预差分编码,上下变频后得到正交和同相两路基带信号:

其中频偏和初始相差在仿真中给定,通过算法来估计。

信道中的噪声通过与随机序列相加引入,用随机序列代表高斯带限白噪声,该序列与一系数相乘,通过调整系数改变噪声的大小,实现不同的信噪比。

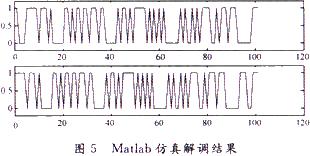

采样时,每个码元取6个样点,经过3倍抽取后每个码元为2个采样点,然后由上述算法内插出近最佳采样序列。再用复数乘法消除掉估计出的相位误差后进行判决和差分解码,最后得到码元信息。

图5分别为式(6)中的I(i)和针对他恢复出的数据,整个序列只是在时间上有一定的延时,上述算法较好地实现了数据的恢复。

4 硬件实现

4.1 VHDL设计和仿真验证

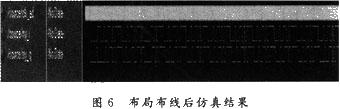

完成算法系统的全精度仿真后,使用ISE PrOjectNavigator对上述QPSK的全数字解调算法进行VHDL编程,综合(使用ISE自带的XST综合工具),实现(包括转换、映射、布局布线和时间参数提取),以及功能仿真和时序仿真。

为方便观察输出结果正确与否,将基带I,Q数据设计为重复周期为15的相同数据,时间上相差一个时钟周期。用Matlab计算出I,Q调制后的QPSK信号,保存为二进制文件,作为功能和时序仿真的输入文件。图6是布局布线后的时序仿真结果,最上一行为60 MHz采样时钟,下面两行是解调后的I,Q数据,数据率为10 MHz。

从图6中可以看出,经过同步后,解调后的I,Q数据是正确的,从而证明VHDL设计是成功的。

4.2 FPGA硬件电路验证

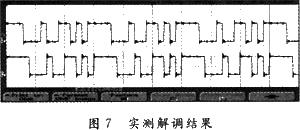

硬件方案的具体实现中,高速信号处理板包括A/D采样芯片AD6645(最高采样率为65 MHz,14 b),时钟分配器CY2305,Virtex-II Pro FPGA XC2VP70和配置用的PROM(XCf32P)。微波源4438C产生中频105 MHz、比特率20 Mb/s的QPSK信号,I,Q数据格式同上。任意波形发生器输出60 MHz的正弦波信号作为A/D的采样时钟。用54622D示波器观察高速信号处理板输出的解调后的I,Q信号。

使用PrOject Navrigator生成下载用的.mcs.和.bit文件,将他们下载到FPGA和PROM中进行实际测试。图7是实际观察到的I,Q数据,从中可以看出,对宽带QPSK信号的解调是正确的。

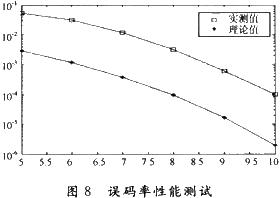

图8是系统的误码率性能测试,当信噪比大于8 dB时,实测值与理论值之间有大约2 dB的差,这主要由于系统前端滤波器不匹配,进入系统的噪声带宽比信号带宽大得多,影响了系统性能。对滤波器的改进将有利于系统性能的改善。

5 结 语

本文首先介绍了QPSK信号的构成,指出同步技术是QPSK信号解调的主要任务。在此基础上,与现有成熟算法相结合,针对高码率QPSK信号提出一种计算量小,易于实现的同步方法,他采用数字转换跟踪环和COSTAS环实现同步。计算机仿真及实测结果表明,该方法是可行的,适合FPGA实现。

-

通信

+关注

关注

18文章

6029浏览量

135957 -

变换器

+关注

关注

17文章

2098浏览量

109274 -

无线电

+关注

关注

60文章

2141浏览量

116450

发布评论请先 登录

相关推荐

高码率QPSK信号的构成及实现同步的方法介绍

高码率QPSK信号的构成及实现同步的方法介绍

评论