跳频通信技术是一种扩频技术,也是最常用的一种扩频抗干扰技术,通过载波频率在一定的范围内按某种序列进行跳变,使信号频谱得以扩展,以抑制信道中的干扰。跳频频率合成器是实现跳频通信的核心部件,它直接关系到跳频通信的性能,其主要指标有相位噪声、锁定时间、跳频带宽、频率数目等,其中又以相位噪声和锁定时间最重要,他们直接关系到跳频系统通信质量和抗干扰能力。

1 锁相环频合器相位噪声的分析

1.1 锁相环(PLL)频合器各功能部件相位噪声的估算

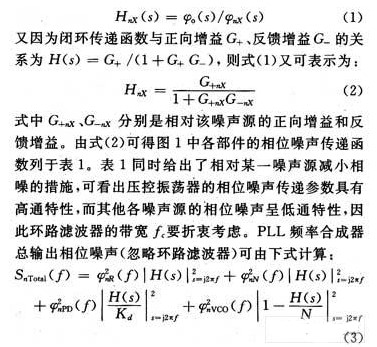

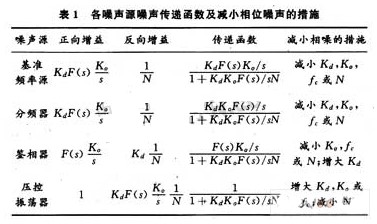

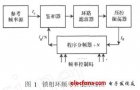

PLL频合器各功能部件对相位噪声均有贡献。分析和估算各部件对总相位噪声影响的方法是利用锁相环线性时不变模型,把各个功能块看成无噪声,并将噪声信号加到PLL各功能块的求和节点,如图1所示。假定各噪声源是独立的,先求出每一部件在输出端的相位噪声,再利用叠加法确定PLL频合器输出端总的相位噪声,且在求某一噪声源影响时,令其他噪声源输出为零。各部件在输出端相位噪声是通过各自的传递函数来求得的。如设某一相位噪声源为φnX,输出相位噪声为φo(s),则φnX到输出端的传递函数为:

1.2 PLL频合器相位噪声仿真

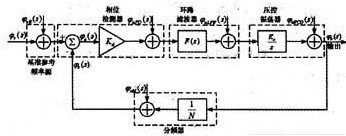

我们利用ADS仿真软件,验证上述分析得出的结论。采用电荷泵三阶无源环路滤波器,设定电路的原始参数为环路带宽10 kHz,Kd=1/10π,Ko=1 MHz/V,分频比为1 000。为了分析环路参数变化对输出相位噪声的影响,首先根据原始数据进行仿真,然后分别改变其中的某一参数,仿真变参数后对系统输出的影响。

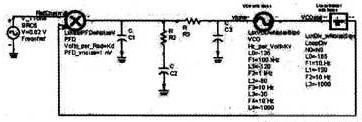

仿真电路如图2所示,仿真结果见图3,图中设频标m1~m7,分别对应频率1 Hz,100 Hz,1 kHz,100 kHz,1 MHz和10 MHz。

仿真结果中变参数数据与原始数据比较:在环路带宽内(频标m1~m3),N的增加增大了相位噪声,Kd的增加减少了m2~m3处的相噪,而Ko的增加对带内的相噪影响不大;在环路带宽外,Ko的增加增大了m4~m6处的相噪,Kd和N的增加对相位噪声没什么影响(m4~m7处);环路带宽fc增加一倍,则增加了m4~m7的相噪,而fc减少一倍,则减少了m4~m6处的相噪。

2 锁相环频合器锁定时间的分析

锁定时间与环路带宽成反比,带宽越大,锁定时间越短,系统跟踪性能越好。分析锁定时间,首先要得出环路滤波器的传递函数。对于图2中电荷泵三阶无源环路滤波器,其传递函数形式为:

3 S波段宽带快速跳频频合器的实现

3.1 技术指标及方案选择

跳频频合器主要技术指标:输出频段S波段,频带范围500 MHz;频率转换时间<120μs;相位噪声在偏离载波1 kHz,10 kHz,100 kHz处分别小于-70 dBc/Hz,-80 dBc/Hz,-90 dBc/Hz。

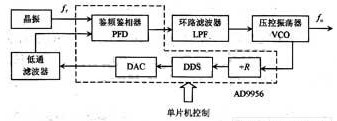

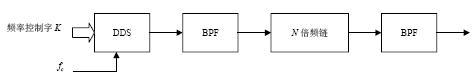

我们采用了DDS分频的PLL组合频率合成器技术方案,选用ADI公司的AD9956芯片,该芯片集成了DDS与PLL两部分,DDS作为频合器中的分频器,内部时钟频率可达400 MSPS,14位的D/A转换器,48位的频率调制字,PLL RF分频器输入频率范围1~2700 MHz,设计方案见图4。

3.2 频合器相位噪声及锁定时间可行性论证

3.2.1 输出总相位噪声可行性的分析

由PLL频合器基本工作原理可知,频合器环路带宽内相位噪声与基准频率源、鉴频鉴相器噪声基底、分频器输出信号有关,而带外的相噪与VCO有关。

AD9956芯片的相位噪声来自鉴频鉴相器噪声基底和DAC输出的相位噪声,这里DAC输出信号为PLL频合器分频器的输出信号。AD9956的鉴频鉴相器噪声基底在工作频率为50 kHz,2 MHz,100 MHz,200 MHz时分别为-149 dBc/Hz,-133 dBc/Hz,-116 dBc/Hz,-113 dBc/Hz;AD9956中DAC输出频率为51.84 MHz时,偏离载波10 Hz,100 Hz,1 kHz,100 kHz,>1 MHz处的相位噪声分别为-119 dBc/Hz,-125 dBc/Hz,-132 dBc/Hz,-142 dBc/Hz,-150 dBc/Hz,-155 dBc/Hz。由于DAC具有低相位噪声性能,基准频率源通常又采用稳定度高、相位噪声低的晶振,所以频合器带内相位噪声主要取决于AD9956中鉴频鉴相器的噪声基底,其理论计算值由下式得到:

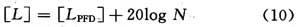

式中[?]表示对数值,N为系统的分频比,[LPFD]为所使用鉴相频率噪声基底的分贝数。设鉴相频率为25 MHz,可推算噪声基底-122 dBc/Hz,设N=92,因此由式(10)得带内相位噪声为:

根据理论计算值,如选择合适的环路带宽是能满足指标要求的,但由于频率高、频带宽,且要考虑获得快速锁定的大环路带宽,因此满足指标的相位噪声富裕量不大,在器件选择、PCB设计时要周密考虑,尽量达到理论计算值。

3.2.2 跳频锁定时间可行性分析

跳频锁定时间的估算包括DDS的频率转换时间、PLL转换时间以及控制电路的转换时间。DDS的频率跳变时间与PLL转换时间和控制电路转换时间比起来要小得多,因此可以忽略。

PLL频率转换时间与环路状态有关。采用电荷泵三阶无源环路滤波器,设环路带宽fc=100 kHz、频率容忍度ε=500 kHz,利用式(9)可得跳频间隔500 MHz时的频率转换时间为28μs。

AD9956的状态和频率控制字采用串行方式输入,要对32 b功能控制寄存器CFR1、40 b功能控制寄存器CFR2、64 b频率控制寄存器PCR0和各自的8 b地址信息,总共写入160 b的有用信息。为了减小系统复杂度,使用单片机产生的时钟,在每次对AD9956写入1 b有用信息时,需要三个周期的时钟控制,160 b有用信息就需480个时钟周期,计算频率控制字和单片机控制需要40个时钟周期,合起来一次跳频控制需要520个时钟周期。如单片机采用8 MHz晶振作为时钟,控制电路的转换时间为:

如果提高时钟频率,可进一步减小控制电路的转换时间。因此合理的选择环路中有关参数,锁定时间是能达到指标要求的。

3.3 测试结果

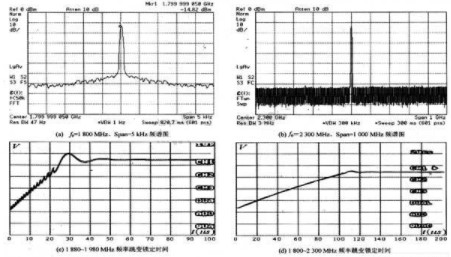

相位噪声的测试结果:在工作频率范围内,偏离载波1 kHz,10 kHz,100 kHz时的相位噪声分别小于-73 dBc/Hz,-81dBc/Hz和-93 dBc/Hz,且整个输出频带内杂散输出均小于-70 dBc。图5(a),图5(b)分别示出了f0=1 800 MHz,f0=2 300 MHz时的相位噪声测试频谱图,从图5(b)可看出在1 000 MHz的频率范围内对杂散的抑制很好。

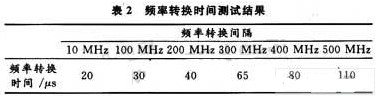

频率锁定时间测试结果:工作频率范围内最大的频率跳变(500 MHz)锁定时间为110 μs,表2示出了测试结果。图5(c),图5(d)分别示出了频率跳变范围为1 880~1 980 MHz,1 800~2 300 MHz VCO测量电压的变化曲线。

4 结语

跳频频率合成器设计和制作的重点之一是要解决频率捷变快速锁定的问题,文章对锁相环频合器的相位噪声和锁定时间进行了分析,并进行了仿真;采用基于DDS分数分频的锁相环频合器方案,实现了S波段宽带跳频频合器。试验结果表明,采用该方案的频率合成器频率转换速度快、相噪低、频谱纯度高,同时满足低功耗、小型化要求,验证了该方案的合理性和实用性。

-

噪声

+关注

关注

13文章

1122浏览量

47407 -

仿真

+关注

关注

50文章

4080浏览量

133587 -

pll

+关注

关注

6文章

776浏览量

135152

发布评论请先 登录

相关推荐

PXI 3010艾法斯频率合成器

基于锁相环CD4046的跳频频率合成器设计

锁相环频率合成器关键指标和优化方法

跳频频率合成器的性能指标及仿真分析

跳频频率合成器的性能指标及仿真分析

评论