近年来,红外探测系统因其具有隐蔽性,抗干扰性,全天候工作等特点,在现代战争中具有重要的作用,而红外图像中小目标的检测将直接影响制导系统的有效作用距离及设备的复杂程度,在红外成像制导和预警系统中发挥着举足轻重的作用。研究红外辐射的产生、传播、转化、测量及其应用的技术科学。通常人们将其划分为近、点击此处添加图片说明中、远红外三部分。近红外指波长为0.75~3.0微米;中红外指波长为3.0~20微米;远红外则指波长为20~1000微米。在光谱学中,波段的划分方法尚不统一,也有人将0.75~3.0微米、3.0~40微米和40~1000微米作为近红外、中红外和远红外波段。另外,由于大气对红外辐射的吸收,只留下三个重要的"窗口"区,即1~3微米、3~5微米和8~13微米可让红外辐射通过,因而在军事应用上,又分别将这三个波段称为近红外、中红外和远红外。

一般说来,由于小目标距离较远,因而在成像系统中表现为微弱特性,并且没有形状和结构特征或特征不明显。同时,由于高于绝对零度的物体均有红外辐射能力,所以自然界中的干扰源很多,很难准确地检测出真正的目标。

本文在数学形态学Top-hat算子对于目标检测的基础上,设计了一种基于DSP+FPGA的图像实时处理系统,使其能够满足高速采样数据流快速存取,快速运算的要求。

1 算法基础

1.1 形态学算法

数学形态学(Mathematical Morphology)诞生于1964年,是由法国巴黎矿业学院博士生赛拉(J. Serra)和导师马瑟荣,在从事铁矿核的定量岩石学分析及预测其开采价值的研究中提出"击中/击不中变换", 并在理论层面上第一次引入了形态学的表达式,建立了颗粒分析方法。他们的工作奠定了这门学科的理论基础, 如击中/击不中变换、开闭运算、布尔模型及纹理分析器的原型等。数学形态学的基本思想是用具有一定形态的结构元素去量度和提取图像中的对应形状以达到对图像分析和识别的目的。数学形态学方法是一种非线性滤波方法,它最先被用来处理二值图像,后来被引用到灰度图像处理。基本思想是:用一定的结构元素去度量和提取图像中的对应形状,去除不相干的结构,以达到图像分析和目标识别的目的。

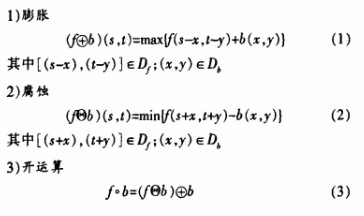

灰度形态学的基本运算有膨胀、腐蚀、开运算和闭运算。基于这些运算,可以推导和组合各种数学形态学使用算法。

设f(x,y)为输入图像,b(x,y)为结构元素,其中(x,y)为图像平面空间的坐标点,f为(x,y)点的灰度值,b为(x,y)点的结构函数值,Df和Db分别是f和b的定义域,上述4种基本运算的表达式为:

其中,开运算有些像非线性低通滤波器,但是又与低通滤波器不同,开运算可以允许高频部分中大于结构元素的部分通过。Top-hat算子就是利用了开运算的上述性质来进行目标检测的。

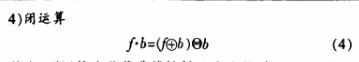

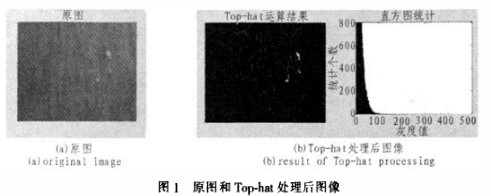

Top-hat算子的定义为:

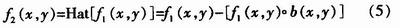

经过Top-hat处理后的图像,目标和背景在能量上差别较大,大部分像素都集中在低灰度区,只有目标和小部分噪声分布在高亮度区,如图1所示,图1(a)为原始图像,图1(b)为经过Top-hat处理的图像及其直方图统计结果。

1.2 最大类间方差法求阈值

阈值就是临界值,在PS中的阈值,实际上是基于图片亮度的一个黑白分界值,默认值是50%中性灰,既128,亮度高于128(<50%的灰)白既会变白,低于128(>50%的灰)的既会变黑。[可以跟滤镜中的其它――高反差保留,再用阈值效果会更好。]

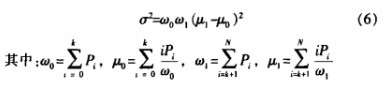

设经过处理后的图像f2(x,y)的各灰度的集合为S={0,1,2,…,N},Pi为此集合中i出现的概率,由于图像是由小目标和背景两部分组成的,设这两部分对应的灰度子集分别为:红外背景,C0={0,1,2,…,k};目标对象,C1={k+1,k+2,…,N};则两个类别的间方差为:

为节约程序运行时间,选取k的取值范围为[μ+5σ…N],其中μ为整幅图像的均值,σ为整幅图像的平均差,直到找到使类间方差取最大值时的k值,即为最佳分割阈值th.

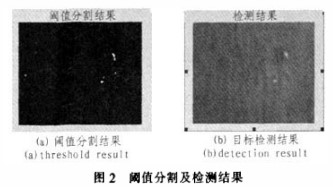

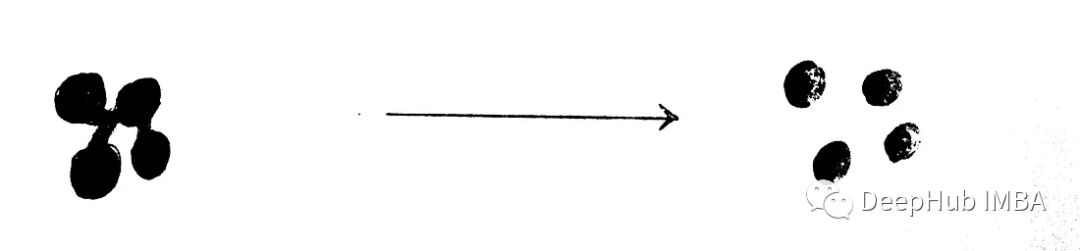

对经过Top-hat处理后的图像,利用上述的最大类间方差法获取阈值,利用这个阈值对图像进行分割,最后通过判断目标的形状大小,以达到提取目标的效果,如图2所示,图2(a)为阈值分割的结果,图2(b)为最终判断结果。

2 硬件系统结构

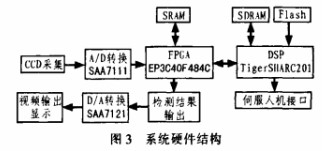

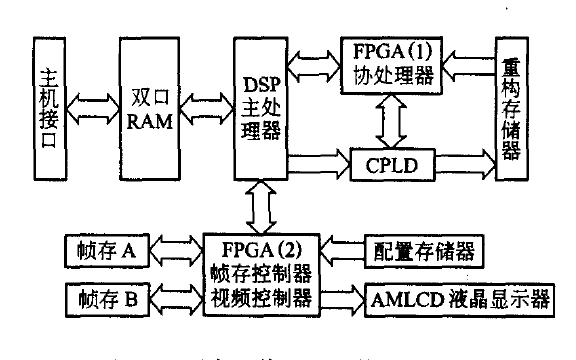

在实时视频处理系统中,底层算法的数据量大,运算结构相对比较简单,对速度有很高的要求,而高层处理算法控制结构复杂,数据量较底层算法少,故本文采用FPGA+DSP的结构。利用DSP实现目标检测的算法,数字信号处理(Digital Signal Processing,简称DSP)是一门涉及许多学科而又广泛应用于许多领域的新兴学科。20世纪60年代以来,随着计算机和信息技术的飞速发展,数字信号处理技术应运而生并得到迅速的发展。数字信号处理是一种通过使用数学技巧执行转换或提取信息,来处理现实信号的方法,这些信号由数字序列表示。在过去的二十多年时间里,数字信号处理已经在通信等领域得到极为广泛的应用,可以提高运行速度及便于调试和修改,FPGA实现整个系统的控制和图像的基本预处理功能。整个系统的硬件结构如图3所示。

在系统设计中,DSP采用ADI公司通用浮点型TigerSHARC201,它拥有非常高的存储宽度,支持32位和扩展的40位浮点运算,支持8、16、32、64位定点运算。它拥有高达600 MHz的内核时钟速率,一个周期可以执行4条指令,相当于24次16 bit定点操作或者6次浮点操作。处理器的运算流水是双周期的,分支流水为2~6周期,鉴于此流水深度,它使用分支目标缓冲(BTB)来减少分支延迟,其两个相同的计算单元均支持浮点和定点运算。

FPGA(Field-Programmable Gate Array),即现场可编程门阵列,它是在PAL、GAL、CPLD等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。FPGA采用Altera公司的EP3C40F484C对视频信号进行预处理和整个系统的时序控制,它具有多达24 624个逻辑单元,具有129个兼容的LV-DS通道,每个通道数据率高达640 Mb/s,还有4个可编程锁相环和8个全局时钟线。另外此芯片的功耗较低,全局运行时总功耗为300 mW左右。

2.1 视频输入和输出模块

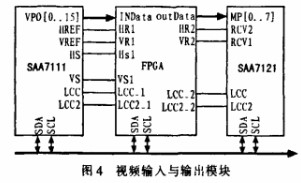

采用解码器SAA7111将摄像头输出的模拟视频信号转换为数字信号。编码器(encoder),是一种输入模拟视频信号并将它转换为数字信号格式,以进一步压缩和传输的硬件/软件设备。像视频的mpeg4,音频的mp3,ac3,dts等,这些编码器可以将原始数据压缩存放,刚才都是常用的编码格式,还有些专业的编码格式,一般家庭基本不会用到。为了在家用设备或者电脑上重放这些视频和音频则需要用到解码软件,一般称为插件。解码器是一个重要前端控制设备。在主机的控制下,可使前端设备产生相应的动作。解码器,国外称其为接收器/驱动器(Receiver/Driver)或遥控设备(Telemetry),是为带有云台、变焦镜头等可控设备提供驱动电源并与控制设备如矩阵进 解码器(Decoder)

行通讯的前端设备。通过配置SAA7111将PAL制式的模拟基带信号转化为CCIR-656格式的UYVY信号,并将其送入FPGA中,进行预处理。具体连接如图4所示,VPO[0…7]没有数据输入,VPO[8…15]是数据输出管脚与FPGA相连,时钟同步信号TS201采用MDMA的方式将原始图像信号存入SDRAM中,供目标检测算法使用。视频输出模块采用视频编码器SAA7121,标准的UYVY数据从FPGA的引脚输出,送到SAA7121的数据引脚,场、行同步信号分别接到FPGA的控制引脚上,通过行、场信号的控制,就能够输出显示正确的视频图像。在SAA7111和SAA7121工作之前,都需要对这两个芯片进行配置,它们的配置的参数都是通过FPGA产生I2C总线来实现的。

2.2 存储模块

TS201的片上存储器分为两个部分:每个内核各使用100 KB的专用、高速L1存储器;128 KB的大容量共享L2存储器。通过EBIU接口外扩SDRAM和Flash两种存储器。选取2片MT48L32M16A2来构成SDRAM存储器,图像处理数据和图像处理中间结果可存储在SDRAM中。系统扩展64 MB的Flash,选用S29GL064M90T,主要存放DSP内核程序。

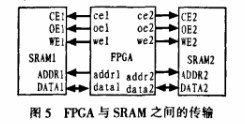

FPGA的存储系统:选取2片IS61LV10248来构成SRAM存储器,主要用于存储从SAA7111传输到FPGA的数据,根据视频数据的奇偶场的关系,在数据的存取过程中采用乒乓存取方式,当SRAM1存储数据的时候,FPGA从SRAM2读取数据,传给SAA7121做为显示使用,当SRAM2存储数据的时候,FPGA从SRAM1读取数据,传给SAA7121做为显示使用,同时通过对读时钟和读范围的控制,可以控制图像的现实范围和现实方式。具体硬件连接结构如图5所示。

2.3 DSP双核以及FPGA之间的通信

在本系统中,涉及到TS201两个核之间的通信以及TS201与FPGA之间的通信。FPGA给DSP提供预处理之后的图像数据,DSP根据提供的图像数据进行目标检测算法,并将检测之后的坐标数据传输到FPGA,FPGA将坐标信息叠加到原始图像后送给SAA7121显示。常见的双核通信主要采用中断、轮询两种通信方式。中断是利用两个核的中断机制来实现FPGA与DSP之间的通信;轮询是通过在双核的共享寄存器里设置一些信号量,供双核通信与访问。考虑到本系统的应用条件,采用轮询的通信方式,DSP的异步存储器的地址空间映射到FPGA,通过FPGA操作数据线和地址线,即可完成FPGA与DSP之间的数据交互。

2.4 系统工作流程

整个系统的工作流程为:由CCD采集视频模拟信号,经过可编程视频解码处理器SAA7111解码后输出场同步、行同步、像素时钟和位宽为16 bit的数字图像信号,并将信号送入FPGA中,在FPGA中对送来的数据做缓存,预处理,再通过与TS201连接的双向LINKPORT,把图像数据实时地导入DSP中,在DSP中运行检测算法,得到被检测目标的正确坐标,DSP把目标的坐标信息返回到FPGA中,FPGA根据坐标信息在原始图像上标示出目标的位置,最后将处理后的图像信号传给可编程视频编码器SAA7121进行编码实现D/A转换,输出模拟视频,并把检测结果显示在视频显示设备上。

3 结论

首先研究了形态学Top-hat算子,并利用Top-hat算子进行背景抑制,同时,采用最大类间方差法获得图像的阈值,分割背景和目标,实现小目标检测,通过仿真实验发现,这种方法能够在一定程度上减少实际检测中的虚警率,增加目标检测的准确性。

利用DSP+FPGA的系统架构设计了实现算法的硬件平台,这种结构在一定程度上可以满足实时性和灵活性的要求,具有很强的通用性和可扩展性。并在设计中采用了模块化设计,这样的设计便于集中控制,能够节省程序运行时间。

-

处理器

+关注

关注

68文章

19342浏览量

230227 -

dsp

+关注

关注

553文章

8030浏览量

349319 -

FPGA

+关注

关注

1629文章

21754浏览量

604234

发布评论请先 登录

相关推荐

在数学形态学基础上实现DSP和FPGA的红外图像检测系统

在数学形态学基础上实现DSP和FPGA的红外图像检测系统

评论