随着计算机、多媒体和数据通信等技术的高速发展,对计算机音视频的需求和应用越来越多,如视频监控、视频会议等。计算机音视频提供给人的信息很多,但其数据量很大,不利于传输和存储,从而使其应用受到不少限制。为解决音视频数据的存储和传输,唯一的途径就是对音视频数据进行压缩。

基于Z1510专用音视频压缩芯片设计的具有USB接口的实时MPEG-1音视频压缩卡,较传统的PCI接口的MPEG-1音视频卡具有支持热插拔和即插即用等特点,同时该系统还具备很好的可扩展性。本文就来介绍这个系统的设计与实现。

1 硬件设计

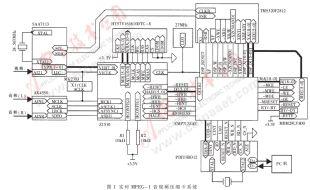

本系统主要由音视频A/D转换单元、音视频压缩单元、系统控制单元和UBS接口单元四大部分组成,如图1所示。模拟音视频信号经AK4550、SAA7113音视频A/D转换器后送入Z1510音视频压缩芯片,压缩编码后生成的MPEG-1码流经USB端口输出。整个压缩系统的控制由TMS320F2812和EPM7128AE共同完成,压缩后的数据通过USB接口芯片PDIUSBD12输出。

1.1 音视频压缩部分的电路设计

本系统中的MPEG-1压缩芯片选用以色列Emblaze Semiconductor公司的Z1510。Z1510是一款高性能低成本的音视频压缩编码芯片,它可完成MPEG-1音视频压缩、MJPEG视频编码以及全分辨率静态图像捕获,还可对CD-ROM和VCD进行格式化。Z1510压缩芯片有三种系统配置(Master、Direct-data、Indirect-data),总共有20余种工作模式,不同的工作模式可通过加载不同的代码来实现。

Z1510的音视频输入是通过视频端口和串行接口完成的。视频输入端口主要接收视频A/D转换器产生的ITU-R BT.601或ITU-R BT.656格式的数字视频信号和相应的时钟同步信号。Z1510有五个串行端口,包括三个输入端口(Audio0、Audio1和CD-Drive)和两个输出端口(CD-Drive和SVCD decoder),每一个端口均可作为主设备端口和从设备端口,本系统中应用的Audio1端口作为主设备端口,接收未压缩的数字音频信号,同时为音频A/D转换器提供相应的同步时钟信号。

Z1510的主时钟信号频率为稳定的27MHz,该时钟信号频率在芯片内部被PLL1倍频为81MHz,驱动Z1510的视频压缩内核及SDRAM。而PLL2连接到DSP内核,该PLL由软件配置PLL寄存器,工作在94.5MHz,用于音频压缩和系统数据流复合。系统主时钟由一个27MHz的晶体振荡器直接提供,该晶振同时也为EPM7128AE和TMS320F2812提供时钟信号。

在Z1510进行MPEG-1压缩时,它是工作在LAVE(Live Audio Video Encoding)模式。在此模式下,Z1510只能配置为间接工作(Indirect-data)状态,此时Z1510作为从设备,受主机控制,主机可以通过其HOST接口访问它内部的配置和状态寄存器,并且可以通过局部FIFO获得压缩后的视频码流。

Z1510的HOST接口的主要信号有:

·HAD[150] 数据总线;

·HCONFIG[9,8] 总线数据类型选择;

·HWR_N,HRD_N 读写控制,HCS_N器件片选信号;

·HALE在复用总线模式下,锁定低8位地址HAD[7~0];在非复用总线模式下,指示当前数据总线上发送的是寄存器地址还是寄存器数据。

·HINT_N 中断请求信号,低电平有效。

在存储空间分配中,Z1510分在TMS320F2812外部拓展存储空间(XINTF)的0区(0x00 2000~0x00 3FFF),因此需将HALE管脚在CPLD内部通过进位链与DSP的A0相连,而片选信号HCS_N需由A12、A13、A14、A15和DSP的信号经译码实现,HWR_N和HRD_N信号由A12、A13、A14、A15和DSP的信号经译码实现。

1.2 系统控制单元

本系统使用TI公司的TMS320F2812和Altera公司的MAX7000系列的EPM7128AE实现系统的管理和控制。TMS320F2812是基于TMS320C28xTM DSP内核的芯片,时钟频率高达150MHz,具有18K的SARAM和128K的片内Flash,另外还具有1M的外部扩展存储空间(XINTF)。TMS320F2812的外部扩展存储空间只可用作数据空间或程序空间,不支持I/O空间,它分为0、1、2、6、7五个区,没有DS、PS、IS三个信号线,取而代之的是三个区选信号,其中0区和1区共用一个区选信号,6区和7区共用一个区选信号,在设计中,由于SAA7113的片选信号直接拉高,而它的配置是通过TMS320F2812的GPIO模拟I2C总线实现的,因此不占用存储空间;Z1510的控制接口地址与数据复用和USB接口芯片PDIUSBD12一样,都只有一个地址位(占用两个位置);只有外界FLASH芯片MBM29LV800(512K×16位)占用存储空间较多,因此系统主要存储空间分配如下:

Z1510 占用Zone00x00 2000~0x00 2001

USB接口 占用Zone10x00 4000~0x00 4001

FLASH 占用Zone20x08 0000~0x0F FFFF

由于本系统采用专门的视频压缩芯片,CPLD主要完成一些逻辑仲裁、地址解码逻辑、控制信号的产生等,无需进行一些较复杂的运算,因而选用内核电压和I/O电压均为3.3V且具有128个宏单元的EPM7128AE来实现。

1.3 接口单元

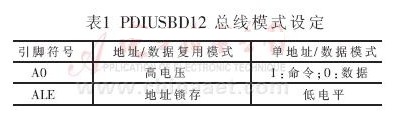

Z1510在进行标准的MPEG-1音视频压缩时,系统比特率一般在1.5Mbps以下。虽然最高速度12Mbps的USB1.1里的开销包括了命令包、帧标记和握手协议传输等,但仍可达2Mbps的系统比特率,可以满足系统设计需要。在综合考虑性价比后,选用了Philips公司的USB1.1接口芯片PDIUSBD12。PDIUSBD12看起来就像是一个带八位数据总线和一个地址位的存储器,它提供的微处理器接口可以兼容大部分的DSP环境,其接口信号包括八位数据线D0~D7和ALE、A0、、、、,USB控制器可以分为地址/数据复用模式或单地址/数据模式,如表1所示。DSP的数据地址总线是分离的,USB控制器采用单地址/数据总线模式更容易与DSP接口。

2 软件设计

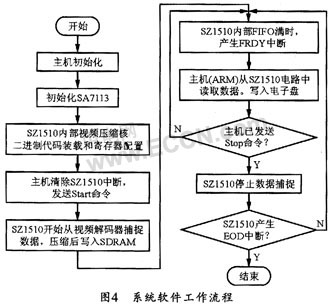

本系统的软件设计主要分两大部分:对硬件的初始化(SAA7113、Z1510)和PC机与系统的实时通信。系统上电后,由电源输出端的RC电路触发CPLD里的D触发器,对DSP进行复位,然后由DSP对其它器件进行复位和初始化。

2.1 硬件初始化

对SAA7113的初始化可通过将DSP的McBSP用作通用I/O脚模拟I2C总线来实现,DSP作为主器件,SAA7113作为从器件,用McBSP的CLKR模拟SCL,FSR模拟SDA。首先设置DSP的GPFMUX寄存器的相应位为0,使CLKR和FSR用作通用I/O脚;然后设置GPFDIR和GPFDAT寄存器的相应位以改变CLKR和FSR的输入输出方向和高低电平,GPFDIR.bit=0时为输入,相反为输出;GPFDAT.bit=0,同时引脚为输出时为低电平,相反为高电平。通过CLKR和FSR管脚的高低电平的变化和输入输出状态的切换可以实现I2C协议。SAA7113的初始化就是对寄存器配置合适的参数,使其能够有符合要求的输出。寄存器配置通过I2C总线来进行,很多可以控制I2C总线的器件都可以作为主器件对7113进行初始化,这里介绍用51单片机初始化7113的例子。

系统在开始工作之前,还要进行一个软复位过程。TMS320F2812先向Z1510的Soft_reset寄存器(地址0x08)写0x55,等待至少1微秒后,设置Int_enable [6]寄存器,使能RDY中断,等Z1510产生一个RDY中断后,清中断,完成软复位,开始代码加载。SAA7113是一种视频解码芯片,它可以输入4路模拟视频信号,通过内部寄存器的不同配置可以对4路输入进行转换,输入可以为4路CVBS或2路S视频(Y/C)信号,输出8位“VPO”总线,为标准的ITU 656、YUV 4:2:2格式。7113兼容PAL、NTSC、SECAM多种制式,可以自动检测场频适用的50或60Hz,可以在PAL、NTSC之间自动切换。7113内部具有一系列寄存器,可以配置为不同的参数,对色度、亮度等的控制都是通过对相应寄存器改写不同的值,寄存器的读写需要通过I2C总线进行。7113的模拟与数字部分均采用+3.3V供电,数字I/O接口可兼容+5V,正常工作时功耗0.4W, 空闲时为0.07W。7113需外接24.576MHz晶体,内部具有锁相环(LLC),可输出27MHz的系统时钟。芯片具有上电自动复位功能,另有外部复位管脚(CE),低电平复位,复位以后输出总线变为三态,待复位信号变高后自动恢复,时钟丢失、电源电压降低都会引起芯片的自动复位。7113为QFP44封装。

在Z1510内部寄存器有一段程序空间,这段空间以块为单位,每块的大小是256字节。其中,DSP核程序空间为0x280~0x2BF(64 banks),视频编码核的二进制代码的装载空间为0x000~0x004和0x00C等六个块。装载步骤如下:

(1)向Z1510内部寄存器0x2E写入0x01,表示外部的SDRAM是1M×16bit;

(2)向0x0C寄存器写0x03,使能FIFO Ready和End of Data中断;

(3)向0x11寄存器写0x18,设定工作模式为内部内存写模式;

(4)向0x10写0x20,设定Z1510的FIFO满为256字节;

(5)向0x08寄存器写0x04,发送开始命令;等待Ready中断,然后清除Ready中断;

(6)向Data _in寄存器0x01写256个字节数据;等待End of Data中断,然后清除中断;

(7)查程序空间的代码是否装载完毕,如没有,回到(5)继续装载。

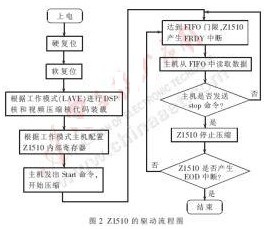

通过设定Z1510内部工作寄存器的特定状态可以使其工作在特定的模式,在本系统中设定Z1510工作在LAVE模式,在此模式下,Z1510从音频和视频A/D转换器获取数据并压缩为MPEG-1码流。Z1510正常工作后,输出MPEG-1码流。其输出码流要经过输出端口FIFO缓冲,每当FIFO写入超过半门限时,产生中断FRDY(FIFO Ready)通知DSP,DSP通过读寄存器DATA_out(0x00)取走数据,其半门限可由ThreshHold寄存器设定,最大256字节。FIFO满后,DSP连续读寄存器256次可以取走数据。Z1510的驱动流程见图2。

2.2 接口程序设计

在设计开发一个USB外设的时候,主要需要编写三部分程序:①固件程序;②USB驱动程序;③客户应用程序。固件编程主要完成PDIUSBD12的驱动,使DSP系统与外部系统进行数据交换。

在Win32系统中,每一个设备对象都抽象为文件。在应用程序设计中,只需通过几条简单的文件操作API函数,就可以实现与某个设备通信。主要使用的API函数有DeviceIOControl()、ReadFile()、WriteFile()。其中,DeviceIOControl()用于PC机(主机)向图像压缩系统发送请求;ReadFile()和WriteFile()分别用于从图像压缩系统中读出数据和写入数据。在设计过程中必须注意的问题是:由于USB接口是主-从方式的接口,它的一切传输都必须通过主机向外设发送请求后才能进行,所以在使用ReadFile()、WriteFile()读写数据之前,必须先通过DeviceIOControl()向图像压缩系统发送请求,系统接收请求后才能读写数据,开始进行音视频压缩。

该音视频压缩系统具有较好的功能扩展性,正如前面所介绍的,由于Z1510具有多种工作模式,在系统初始化时可根据所需工作模式加载不同的代码,对相应的寄存器进行不同的初始化,通过改变工作模式,可完成单独的视频压缩、音频压缩、静态非压缩或压缩图像获取(PC CAMERA)等多种功能。如再在系统中设计大容量FLASH,还可升级为独立的音视频压缩记录系统。

-

寄存器

+关注

关注

31文章

5363浏览量

121089 -

usb

+关注

关注

60文章

7979浏览量

265945 -

视频

+关注

关注

6文章

1956浏览量

73123 -

计算机

+关注

关注

19文章

7534浏览量

88594 -

PCI

+关注

关注

4文章

671浏览量

130451

发布评论请先 登录

相关推荐

【RTC程序设计:实时音视频权威指南】音视频的编解码压缩技术

基于ARM Linux的无线音视频对讲系统

怎么实现基于VW2005的MPEG-4音视频压缩卡的设计?

基于Z1510的音视频压缩卡的设计

基于LPC2210和SZ1510的车载数字视频压缩记录系统设

富瀚微电子FH8735的H.264音视频压缩卡方案

FH8735在音视频压缩卡上的应用设计

基于Z1510与A/D转换单元的音视频压缩系统的设计

基于Z1510与A/D转换单元的音视频压缩系统的设计

评论