1 引言

随着微电子技术和网络的发展,人们对网络的认识日益深入。网络终端产品也越来越受到人们的关注,嵌入式操作系统的应用也得到了前所未有的发展。PC104是一种嵌入式平台,它与IBM的PC机兼容,具有灵活的可扩展性,其小巧的尺寸非常适合嵌入式系统的应用。

本文基于PCM-3350型PC104嵌入式开发平台,最高采集速度可达1Msps,分辨率为12bit,能够进行通道扫描采集和单通道采集的数据采集系统。

2 数据采集系统设计

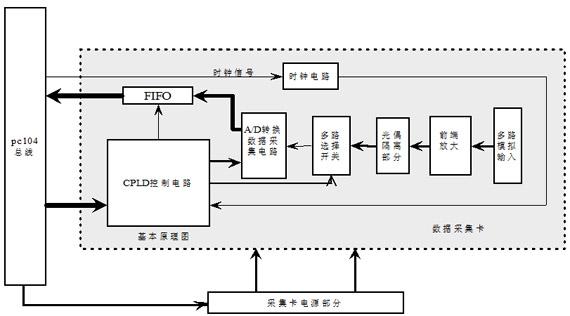

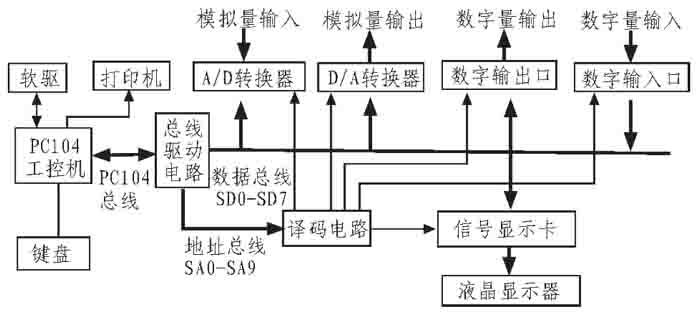

数据采集系统主要由放大电路、光藕隔离电路、带采样保持器的AD模数转换器、时钟电路、CPLD控制电路、数据缓存(FIFO)等部分组成,总结构框图如图1所示:

图1 总结构框图

2.1 A/D转换数据采集电路

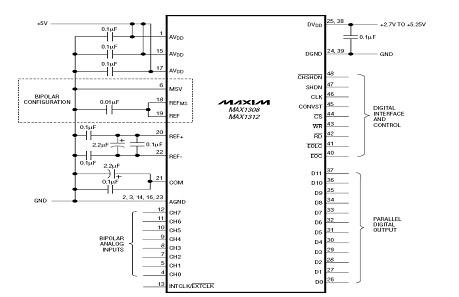

A/D转换选用max1308AD芯片,它是一种采样速率最高可达1Msps,分辨率为12bit的采集芯片,多达8个通道的同时采样,+5V模拟电源,+3V至+5V数字电源,其硬件系统连接如图2所示:

图2 max1308AD硬件连接

2.2 FIFO存储电路

FIFO电路芯片选用IDT公司的IDT7203,它是一个双端口的存储缓冲芯片,有2048×9 的存储结构,12ns 的高速存取时间,结构简单便于操作,内部读、写指针在先进先出的基础上可进行数据的自动写入和读出。

2.3 CPLD控制电路设计

CPLD(EPM7160STC100-6)的设计是本采集系统的核心,它能够对PC104地址总线进行译码,所产生的逻辑控制信号对各个单元的工作状态起控制作用。

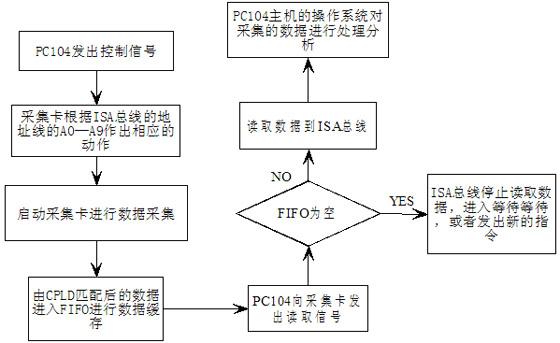

数据的读取可以采用查询的方式。在PC104 ISA部分,用到ISA的16位数据总线D[0..15]。A[0..9]是PC104的地址总线;IOW和IOR是对指定设备的读写信号;AEN是允许DMA控制地址总线、数据总线及读写命令线进行DMA传输及对存储器和IO设备的读写。系统工作流程如图3所示:

图3 系统工作流程

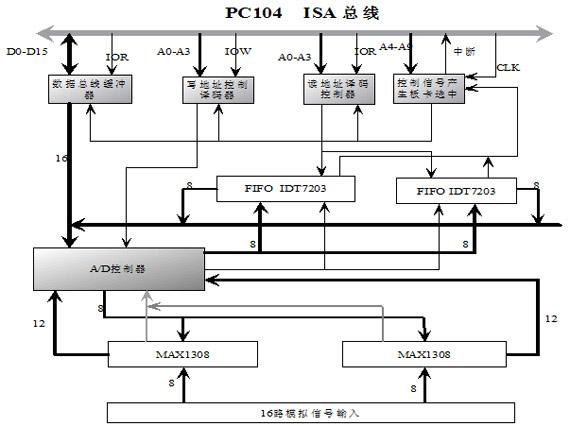

数据采集系统的工作逻辑框图如图4所示:

图4 数据采集系统的逻辑框图

其中,地址译码、控制器:只有地址选中该模块时,A/D 才能工作,同时使PC104工作在16位数据线方式,A0到A3分别控制着转换通道的选择;启动触发器和中断响应寄存器都位于状态控制器内部;读数据寄存器:当FIFO不为空,在FIFO中的转换结果直接进人数据总线,第12位到15位 由CPLD提供,使数据与其相等再进入16位数据总线,完成整个转换过程。

2.4 采集卡的地址分配

由于该数据采集卡是作为PC104的标准外设进行工作的。PC104规定,外设的操作地址为A[9:0],在系统软件设计中要防止地址冲突。PC104中使用A0~A9地址位来表示I/O端口地址,即可有1024个口地址,前512个供系统板使用,后512个供扩充插槽使用,当A9=0时表示为系统板上的口地址;当A9=1时表示扩充插槽接口卡上的口地址[2]。

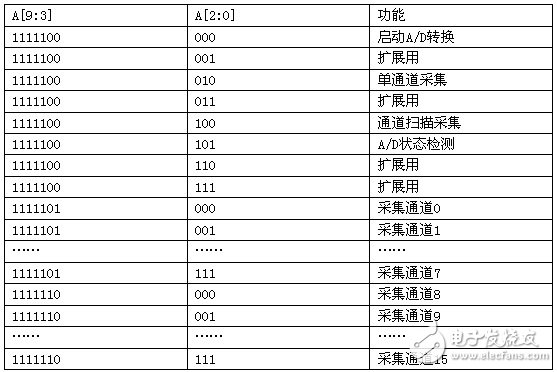

采集卡的基地址分配和译码地址分配见表1,本文设计的数据采集卡的地址范围是:2E0H—2F7H,不会发生地址冲突。

表1:数据采集卡的地址分配及译码

3 PC104平台

PC104平台硬件采用PC/104总线标准结构设计的产品PCM一3350主板。它是研华新一代高速低耗PC/104系列的代表产品。控制器模块包括一个主控32位微处理器单元,具有32MRAM和内置的非易失存储器用于数据和程序存储,提供VGA,LCD显示器接口;该模块还具有一系列标准通讯口从而提供多种通讯方式,包括串行通讯(RS232,RS485)、以太网等以及一个PC104总线接口。

4 软件设计

本系统中,根据固态盘的特点,操作系统软件采用DOS6.22,以TuborC 2.O作为开发环境,应用程序采用C语言和汇编语言相结合来实现除此在编写软件时,首先要设置好I/0板卡的基地址,再根据基地址来确认其他外围寄存器端口地址,包括读写端口、控制字和通道选择等地址。

5 结束语

数据采集技术是信息科学的重要组成部分,已广泛应用于国民经济和国防建设的各个领域,并且随着科学技术的发展,数据采集技术将有广阔的发展前景。本文基于PC104的嵌入式平台,采用MAX1308AD转换芯片,设计了一个16通道,最高采集速度可达1Msps, 分辨率为12bit的数据采集系统,由于其小型化易携带的特点,此数据采集系统可方便地用于野外作业。

-

嵌入式

+关注

关注

5105文章

19288浏览量

310203 -

存储器

+关注

关注

38文章

7557浏览量

164951 -

数据采集

+关注

关注

39文章

6485浏览量

114556

发布评论请先 登录

相关推荐

arm vs pc104

怎么设计基于PC104总线的实时信号采集处理系统?

基于Paradigm IDE 开发PC104 嵌入式系统的RAM 配置方法

基于Paradigm IDE 开发PC104 嵌入式系统的R

基于PC104 的数据采集系统的研究与实现

基于PC/104总线的数据采集系统设计及应用

TurboC在嵌入式PC/104系统中的应用

Windows CE下PC104模块与MCS51单片机串行通

一种基于PC104的实时姿态数据采集系统的设计与实现

PC104数据采集与检测电路实现改进投弹装备故障检测方法

采用PC/104嵌入式系统平台实现实时姿态信息采集系统的设计

基于PC104嵌入式平台的MAX1308AD数据采集系统设计与实现

基于PC104嵌入式平台的MAX1308AD数据采集系统设计与实现

评论