在NiosⅡ系统的构建过程中,SoPCBuilder开发环境集成了许多常用类型的设备模型,供开发者调用。在日新月异的嵌入式系统设计中开发环境所集成的接口设备是非常有限的,有时无法满足开发者的需要,SoPCBuilder开发工具允许用户依据规则扩展自己的所需设备,完成系统的设计和开发,开发者按照Avalon总线规范将设备驱动程序集成到SoPCBuilder的硬件抽象层(HAL)中,在SoPCBuilder环境下加载使用,方便了用户开发一个自定制的片上系统。本文通过在NiosⅡ嵌入式系统内部集成了基于Avalon总线的脉冲宽度调制(PWM)从外设,介绍了自定制Avalon设备的过程。将其应用在嵌入式智能小车监控系统,为采用NiosII处理器的开发者提供了一些方法和建议。

1、定制基于Avalon总线的用户外设介绍

NiosⅡ的Avalon总线不同于其他微处理器的固定外设,NiosⅡ的外设是可以任意定制的,这使得用户可以根据具体的应用需求而定制。所有的NiosⅡ系统外设都是通过Avalon总线与NiosⅡ软核相连,从而进行数据交换。因此对于用户定义的外设必须遵从该总线协议才可与NiosⅡ之间建立联系。

Avalon信号接口定义了一组信号类型片选、读使能、写使能、地址、数据等,用于描述主从外设上基于地址的读写接口。外设使用准确的信号与其内核逻辑进行接口,并删除会增加不必要开销的信号。

在NiosⅡ系统中一个自定义设备由如下几部分组成:

(1)硬件文件:用HDL语言编写的描述自定义设备元件逻辑的硬件描述文件。

(2)软件文件:用C语言编写的设备寄存器文件以及设备的驱动程序文件。

(3)设备描述文件(Ptf):本文件描述了设备的结构,包含SoPCBuilder配置以及将其集成到系统中时所需要的信息。本文件由SoPCBuilder根据硬件文件以及软件文件自动生成。

2、基于NiosⅡ系统的PWM设计

PWM是利用数字输出来对模拟电路进行控制的一种非常有效的技术,广泛应用于从测量、通信到功率控制与变换的许多领域中。实际上PWM是一种对模拟信号电平进行数字编码的方法,通过高分辨率计数器的使用,方波的占空比被调制用来对一个具体模拟信号的电平进行编码。PWM信号仍然是数字的,因为在给定的任何时刻,满幅值的直流供电或者完全有,或者完全无。电压或电流源是以一种通或断的重复脉冲序列被加到模拟负载上。通即是直流供电被加到负载上,断即是供电被断开。只要带宽足够,任何模拟值都可以使用PWM进行编码。

2.1硬件设计

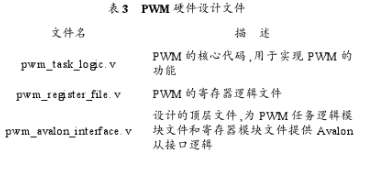

硬件文件指的是HDL文件,由以下几个模块组成:

逻辑模块:描述设备的逻辑功能;

寄存器映射模块:为内部逻辑模块和Avalon总线提供了通信接口;

Avalon总线接口模块:使Avalon总线访问寄存器从而完成相应的逻辑功能。

2.1.1逻辑结构

对于自定义的PWM也是由以上几部分模块组成。PWM按照以下要求设计:

(1)任务逻辑按一个简单时钟进行同步操作。

(2)任务逻辑使用32位计数器为PWM提供一个一定范围的周期和占空比,最大周期可设为232个clk。

(3)可以使用微控制器来设置PWM的周期和占空比的值,因此要提供一个可对寄存器进行读写的接口和控制逻辑。

(4)定义寄存器来存储PWM周期和占空比的值。

(5)微控制器可以通过控制寄存器的禁止位关闭PWM输出。

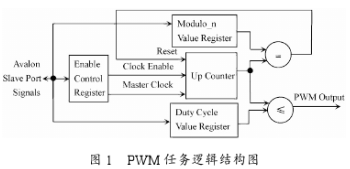

PWM任务逻辑的结构图如图1所示。

PWM任务逻辑由输入时钟(clock)、输出信号端口(pwm_out)、使能位、32位计数器以及一个32位比较电路组成。clk作为32位计数器的时钟信号,32路比较电路比较32位计数器的当前值与占空比设定寄存器(DutyCycleValueRegister)中的值来决定pwm_out的输出为高或低。当当前计数器中的值小于或等于占空比寄存器中的值时,pwm_out输出低电平,否则输出高电平。PWM周期设定寄存器(Modulo_nValueRegister)用来设置pwm_out的信号周期,当当前计数器的值等于周期设定寄存器中的设定时,产生一个复位信号来清除计数器中的值。使能控制寄存器(EnableControlRegister)能使时钟信号有效或无效,即控制计数器是否计数,从而保持pwm_out输出保持当前不变。

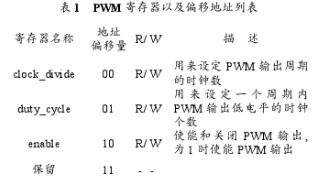

PWM内部包括使能控制寄存器(EnableControlRegister)、周期设定寄存器(Modulo_nValueRegister)以及占空比设定寄存器(DutyCycleValueRegister),如图1所示。设计中将各寄存器映射成Avalon从端口地址空间内一个单独的偏移地址。每个寄存器都能进行读/写访问,软件可以读回寄存器中的当前值。表1是PWM寄存器以及偏移地址列表。

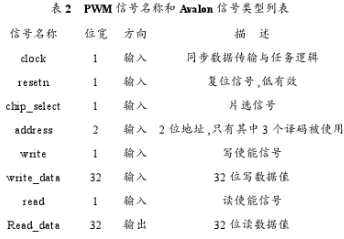

PWM的Avalon接口需要一个简单的从端口,该端口使用Avalon总线信号完成寄存器的读/写传输。PWM与Avalon总线接口所需的信号如表2所示。

图2中:clock_divide信号设定PWM输出周期的时钟数,dutv_cycle信号设定一个周期内PWM输出低电平的时钟个数,两个信号设定值决定PWM信号的占空比和周期。

2.2软件设计

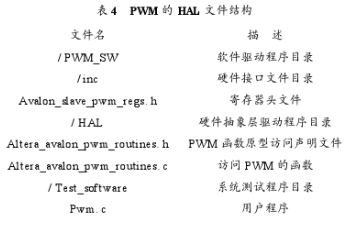

如果要使Nios软核能够访问自定义的设备,就必须根据先前的硬件设计按照硬件提取层的文件结构编写设备驱动程序。以PWM为例说明HAL的文件结构,如表4所示。

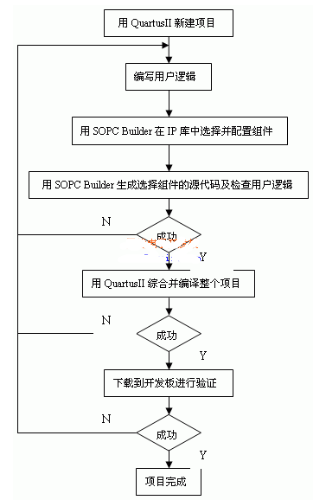

2.3将PWM设计封装为SoPCBuilder元件

当硬件文件和软件文件都已建立好后,便可以通过SoPCBuilder中带有的设备编辑器将自定义设备封装到开发环境内部,在构建NiosⅡ系统时可以对其直接调用。在SoPCBuilder中单击CreatNewComponent,创建新元件向导添加HDL文件、设置信号和接口添加软件,最终生成包含描述文件、用户存放硬件描述文件的文件夹以及用来包含HAL软件文件的HAL文件夹。

2.4构建Nios系统

构建好的内核文件在QuartusⅡ中编译,生成pof配置文件下载到E2PROM芯片中,接下来就可以使用NiosIDE开发环境编辑用户程序,以及通过JTAGBlaster或者USBBlaster在目标板上对应用程序进行调试。

3、自定制外设PWM在嵌入式智能小车监控系统中的应用

智能小车监控系统设计应用周立功公司SmartSoPC核心板,FPGA为Altera公司的EPlC12,NiosⅡ处理器作为嵌入式CPU,机器人车电机共有两个,左轮电机和右轮电机。该部分包括电机驱动电路和电机控制电路,即左电机的驱动与控制以及右电机的驱动与控制。驱动电路采用CTMicroelectronics公司的大功率直流电机驱动芯片L289,调速控制采用PWM来控制汽车的前进速度,由FPGA写入控制字,可得到不同占空比的PWM驱动信号,此PWM信号送人电机驱动芯片的控制端来调节速度。调用电机驱动程序,改变PWM占空比,输出PWM波,实现电机的速度控制。用PWM信号控制直流电动机速度,频率较低时,电动机不会稳定运转,频率较高时,PWM信号的驱动效率降低。经过多次实际电路的测试,调试结果显示当频率在500~1000Hz时,效果较好。部分C语言控制代码如下:

4、结语

NiosⅡ嵌入式处理器是用户可配制的通用RISC嵌入式处理器,是一个非常灵活和强大的处理器。基于此种技术的嵌入式系统设计可以方便地将一般设备和自定义设备模块集成到系统中,丰富了接口资源,从而能使用户快速地开发一个自定制片上系统,提高了效率,缩短了开发周期。本文通过自定制PWM外围设备的方法,并通过硬件测试证明了方案的可行性和正确性,希望能够为采用NiosⅡ处理器的开发人员提供一些方法和建议。

责任编辑:gt

-

处理器

+关注

关注

68文章

19349浏览量

230324 -

嵌入式

+关注

关注

5087文章

19149浏览量

306219 -

总线

+关注

关注

10文章

2891浏览量

88186

发布评论请先 登录

相关推荐

采用nios和μClinux实现嵌入式系统设计

Cyclone II FPGA和Nios II嵌入式处理器的优势

Avalon设备怎么定制?

Nios II入门起步-创建一个嵌入式处理器系统

基于Chirp函数的Nios Ⅱ嵌入式实现

介绍如何用Nios II 软核处理器来开发FPGA嵌入式系统软件

基于Nios II实现AVALON总线与USB控制器的接口设计

NiOSⅡ处理器的Avalon总线架构资料下载

基于Avalon总线的PWM外设实现NiosⅡ嵌入式处理器的设计

基于Avalon总线的PWM外设实现NiosⅡ嵌入式处理器的设计

评论