针对双天线干涉SAR 基线测量系统数据量大、实时性要求高和体积小的特点,设计并实现了一种基于FPGA + PCI 的实时数据采集存储系统。 系统基于PCI 总线技术,采用FPGA 和大容量SDRAM 对采集数据进行控制和缓存,利用多个硬盘组成的磁盘阵列进行实时存储,实现了CCD 相机和激光测距仪与PCI 总线间的高速数据实时传输。 对系统进行了功能和性能测试,测试结果表明,系统数据吞吐量大,实时性强,性能稳定,能够有效地满足基线测量系统的需求。双天线干涉合成孔径雷达系统可以获取地面目标的高程信息,具有全天候、全天时工作、测绘范围广、分辨率高等优点。干涉测量一般采用单轨双天线或重复轨道单天线系统,对于单轨双天线系统,其交轨干涉基线越长、越精确,获取的高程精度越高。一般干涉基线长度大于4 m 时,基线呈柔性结构而不能保持稳定基线,由于柔性基线结构出现的变形和抖动,会造成2 个天线的相对位置和姿态动态变化,并最终严重影响高程精度。 采用CCD 相机和激光测距仪的组合基线测量系统能够实现对2 个天线的位置和姿态变化进行精密动态测量,CCD 相机对布设在天线上LED 标志点进行高速跟踪拍摄,激光测距仪同步测量平台与合作目标之间的距离。 这使得柔性基线测量系统具有输出数据量大、处理算法复杂、计算量大、处理实时性要求高等特点,本文针对柔性基线测量系统的需求,提出一种基于FPGA +PCI 的数据实时采集与高速存储的解决方案,进行了硬件关键功能设计与实现。 系统采用FPGA进行核心逻辑控制,对CCD 相机和激光测距仪的数据进行同步采集控制,整理、利用外部大容量的SDRAM 组进行缓存,采用专用的PCI 接口芯片PLX9656,实现了2 个传感器数据与PCI 总线数据的高速传输,利用多个SATA 硬盘构成的大容量的磁盘阵列进行实时存储。 并对该数据采集存储系统进行了功能和性能测试,实测数据表明本文设计的系统能够有效解决柔性基线测量系统数据高速采集,大容量数据传输的难题。

1、 系统组成及工作原理

1. 1 主要功能和技术指标

在柔性基线测量系统中,为了精确实时测量柔性基线的抖动和2 个天线相对姿态的变化,需要选择高帧频、大面阵的CCD 相机和高精度的激光测距仪进行组合测量,这样会产生大量高速的图像数据和激光测距仪输出的距离数据。 因此本文设计的高速采集存储系统主要功能是控制各测量传感器之间的时间同步,完成各传感器数据的实时采集,并对采集的数据进行分流。 一路数据进行高速存储; 另一路数据输出至另外的实时处理系统中。根据柔性基线测量系统的要求,本文系统应该能够实时采集和存储2 个传感器测量数据,需要达到的技术指标主要包括持续采集速度、持续存储速度和最小存储容量等。系统中CCD 相机采用SVS-VISTEK 公司生产的一款高分辨率、高帧频的面阵数字相机,图像的分辨率为1608 列× 1208 行,相机帧频最高为30 Hz. 该相机数据AD 采样为10 位,数据采集只取高8 位,则CCD 相机每秒产生的数据量约为55. 57 MB. 激光测距仪采用的是德国公司生产的LRFS-0040-2 激光测距仪,测量速率最高可达50Hz,数据接口采用的是RS 422 接口,产生的数据量为9. 6 KB / s.2 个传感器每秒的数据量约为56 MB / s,则采集系统的持续采集速度必须大于56 MB / s,才能对2 个传感器数据进行实时采集。只有当持续存储速率大于采集速度时,才能够把数据实时准确的存储数据。 所以持续存储速度要大于56 MB / s,SATA 硬盘理论读写速度最大可达150 MB / s,利用多个SATA 硬盘组成RAID阵列,可以提供比单个硬盘更高的存储性能。

根据柔性基线测量系统的需求,该采集存储系统的持续工作时间最长约为2 h,则需要的最小的存储容量约为390. 76 GB.根据上述数据采集系统的需求分析,并考虑到系统的可扩展性以及数据实际传输、终端处理的需要,要求数据采集记录速度要达到70 MB / s,持续写盘阵速度要达到120 MB / s,存储容量要求达到2 TB.对于32 bit /33 MHz 的PCI 总线,实际使用中一般能达到80 MB / s,数据进出系统内存都要经过PCI 总线,会导致总线的效率降低一半。 而系统的采集速度必须大于56 MB / s,所以选择64 bit /66 MHz的PCI 总线,数据传输的峰值速度可以达到528 MB / s,现有系统表明64 bit /66 MHz的PCI 总线实际传输的速度能达到200 MB / s 以上,所以该PCI 总线的传输速度完全能满足系统需求。

1. 2 系统组成和整体方案

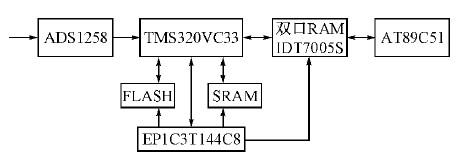

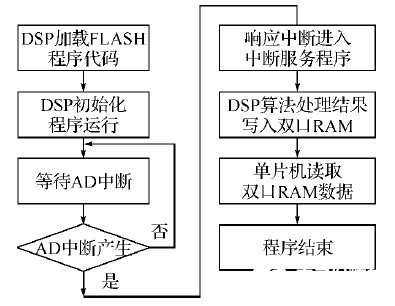

整个系统主要由CCD 相机、激光测距仪,PCI数据采集卡,SATA 磁盘阵列和计算机组成。 其中PCI 图像采集卡主要由传感器数据接口、FPGA 逻辑控制芯片、高速缓存、PCI 接口芯片组成。 本文提出一种基于FPGA + PCI 的数据采集存储系统的解决方案,该方案的原理如下: 首先由主机端发送命令对CCD 相机和激光测距仪进行配置,配置完成后启动采集,CCD 相机输出的高速图像数据、同步控制信号一起送到FPGA 中,在FPGA 中进行缓存,激光测距仪的数据通过串口也送入到FPGA 的双口RAM 中进行缓存,FIFO 半满后在FPGA 的控制下把CCD 相机和激光测距仪数据进行分流,其中一路送到外部的SDRAM 组中进行缓存,SDRAM 存储到设定图像帧数后给PCI 发送中断,主机响应中断,从SDRAM 中把数据读到内存中进行处理,并同时向硬盘中写数据完成实时存储; 另一路送到相关的实时处理系统中进行处理。整个设计方案的框图如图1 所示。

图1 数据实时采集与存储系统设计方案框图

应用于柔性基线测量系统的数据实时,采集存储系统的设计包括以下几个方面的关键技术:

Camera Link 接口技术、多传感器同步技术、多传感器数据的实时采集与高速缓存和多传感器数据的实时存储。

2、 数据实时采集存储系统关键设计与实现

下面对本系统中的几个关键技术具体实现的设计方案进行详细阐述。

2. 1 数据采集接口设计

实验相机采用Camera Link 标准接口,基本配置采用标准的MDR26 连接器输出。 本系统采用FPGA 作为采集卡的主控芯片,FPGA 支持的I /O 标准为LVCMOS /LVTTL 信号。 因此本系统对于Camera Link 接口的设计方案为: 通过DS90CR288A 接收器将4 路相机数据LVDS 信号和1 路相机时钟LVDS 信号转换成28 位TTL 数据,输出24 位图像信号、图像同步信号和像素时钟信号Strobe. DS90CR288A 的主要功能是完成LVDS 到TTL 电平信号的转换和串行信号转成并行信号。 为了对相机进行参数设置和触发控制,需要将FPGA 输出的相机控制信号( CC1-CC4 )和信号SerTC( serial-to-camera) 通过电平转换芯片DS90LV047 转换成LVDS 信号送入接收器中。为了接收相机向采集卡发送的应答信号SerTFG( serial-to-frame-grabber ) ,采用DS90LV048 把该LVDS 信号转换成TTL 信号后送入FPGA 中,并送入主机端进行显示。

2. 2 PCI 接口设计

由1. 1 节指标论证结果可知,本系统采用64bit /66 MHz 的PCI 总线来实现数据的高速传输。PCI 接口是PCI 总线与外部总线的通信接口,以实现二者的通信。 目前常用的PCI 接口的方案是采用专用的PCI 总线接口芯片,无需掌握复杂的PCI 总线协议,设计简单,能够减少开发周期和成本。 本系统中采用PLX9656 来进行高速PCI 卡的设计,以实现设置相机参数、设置激光测距参数、设置采样参数、读取图像数据等功能。 PLX9656是目前性能最高的PCI 接口控制器,具有PCI 端66 MHz、64 bits,LOCAL 端66 MHz、32 bits 的性能,符合PCI V2. 2 规范。 本系统中PCI 接口设计的重点是PLX9656 本地总线工作方式和数据传输模式的设置与实现。 PLX9656 的本地总线可以设置成3 种模式: M 模式、C 模式和J 模式。 根据本系统的特点,选择C 模式,可以通过把MODE1 和MODE0 引脚拉低来实现C 模式的工作方式。 在C 模式下,数据传输方式分为主模式操作、从模式操作和DMA 操作。 采用DMA 工作方式,能在不需要CPU 干预的条件下,实现高数外设和存储器间的快速传输,因此比较适合CCD相机数据和激光测距仪数据的传输,DMA 传输方式的实现可以通过对PLX9656 的内部寄存器的DMAMODE0 /1,PCICR置位来实现。

2. 3 FPGA 核心逻辑控制

基于FPGA 的时序逻辑控制模块是本系统的核心设计,能够实现对相机和激光测距仪的模式设置、相机和激光测距仪的数据同步控制、多个传感器数据的缓存与整理,对外部高速缓存的控制以及与PLX9656 的通信。 系统采用Altera 公司的Stratix Ⅱ系列EP2S60F1020 器件,配置芯片选用EPC16.

1) 传感器触发设置

本设计中,2个传感器的工作模式通过主机端进行设置,通过PCI 总线将模式设置字符串传到FPGA 中,通过串口控制器实现与相机和激光测距仪的通信,从而完成对相机和激光测距仪的配置。 且相机和激光测距仪收到配置命令后也通过串口控制器把应答信息传到FPGA 中,再通过PCI 总线传到主机上。为了实现与激光测距仪的同步控制,相机选择软件外触发模式,此模式下需要在FPGA 内产生一个频率为20 Hz 的EXSYNC 触发信号送给CCD 相机进行曝光读取数据,EXSYNC 的低电平宽度为10 μs,相机的曝光时间由主机端进行参数设置。

2) 数据同步控制

把EXSYNC 触发信号同时送给激光测距仪和相机,来实现2 个传感器的输出同步。 因为2个传感器的测量速度不同,相机的输出帧频为20 帧/ s,激光测距仪的输出频率为50 Hz,所以数据同步的设计关键在于如何记录同时刻的单帧图像数据和激光测距仪数据,2 个传感器同步采集的时序关系图如图2 ( a) 所示,CLK 100 Hz 是取2 个频率的最小公倍数,可以根据FPGA 的内部资源使用情况来设定,Data_lrf_sel 为选择的激光数据,其中I 表示该时刻的数据无效,V 表示该时刻的数据有效。数据同步方案为相机数据进入FPGA 后,在2 个双口RAM 中进行整理缓存,激光测距仪经过串口接收器把数据传入FPGA 内,本设计的串口接收器带有FIFO 缓存,数据经过缓存后接送入双口RAM 中进行进一步缓存; 按照图2 ( a) 所示的时序关系图生成双口RAM 的写使能WEN 信号,WEN 信号有效时把此时刻的激光数据写入双口RAM 中; 当读使能信号有效时,首先从双口RAM 中的激光测距仪数据到FIFO 中,接着读取相应帧的图像数据到FIFO 中; FIFO 半满后,激光测距仪数据和相机数据一起送到外部的SDRAM中进行进一步缓存,仿真时序图如图2 ( b) 所示。由图2 的仿真结果可知,本文同步设计方案能够有效地减少2 个传感器之间的延时,采集2 个传感器的相对同步数据。 虽然不是严格意义上的同步,但已能满足柔性基线测量系统的需求。

图2 CCD 相机和激光测距仪同步采集设计及仿真时序图

3) 数据缓存与整理

本系统中采用的缓存方案为首先把图像数据、控制信号进行3 级锁存,因为实验相机输出的图像数据为2 个TAP 的数据,分别把2 个TAP 的数据送入FPGA 内部的2 个双口RAM 中进行缓存,左边TAP 的数据按照顺序地址存储,右边TAP 的数据按照逆序地址存储,从而将2 个TAP的数据拼接成完整的图像。 当使能信号有效时,把2 个双口RAM 的数据送入到FIFO 中进一步缓存,当FIFO 数据半满后,把FIFO 的数据通过SDRAM 接口控制器送入到外部的SDRAM 存储器中去。

4) PCI 逻辑接口

本系统通过PCI 本地逻辑接口来完成FPGA与PLX9656 的通信。 系统加电启动后,PLX9656的内部寄存器由PCI 总线的RST#信号复位; 同时PLX9656 输出局部复位信号LRESET,并检查EEPROM 是否存在。 如果采用本地端DMA 方式控制,则整个握手过程如下: 首先当SDRAM 缓存中的数据达到设定值后,LINTI # 信号有效,PLX9656 向主机端发送中断请求信号; 若CPU 响应中断,则在中断相应程序内发出DMA 读命令、要读的字节数和地址信息等。 PLX9656 申请本地总线,使LHOLD 信号有效。 FPGA 驱动LHOLDA信号有效来响应PLX9656 的请求,PLX9656 将PCI 地址空间映射到本地地址空间。 接着通过设置寄存器来启动DMA 传输,PLX9656 有效ADS#( 地址选通信号) 、访问地址出现在LA 地址总线上。 再次FPGA 有效READY # 信号,同时使能SDRAM 控制接口的读使能有效信号,数据开始出现在LD 数据总线上。 当数据的最后一个字节开始传输时,PLX9656 驱动BLAST#信号有效,同时FPGA 无效READY #信号。 最后使SDRAM 的读使能是信号无效,PLX9656 驱动LHOLD 无效,释放本地总线,接着FPGA 也驱动LHOLDA 无效,结束一次数据的传输。 DMA 传输的时序仿真图如图3 所示。

图3 本地总线到PCI 总线的DMA 传输时序仿真图

2. 4 高速缓存设计

由于PCI 接口芯片内部缓存容量太小,所以在实时采集过程中必须采用高速缓存器将数据进行缓存,然后再通过PCI 总线送到主机,以提高系统的传输速度和性能。 大容量高速的SDRAM 容易买到且价格适中,本系统采用SDRAM 进行缓存。 Windows 是多线程、抢先任务的操作系统,为了减少线程由于CPU 占用时间结束而中断,中断间隔应大于线程的最大执行时间20 ms,所以缓存的容量至少应为: 20 ms × 70 MB / s × 2 = 2. 8MB. 本系统中采用Micron 的MT48LC32M16A2芯片,该芯片为512 MB 存储大小,16 bit 位宽,133 MHz 的读写速度,能够满足系统数据采集和存储带宽的要求。本系统采用缓存方案为在FPGA 外接2 组32M* 32 位的SDRAM,由4 片SDRAM 配置而成,用于相机到PCI 的数据缓冲。 且SDRAM 通过控制器的封装做成FIFO 的接口,相机的数据写入FIFO,按照设定的图像数量给PCI 发送中断,然后由PCI 读取相机数据,从而克服了SDRAM结构复杂,切换控制电路难操作的缺点。

2. 5 实时存储设计

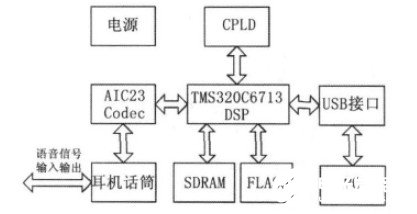

实时流盘一直是高速数据采集技术的最大瓶颈,直接制约了采集存储设备的实时存储能力。 本系统中采用支持66 MHz、100 MHz、133 MHz /64 bit的PCI-X 总线的主板,由8 块容量为1TB 的高速SATA 硬盘,通过3WARE 公司的RAID 卡配置成RAID0 方式,以获得最大化的磁盘访问速率,组成高速大容量的存储设备,整个数字相机数据采集存储设备的设计框图如图4 所示。

本系统把实时采集模块输出的数据,利用接口芯片PLX9656,通过PCI 总线把数据送进系统内存,然后在RAID 卡的控制下,将内存中的数据通过PCI 总线写入SATA 硬盘阵列中,理论持续写盘速度可达400 MB / s 以上。

图4 实时高速存储方案设计

3、 实验及系统测试结果

双天线干涉SAR 柔性基线测量系统的模拟实验平台由传感器测量平台、合作目标和运动平台组成,如图5( a) 和图5( b) 所示。 本文设计实现的数据采集存储系统实物如图5( c) 所示。

图5 柔性基线测量系统原理样机

实验中,对系统分别进行了功能测试和性能测试。 性能测试主要包括实时采集记录速度测试、持续写盘阵速度测试和稳定性测试。对于系统的功能测试,分别进行模拟图像和实际图像数据采集测试。 模拟图像为在FPGA 内产生循环有规律的数据,对应的图像为条纹图像,根据采集的数据是否正确来验证采集系统的功能; 然后切换到实际数据源,采集合作目标的运动图像。 模拟和实测的图像和数据文件分别如图6所示。

图6 数据采集系统采集的数据文件与图像

由图6( a) 和图6( b) 可知,对于模拟数据源,本文系统采集图像为黑白相间的条纹,且图像数据中像素的灰度值与设定值是一致的,不存在丢数问题。 由图6( c) 和图6( d) 可知,本文系统采集的合作目标的图像和实际物体是一致的。 模拟和实测图像数据的测试结果均表明,本文系统可以正确地进行数据采集和存储,没有图像错位现象,这验证了系统功能的正确性。系统实时采集记录速度的测试方法为: 由于本系统中传感器的输出频率有限,无法反映系统的最大采集记录速度。 采用在FPGA 内部生成不同频率的模拟图像,通过本系统进行实时采集和写盘,利用上位机软件对图像进行回放,查看有无丢帧和错位现象。 实测结果表明,当输出频率超过50 Hz 时,如果只采集不存盘,图像采集正确,但是选择同时存盘时,开始出现图像错位和丢帧现象。 原因主要有2 个: 一个是当频率大于50 Hz时,数据量大于100 MB / s,本系统外接的高速缓存,其读写速度理论值为133 MHz,因为做成FIFO 接口,是边写边读,造成传输速度减半,可能导致缓存数据没有及时读走,造成图像错位和丢失; 另一个是系统在主机内存中读和写是一个线程,边读边写数据导致速率跟不上。 综上所述,本系统的采集记录速度可以达到100 MB / s,满足系统70 MB / s 的指标要求。持续写盘阵速度测试方法为采用专用的硬盘读写速度测试软件,从主机内存往磁盘阵列写入不同容量数据,对软件统计的速度作平均。 实测结果表明,在不同的采集时间内,系统的实时存储速度都能达到240 MB / s 以上,满足系统指标120 MB / s的要求。 另外,系统采用8 块1TB 的SATA 硬盘,总的记录容量为8 TB,满足系统最小记录容量2 TB 的指标要求。对于系统的稳定性测试的方法为: 在不同工作模式下,多次采集2 个传感器数据,通过校验程序对数据包头计数器进行校验,统计数据的丢失帧数。 从而计算系统的丢帧率。 在系统要求的工作时间内,系统在不同模式下都没有出现丢帧情况,性能非常稳定,既使工作时间为要求的3 倍,本系统的丢帧率最高只有0. 03% ,能够满足基线测量系统的要求。

综上所述,本系统的实测性能指标均高于基线测量系统的指标要求,能够实时地对基线测量系统输出数据进行高速采集和实时存储。 为了进一步提高系统的性能,可以通过采用性能更高的磁盘阵列控制卡和高速磁盘阵列,如速率更高的SAS 接口硬盘,增大外部高速缓存容量,把SDRAM 做成乒乓模式提高传输速率,对主机端控制程序进行对线程优化等来实现提高采集记录速度。

4、 结论

基于FPGA + PCI 数据采集存储硬件设计,采用了高性能FPGA 逻辑器件与多个磁盘阵列构成的高速存储系统,实现了对柔性基线测量系统输出的高速采集与实时存储。 本文详细介绍了该设计的工作原理和关键模块设计,重点描述了利用FPGA 对CCD 相机和激光测距仪进行设置、同步采集与数据高速缓存,通过PCI 专门接口芯片,和PCI 总线进行高速实时传输的流程。 实际系统测试结果表明,该系统通过PCI 总线传输速度达200 MB / s以上,持续写盘阵速度达到240 MB / s,实时采集记录速度达100 MB / s. 该系统具有实时性强、性能稳定、设计灵活等特点。

责任编辑:gt

-

FPGA

+关注

关注

1626文章

21666浏览量

601830 -

芯片

+关注

关注

453文章

50397浏览量

421799 -

PCI

+关注

关注

4文章

662浏览量

130184

发布评论请先 登录

相关推荐

基于PLX965芯片和EP2S60F1020器件实现柔性基线测量系统的设计

基于PLX965芯片和EP2S60F1020器件实现柔性基线测量系统的设计

评论