引言

现代硬件程序设计规模越来越大,功能越来越复杂,当多个应用程序同时在一个硬件平台上实现时,各个程序的资源使用和数据通路可能会冲突,这增加了控制电路设计的复杂程度,给开发人员增加了工作量和开发难度。通过多重配置,可以将多个应用程序根据需要分时加载到FPGA 中,不仅精简了电路设计,而且使系统更加灵活。FPGA 多重配置的特点可以让特定条件下的用户选择片上资源不多的FPGA 去实现需要很多资源FPGA 才能实现的功能,这大大降低了开发费用,同时提高了FPGA的利用率。

Xilinx 公司Virtex5 系列的FPGA 具有多重配置的特性,允许用户在不掉电重启的情况下,根据不同时刻的需求,可以从FLASH 中贮存的多个比特文件选择加载其中的一个,实现系统功能的变换。

1 总体设计

当FPGA完成上电自动加载初始化的比特流后,可以通过触发FPGA内部的多重启动事件使得FPGA从外部配置存储器(SPI FLASH)指定的地址自动下载一个新的比特流来重新配置。FPGA 的多重配置可以通过多种方式来实现。本文采用的是基于ICAP核的状态机编码方式。通过调用Xilinx 自带的ICAP 核,编写状态机按照一定的指令流程对ICAP核进行不断的配置,可以控制FPGA 重新配置。这种方式可以在源代码中加很多注释,让后来的开发者很清楚地明白ICAP核指令流顺序,以及多重配置地址计算方法,是一种简单实用的实现方法。

1.1 硬件电路

多重配置的硬件主要包括FPGA 板卡和贮存配置文件的FLASH 芯片。FPGA 选用XILINX 公司Virtex-5系列中的ML507,该产品针对FPGA多重配置增加了专用的内部加载逻辑。FLASH 芯片选用XILINX 公司的SPI FLASH 芯片M25P32,该芯片存贮空间为32 Mb,存贮文件的数量与文件大小以及所使用的FPGA 芯片有关。实现多重配置首先要将FPGA 和外部配置存储器连接为从SPI FLASH 加载配置文件的模式。配置电路硬件连接框图如图1所示。

在FPGA配置模式中,M2,M1,M0为0,0,1,这种配置模式对应边界扫描加上拉,FPGA在这种模式下所有的I/O只在配置期间有效。在配置完成后,不用的I/O将被浮空[5].M2,M1,M0 三个选择开关对应于ML507 开发板上的SW3开关中的4,5,6位,在FPGA上电之前将上述开关拨为0,0,1状态。

1.2 软件设计

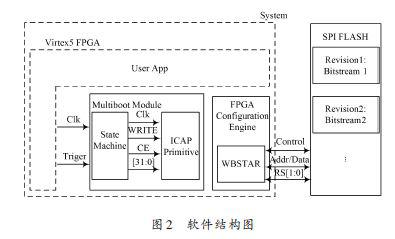

从软件设计的角度可以将FPGA 多重配置主要分为两个部分。第一部分是用户自己开发的程序,这一部分包括用户要在FPGA上边实现的功能,同时也包括为重载模块提供时钟信号,以及触发信号,本文触发信号是通过用户程序编写串口通信协议栈来接收PC端传输的数字作为触发信号。第二部分是FPGA 重载配置模块。FPGA多重配置首先要调用ICAP核,当满足触发条件后,采用状态机编码的方式对ICAP 核进行赋值配置。FPGA多重配置的软件结构图如图2所示。

FPGA多重配置的软件结构图如图2所示。

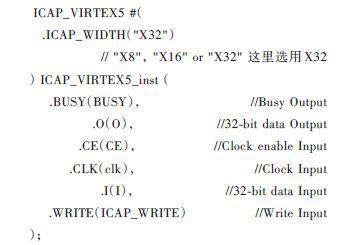

重载模块首先要调用ICAP核。ICAP原语在Xilinx的编译软件ISE 中调用,调用路径为Edit → LanguageTemplates,VHDL/Verilog → Device Primitive Instantia-tion→Virtex5FPGA → Config/BSCAN Components→ In-ternal Config Access Por(t ICAP_VIRTEX5)。

ICAP_VIRTEX5调用接口如下:

ICAP 核支持X8,X16,X32 三种数据带宽模式。在整个FPGA 重配置的过程中并没有用到ICAP核的输出,因此在重载模块的状态机控制程序中不关注BUSY,O 信号的值,可以不对它们赋值。用户程序在使用接口时只需对CE,CLK,I,WRITE4个信号不断赋值来发送命令。

在调用了ICAP核接口之后,通过Verilog编码的方式实现状态机。通过状态机发送IPROG指令给ICAP 核,ICAP 核在接收到这些指令后会根据指定的地址自动加载配置文件。

IPROG 指令的作用是对FPGA 芯片进行复位操作,该复位操作对FPGA 内部的应用程序进行复位,复位过程中除专用配置管脚和JTAG 管脚,其他输入/输出管脚均为高阻态。完成复位操作后,将默认的加载地址用热启动地址寄存器(Warm Boot Start Address,WB-STAR)中的新地址替换。

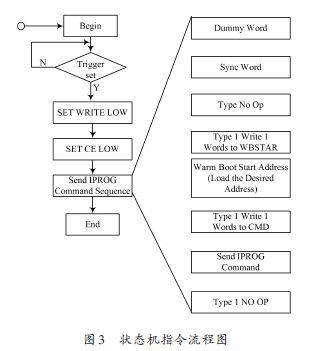

在发送IPROG 指令之前,需要对ICAP核进行预配置。重载控制模块在收到触发信号后,第一个时钟周期将ICAP 核的WRITE 信号和CE 信号置高,第二个周期将WRITE 信号置底,CE 信号置高,第三个周期将WRITE信号置底,CE信号也置底。接着在下面的8 个时钟周期里,将指令队列中的控制命令逐个发出。状态机指令流程如图3所示。

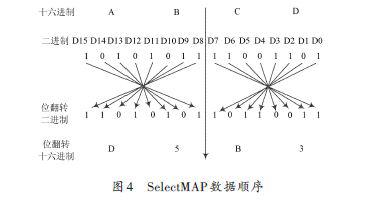

在状态机发送IPROG 指令的过程中,为了保证ICAP 核接收到正确的指令,每一个发送出去的命令和数据必须遵循SelectMAP数据顺序。SelectMAP数据顺序是将每个指令都按字节划分,划分后每个字节的数据都按比特位翻转。如果为“X32”模式,则划分为4个字节,每个字节进行位翻转。图4 以“X16”为例说明Se-lectMAP数据顺序。

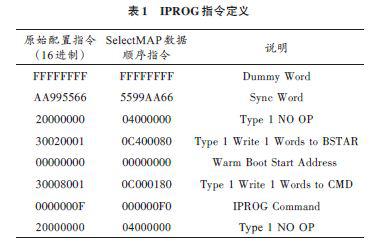

当状态机从用户程序接收到一个触发条件后,会发送一系列如图3所示的IPROG 命令。Verilog编码实现状态机的过程中,必须按照图3给出的指令顺序发送这些IPROG命令,否则无法正确的与ICAP核通信。同时这些指令都具有自己特殊的定义而且必须服从Select-MAP 数据顺序,否则无法通信。IPROG 指令的具体定义及说明如表1所示。

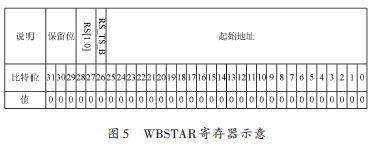

在上述配置指令过程中,第五步Warm Boot StartAddress Register(WBSTAR)指定了满足触发条件的比特流在SPI FLASH中的起始地址,WBSTAR被赋值的地址必须和即将配置的bit流在SPI FLASH中的物理位置相同,否则FPGA就无法从外部读取bit流。WBSTAR被赋值的数值都是提前根据程序的要求计算好的。计算WBSTAR值的时候需要了解WBSTAR寄存器每一位的具体含义,如图5所示。

WBSTAR寄存器共31位,高三位是保留位,RS[1:0]

两位指定了可以多重配置的bit流的个数。RS_TS_B是RS[1:0]的使能信号:0 表示Disabled,1 表示Enabled.

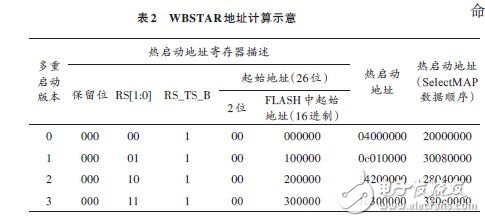

START_ADDR表示要回读的比特流在外部配置存储器的起始地址。状态机在对WBSTAR 进行赋值时,要根据自己选择的bit流个数以及对应各个bit流在外部配置存储器贮存的地址自行计算WBSTAR地址。这里以4个bit流为例说明WBSTAR地址的计算方法,如表2所示。状态机使用的地址是服从SelectMAP数据顺序的地址。FPGA 专用配置逻辑在收到IPROG 指令后,开始执行内部复位操作(JATG 管角和重载控制部分不进行复位操作),擦除板卡上原有的程序,从FLASH 芯片中WBSTAR 所指向的起始地址开始读取新配置文件完成FPGA的重配置。

2 多重配置的实现

Xilinx系列的FPGA 需要将后缀名为mcs的内存镜像文件固化到外部配置存储器中,FPGA上电后才能自动加载配置文件。一般的mcs文件只包含一个bit流文件,多重启动的固化文件(。mcs)包含多bit流文件。在将多个bit流整合到mcs 文件的过程中,需要指定每个bit流的起始地址,这样FPGA专用配置逻辑才能根据地址找到对应的bit流。首先将用户开发的应用程序和重载控制模块添加到一个工程当中,利用ISE编译软件生成位流文件(。bit)。由于Virtex5 系列器件本身的特性,一般情况下生产的bit 流文件大约为3 300 KB,而SPIFLASH 的容量为32 Mb 即4 MB,这个容量无法满足在一个SPI FLASH 上贮存多个bit流文件,需要对生成的bit流进行压缩。在用ISE 软件生成bit流文件时,当完成了Synthesize-XST以及Implement Design后,执行到最后一步Generate Programming File时,在Process Proper-ties 中General Options 选项中勾选Enable BitstreamCompression.通过这个压缩设置可以对bit 流进行压缩,压缩后的bit流大约在500~600 KB 之间,可以满足在一个容量为32 Mb的SPI FLASH上贮存多个bit流文件。其次将需要进行重配置的多个位流文件拷贝至一个工程目录下,有两种方法可以将多个bit流整合为一个mcs文件。第一种方法是通过ISE 编译软件的命令行窗口,使用命令行命令将多个位流文件合并为一个FLASH 存贮芯片M25P32 中烧写的内存镜像文件(。mcs)。第二种方法是用Impact 软件创建MultibootSPI FLASH,选择相应的FPGA 型号和FLASH 的容量以及要包含的bit 流的个数(版本的个数)。本文使用第一种方法来将多个bit 流文件形成一个内存镜像文件(。mcs)。使用promgen 命令的具体格式为:

promgen -spi -pmcs -oMulitBoot.mcs-s4096 -u0rev0.bit -u100000rev1.bit -u200000rev0.bit -u300000rev0.bit命令中各参数的说明如下所述。-spi:表示生成的mcs文件要固化到SPI FLASH中;-p mcs:生成文件的格式是mcs格式;-o ML507.mcs:要生成的文件名,可以根据需要修改;-s 4096:定义了外部存储器的容量,4096 表示32 Mb;- u 0rev0.bit:表示名字为rev0 的比特流文件在外部存储器的起始地址为0;-u 100000 rev1.bit:表示名字为rev1的比特流文件在外部贮存的起始地址为100000.在生成mcs 文件后,通过IM-PACT 软件将mcs 文件固化到SPI FLASH 中。

FPGA 上电自动从外部SPI FLASH 加载一个初始化的bit流,当需要执行新的程序时,会根据触发条件以及启动地址重新配置。在实验中,通过PC机串口终端发送指令当做触发条件实现多重配置。在实际应用中,还可以根据具体硬件实现,采用其他通信方式传送控制指令来进行触发。

3 结语

本文通过硬件电路和软件设计两个方面对FPGA的多重配置方法进行了详细介绍,本文所介绍的多重配置方法灵活方便、易于操作、电路简单,在工程中有很高的应用价值,同时关于bit流压缩的方法也值得参考。

-

FPGA

+关注

关注

1629文章

21729浏览量

603001 -

存储器

+关注

关注

38文章

7484浏览量

163763 -

Xilinx

+关注

关注

71文章

2167浏览量

121304

发布评论请先 登录

相关推荐

基于SPI FLASH的FPGA多重配置

揭秘FPGA多重配置硬件电路设计方案

中端FPGA开发板

谁有Virtex5 FPGA到TI公司64系列的EMIF设计文档??

IDDR最大速度为virtex5 sx95t

Virtex5无法正确读取XCF32P是为什么?

求virtex5与部分重新配置教程?

Virtex5 FPGA在ISE + Planahead上部分可重构功能的流程和技术要点

FPGA多重配置硬件电路的原理及其设计方案的介绍

FPGA开发板使用和配置方式

fpga开发板是什么?fpga开发板有哪些?

【GD32F303红枫派开发板使用手册】第二十讲 SPI-SPI NAND FLASH读写实验

以Virtex5开发板和SPI FLASH为基础的FPGA多重配置分析

以Virtex5开发板和SPI FLASH为基础的FPGA多重配置分析

评论