由于线路速率继续增长,DDR SDRAM在网络应用中正在被广泛地采用。不断增加的系统带宽要求正在推动存储器接口速度提高,而成本仍不断压低。LatticeEC FPGA系列的专门而灵活的DDR能力使设计者拥有满足下一代存储器控制器需求的低成本解决方案。

存储器已广泛地应用于当今的电子系统。由于系统带宽的不断增加,存储器技术针对更高的速度和性能进行了优化。结果,下一代存储器接口的设计变得越来越具有挑战性。在诸如FPGA的可编程器件中实现高速、高效的存储器接口对于设计者来说一直是一个主要的挑战。以往,只有少数FPGA持能可靠地与下一代高速器件接口的构建模块,这些FPGA通常是高端的昂贵器件。不过,现在LatticeEC FPGA系列也提供在低成本FPGA结构中实现下一代DDR2、QDR2以及RLDRAM控制器所需的构建模块、高速FPGA结构、时钟管理资源和I/O结构。

存储器应用

存储器是各种系统的组成部份之一,不同的应用有不同的存储器要求。对于网络基础设施应用,所需的存储器通常为高密度、高性能和高带宽,并具有高可靠性;在无线应用中,特别是手机和移动设备,低功率存储器是很重要的;而对于基站应用,高性能很关键。宽带应用要求存储器在成本和性能方面有很好的平衡;计算与消费类应用则需要诸如DRAM模块、闪存卡和其它对成本很敏感的存储器解决方案,同时要满足这些应用的性能目标。本文主要讨论在网络和通信中的存储器应用。

网络和通信应用需要大的、快速存储器,完成从小的地址查找到流量修整/监控再到缓冲器管理等各种任务。用于消费应用的价格便宜、成熟的FMP和EDO DRAM通常不适用,因为它采用了较慢的异步方式,且需要时序精确的命令信号来初始化数据转移。网络系统架构师一般转向采用静态RAM,解决时延问题,但这导致较高的成本。通过去除读和写周期间的等待状态和空闲周期,ZBT SRAM被广泛地用于改进存储器带宽。

最近,系统架构师在网络基础设施应用中转向使用SDRAM,以便减少时延、满足低成本要求。上述任务的每一个都伴随一组独特的需求。例如,低的和中等带宽的应用要求低时延的存储器,因此ZBT SRAM是理想的。

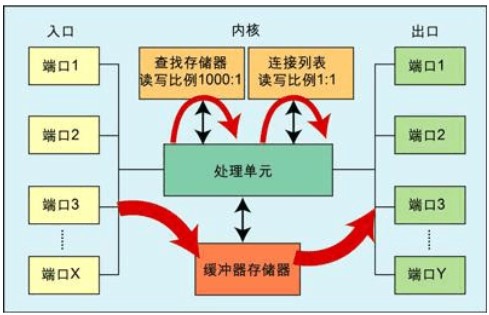

图1:网络中的存储器。不同的功能需要不同的方法。

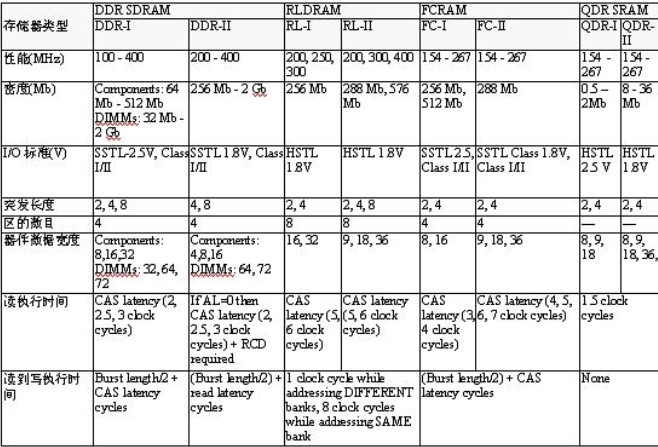

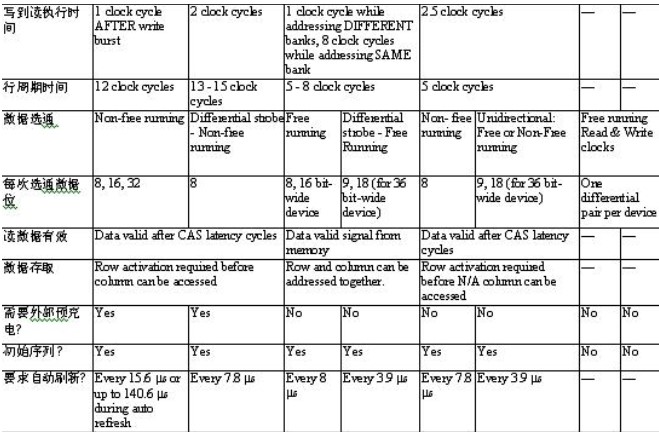

表1:为用于高速网络应用的存储器综合比较。

图1显示了典型的网络架构。在10Gbps,一个读写比为1000:1的地址查找可很容易地在DDR SRAM中得到处理。连接列表管理、流量修整、统计收集任务通常具有平衡的1:1读写比,需要较高性能的QDR SRAM。另一方面,较大的缓冲存储器一般在DDR SDRAM中实现。作为DRAM的替代,SDRAM同步存储器访问的处理器时钟用于快速数据传输。达到快速是因为SDRAM允许存储器的一个块被存取,而另一个块准备被存取。与DRAM不同,SDRAM采用流动电流而不是存储电荷,除去了连续刷新的需要。

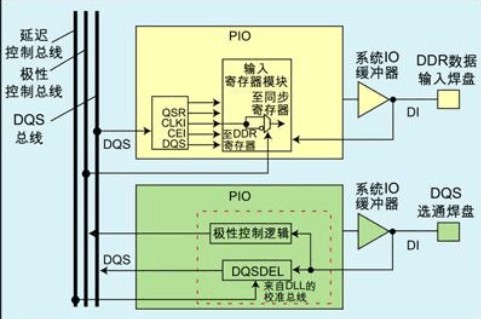

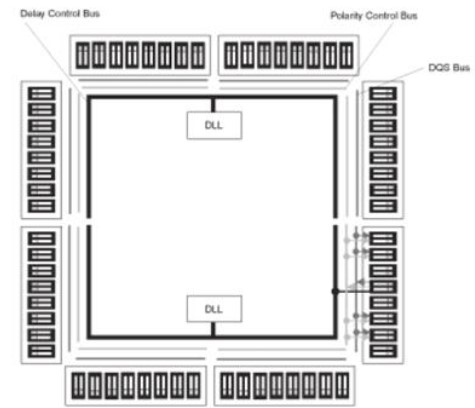

图2:LatticeEC FPGA中的专用DQS电路。

两个新的竞争者进入了高精度存储器舞台。快速周期随机存取存储器(FCRAM)改进了性能,它采用了流水线操作和隐蔽的预充电技术以减少随机存取周期时间,高度分段的存储器核减少了功耗。存储器核分段为较小的阵列,这样数据可以被很快地存取并改进执行时间。这些特征使得FCRAM被理想地用作缓冲存储器,用于诸如交换、路由和网络服务器等的高速网络应用中。时延减少的DRAM(RLDRAM)提供SRAM类型的接口以及非多路复用的寻址。RLDRAM II技术提供最小时延并可减少行周期时间,这些特征很适用于要求关键响应时间和快速随机存取的应用,例如下一代10Gbps以及更加高速的网络应用。

存储器控制器的挑战

目前存储器接口经常要求时钟速度超过200MHz以满足线卡和交换卡的吞吐量要求,这是FPGA架构的主要挑战。PLL是基本的允许控制时钟数据关系的部件。

下一代存储器控制器工作在HSTL或SSTL电压。低电压电平的摆动是需要的,以便??持存储器和存储器控制器的输入输出的高速数据操作。对于高速SRAM存储器来说,HSTL是实际的I/O标准,而对于高速DDR SRAM存储器,SSTL是实际的I/O标准。

高速差分I/O缓冲器和专用电路的组合能够在高带宽下进行无缝读写操作,传统上这属于高级FPGA的领域。LatticeEC FPGA改变了那个惯例,通过低成本FPGA架构实现了高带宽存储器控制器。

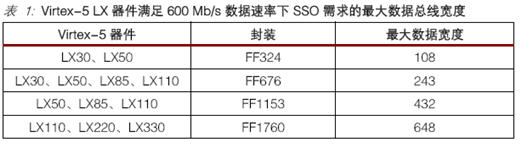

表2:为用于高速网络应用的存储器综合比较。

DDR存储器控制器的支持

实现高性能的DDR存储器需要在输入端的读操作和在输出端的写操作有专用的DDR寄存器结构,LatticeEC提供这个能力。除这些寄存器外,EC器件有两个单元简化用于读操作的输入结构设计,这两个单元是DQS延时块和极性控制逻辑。这两个块对于实现可靠的高速DDR SDRAM控制器十分关键。由于DQS逻辑的复杂性,用FPGA实现高速存储器控制器时,设计者会遇到问题。LatticeEC为设计者提供这些专用块,能够缓解这个问题。

DLL校准DQS延时块

源同步接口通常要求调整输入时钟,以便用输入寄存器正确捕获数据。对大多数接口而言,PLL被用于这种调整。然而对于DDR存储器,称为DQS的时钟是受约束的,因此这种方法不可行。在DDR存储器接口,DQS与主时钟的关系会有变化,这是由于PCB上走线的长度和使用的存储器所引起的。

图3:DLL校准总线和DQS/DQS转移分布。

如图2所示,Lattice DQS电路包括一个自动时钟转移电路,用以简化存储器接口设计和保证稳健的操作。此外,DQS延时块还提供用于DDR存储器接口所需的时钟对列。来自焊盘的DQS信号通过DQS延时单元送入专用的布线资源。DQS信号也送入极性控制逻辑,用于控制输入寄存器块中连至同步寄存器的时钟极性。

专用DQS延时块的温度、电压和工艺变化由一组校准信号(6位宽的总线)进行补偿,它们来自器件两侧的两个DLL。每个DLL补偿器件一半的DQS延时,如图3所示。DLL用系统时钟和专用反馈环来补偿。这是一个重要的结构特征,因为这个器件不会受到通常其它FPGA严格的I/O布局要求的牵制。

极性控制逻辑

对于典型的DDR存储器设计,延时DQS选通脉冲和内部系统时钟(在读周期)之间的相位关系是未知的。Lattice-EC器件含有专用电路在这些域间传递数据。为了防止建立和保持时间发生变化,即DQS延时和系统时钟间的域传递,它使用了一个时钟极性选择器,这改变了锁存在输入寄存器块中同步寄存器中的数据的边沿。这需要测定在每个读周期的起始时刻有正确的时钟极性。DDR存储器读操作前, DQS处于三态(由端接上拉)。起始时刻DDR存储器驱动DQS为低电平,一个专用电路用于检测这个传递,这个信号用来控制至同步寄存器的时钟极性。

-

FPGA

+关注

关注

1629文章

21746浏览量

603777 -

存储器

+关注

关注

38文章

7494浏览量

163899 -

服务器

+关注

关注

12文章

9191浏览量

85510

发布评论请先 登录

相关推荐

基于Xilinx 和FPGA的DDR2 SDRAM存储器接口

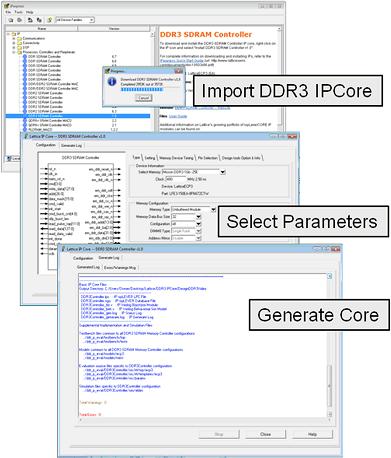

DDR3存储器接口控制器IP助力数据处理应用

如何用中档FPGA实现高速DDR3存储器控制器?

DDR3存储器接口控制器IP核在视频数据处理中的应用

基于FPGA的DDR2 SDRAM存储器用户接口设计

基于Spartan3_FPGA的DDR2_SDRAM存储器接口设计

基于FPGA的DDR3多端口读写存储管理的设计与实现

利用FPGA系列的DDR能力解决DDR存储器的接口设计

利用FPGA系列的DDR能力解决DDR存储器的接口设计

评论