一、 引言

我们独立自主开发了数据广播编码器和微型低功耗调频数据广播接收机,整套系统采用连续相位频移键控(CPFSK)调制方式,副载波频率为72KHz,占用带宽约16Khz,数据传输速率4.8KHZ。采用CPFSK调制方式使接收机易于实现,与QPSK的调制方式相比对相位稳定度要求不高,不易受外界温度噪声的影响,而且在信号解调处理时实现低功耗。

由于在发送端先后进行了数据编码、信道调制、线性调频,所以接收设备要完成信号逆处理。硬件结构框图:

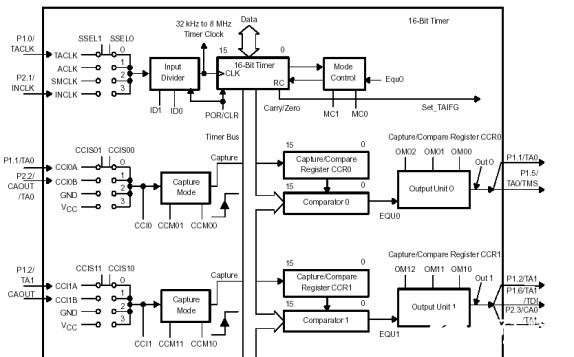

TI公司MSP430系列单片机的超低功耗特性(运行在1MHz时钟条件下工作电流视工作模式不同为0.1-400uA)、强大的外围模块功能、体积小等优点适合作为接收机的CPU。MSP430系列中的各成员集成了较多的片上外围资源,包含:12位A/D,精密模拟比较器,硬件乘法器,2组频率可达8MHZ的时钟模块,2个带有大量捕获/比较寄存器的16位定时器,看门狗,2个可实现异步、同步及多址访问的串行通信接口,数十个可实现方向设置及中断功能的并行输入、输出端口等。

MSP430F123单片机作为CPFSK数据广播接收机的CPU主要对基带数据进行处理,完成数据链路层的工作:

数据解码

位同步

帧同步

序列去扰

去交织

R-S纠错解码

CRC-16校验

三、数字通信中的同步问题

数据通信中,同步是非常重要的问题,通信系统是否可靠、接收灵敏度是否达到标准,很大程度上依赖于同步技术的优劣。

1、同步不确定性的来源

实际通信系统中,收发站之间会由于电波传播中的多径效应引起码相位、载波中心频率相位的延迟,而且在传输信道中随机噪声的叠加引起传输波形的失真,连接在接收滤波器之后的判决电路也很难保证“无差错”的恢复基带信号。这些都会导致同步的不稳定性。

2、实现同步的几种方法

按同步功用分类可分为载波同步、位同步、群同步和网同步。

按传输同步信息的方式可分为外同步法和自同步法。外同步法:是由发送端发送专门的同步信息,接收端把这个专门的同步信息检测出来作为同步信号。自同步法:发送端不发送专门的同步信息,而是由接收端设法从接收信号中提取同步信息。

本接收机的CPU要完成的功能中只涉及到位同步和帧(群)同步,由于不能从硬件解调FSK信号中恢复位同步时钟,所以采用自同步的方法来实现位同步,以下结合MSP430单片机的特点分析位同步和帧同步的实现方法。

四、位同步

由于本接收机接收的码元速率为4.8KHZ,用CPU捕捉位同步信息,然后进行采样,在配合RS纠错,即可达到数据准确传输的要求。

(一)、位同步的方法:

方法一、

〈图1〉

设置接收端恢复出的同步时钟的频率为5倍的码元频率,这样就在一个码元周期内,设置了5个采样点。位同步可以分为两个过程:捕获、同步跟踪。

1、 捕获,即找到正确的同步时钟起始点。在接收的数据中,只有0、1跳变沿才能为我们提供位同步信息,如果数据长时间为1或为0,这将给接收端恢复位定时信息造成一定困难。所以发送端对数字基带信号进行随机化处理,一方面起到能量扩散的作用,另一方面限制连0码和连1码的长度,易于位同步的捕获和同步时钟的恢复。

捕获过程是通过测量数据流中两个跳变沿中间的时间宽度(W),如果W等于码元周期,便以第二个跳变沿为起始时刻,设置同步时钟;如果W不等于码元周期,则需要重新捕获。

2、 同步跟踪,在接收数据的过程中,还要保证同步时钟的变化跟随码元相位或频率的偏移。同样,依据数据流中0、1跳变沿来实现同步时钟的跟踪。如图1:如果同步时钟与码元之间没有任何偏差时,数据的跳变沿每次都应出现在第5个计数时刻与下一个计数时刻之间,这时把第三个计数时刻作为数据采样时刻;当同步时钟与码元之间有偏差时,数据跳变沿不能准确的落在第5个与下一个计数时刻之间,如果数据跳变沿出现在第4 与第5个计数时刻之间,说明同步时钟相对于码元相位滞后,为保证每次采样时刻在码元的中心位置,就要把采样点提前至第2个计数时刻;相反,如果数据跳变沿出现在第1与第2个计数时刻之间,说明同步时钟相对于码元相位超前,就要把采样点错后至第4个计数时刻。这样不断调整采样点,使每次此采样时刻均位于码元中心位置,跟随其变化。

方法二、

根据MSP430单片机硬件特点,我们对上述同步方法进行了优化,并达到了良好的同步跟踪效果。

设置接收端恢复出的同步时钟的频率等于码元频率。每一个计数中点均为采样时刻。与5倍时钟法相同,它也需要捕获和同步跟踪两个步骤。捕获的过程与上述的方法相同。同步跟踪,可以使采样时刻基本稳定在码元中心位置。如果同步时钟不跟随码元相位的变化进行调整,则采样点必然相对于码元滑动,当向前或向后偏移半个码元周期时,采样值就出现错误。如图2,恢复出的同步时钟与码元同步时,数据跳变沿的发生时刻与前一采样时刻的距离(D)等于二分之一码元宽度(M)。在同步时钟与码元相对偏移时,则有D≠M,若D》M,同步时钟超前,就要将下一采样时刻滞后;若D《M,同步时钟超前,就要将下一采样时刻提前。在接收过程中,同步跟踪就是根据D与M的关系不断调整。

(二)、方法二的具体实现

MSP430单片机的Timer_A可支持同时进行的多种时序控制、多个捕获/比较功能、各模块独立编程,中断可以由计数器溢出引起,也可以来自捕获外部信号的跳变沿。

MC1和MC0选择计数器工作模式,MC1=0、MC0=1时定时器增计数至比较寄存器CCR0的值就会产生中断,用这种模式可以产生固定频率的中断信号作为同步时钟。当增大或减小寄存器CCR0的值时,即可改变定时的时间间隔,从而调整同步时钟的频率。由于定时计数器的调整精度为一个时钟周期1/4.3ms(外部时钟晶振4.3MHz),所以可以产生频率精确的同步时钟。

捕获模式用于确定事件发生的时刻,可用于速度计算或时间测量等场合。如果在选定的输入引脚(如图P1.2)上发生选定的脉冲触发沿(上升沿、下降沿、任意跳变),则定时器的计数值被复制到捕获寄存器CCR1中,并产生中断。因此,读出CCR1中的值就可以记录跳变沿发生的时刻,根据跳变沿发生时刻与前一采样点比较的结果,调整同步时钟,超前或滞后,重新预置CCR0。

《图2》

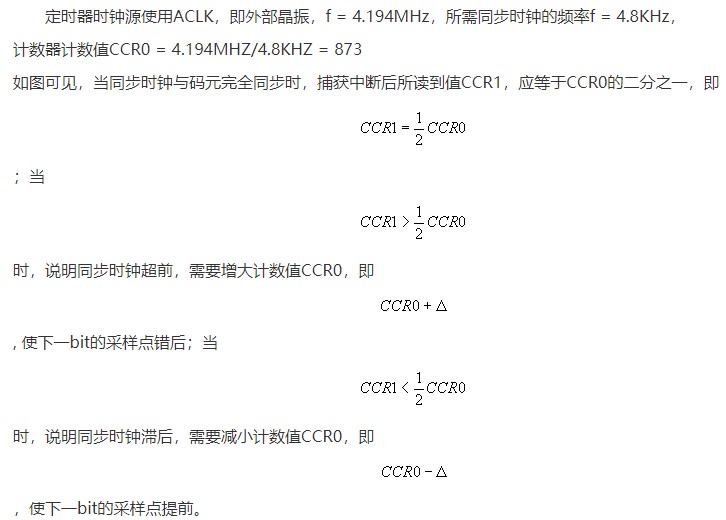

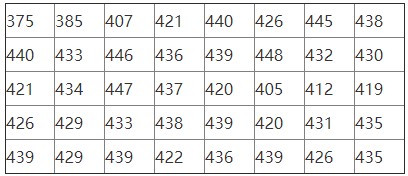

定时器时钟源使用ACLK,即外部晶振,f = 4.194MHz,所需同步时钟的频率f = 4.8KHz,

计数器计数值CCR0 = 4.194MHZ/4.8KHZ = 873

在上式中的 △ 称为数据速率的误差容限值(datarate tolerance),如果设置的这个容限值太高(即:时钟调整的步进值过大),就会导致同步时钟的频率不能稳定;反之这个容限值太小(即:时钟调整的步进值过小),同步时钟就不能跟踪上码元的变化;只有这个容限值合适,同步时钟产生的采样点就会逐渐收敛到接收码元的中心位置

时采样点基本位于码元中心

从表中看出同步时钟的采样点逐渐收敛在码元中心位置,并且-在以后的接收过程中,实现跟踪。

(三)、小结

由于采样时钟恢复和同步捕捉跟踪都需要响应中断服务程序,占用CPU开销。而CPU 的主要工作是进行每帧数据的解码和发送。如果使用第一种同步方法,时钟频率4.8K*5,CPU时钟为4.3MHz,即程序每运行41.6us、约20条程序语句就要响应一次定时器中断服务程序,增大了运算量。如果提高CPU的工作频率,会增大电流的消耗。所以在达到相同的采样效果时,使用第二种同步方法。同理,为节约CPU开销,并不需要捕捉每个数据跳变沿进行同步跟踪,实验证明每8比特数据捕捉一次跳变沿调整采样时钟,即可实现良好的同步跟踪。

五、帧同步

在数字信息传输中,帧同步信号是一些特定的码组,这种帧同步码组通常是在某段时间集中插入信息码流。考虑到时间位置的确定,要在建立了各码元的正确时间关系后才有能实现,所以帧同步一般是在位同步的基础上实现。

(一)、对帧同步系统的要求

1、 帧同步的捕捉(同步建立)时间要短,

2、 在一定的同步引入时间要求下,帧同步信号占用的码组长度应越短越好。

3、 同步系统的工作要稳定可靠,一旦建立同步状态后,系统不应因信道的正常误码而失步,即帧同步系统应具有一定的抗干扰能力,能识别假失步和避免伪同步。

数字信号在传输过程中总会出现误码而影响同步。一种是由信道噪声等原因引起的随机误码。此类误码造成帧同步码的丢失往往是一种假失步现象。因此,一般规定帧同步信号丢失的时间超过一定限度时,才宣布帧同步态丢失,然后开始新的同步搜索(捕捉态)。这段时间称作前方保护时间。然而,无论选用何种帧同步码型,信息码流中都有可能出现与帧同步码图案相同的码组,即伪同步码。所以也不能一经发现符合帧同步码组的信号就进入同步态。只有当帧同步信号连续来了几帧或一段时间后,同步系统才可发出指令进入同步态,这段时间成为后方保护时间。 (二)、帧同步的实现

本接收机使用集中插入特殊码元的帧同步方法,集中插入就是把特殊的帧同步码组集中插在一帧的特定位置(一般是一帧的开始)。接收机一旦检测到这个特定码组就确定了帧的起始位置,从而获得帧同步。此种方法可以迅速纠正帧失步,即一旦帧失步,只要在下一帧同步码就能恢复帧同步。

本接收机收到的数据帧格式为:

每192个信息字节加上2字节的帧同步码组成一帧数据(如图)。选用的帧同步码为0x19D7。

接收端采用帧同步码的滑动法来恢复帧同步信号。其实现方法为:在单片机里设置16bit移位寄存器、前后方保护计数器来完成前方保护时间和后方保护时间的计数,和帧同步状态位SFLAG,标志系统的同步状态。

当数据流进入移位寄存器,与帧同步码(0x19d7)相比较,如果不同则移位寄存器高位移出低位移入下一比特再进行比较,同步系统从不断接收输入的数据流中捕获到0x19d7码组,相当于第N帧有同步码,置SFLAG=1,后方保护时间计数器开始,如果经过192byte信息码在第N+1帧处检出同步码,后方保护时间计数器加1,应在第N+2帧再一次检出同步码,后方保护时间计数器加1,系统进入帧同步状态,进行数据定时接收。如果在第N+1帧处不能检出同步码或在第N+1帧处检出同步码而在第N+2帧处不能检出同步码,同步系统都要重新进入捕获状态。当系统处于同步状态即SFLAG=1时,检测出错误的帧同步码,则打开前方保护时间计数器,如果连续丢失4(或5)个帧同步码,计数器计满,清SFLAG=0,标志系统进入捕捉状态并停止数据定时接收。

在本接收机MSP430的程序中将前方保护时间计数器和后方保护时间计数器简化为一个时间计数器,即SCOUNT。SCOUNT的初始值为0,每接收到一个正确的帧同步码,SCOUNT加1,当连续接收到三个正确的帧同步码时(SCOUNT=3)进入同步状态SFLAG=1,如果在同步状态中SCOUNT=4时,再检测到正确的帧同步码SCOUNT不再加1,也就是说SCOUNT的最大值为4;当检测到一个错误的帧同步码,SCOUNT减1,如果出现连续4个错误的帧同步码,SCOUNT减为0,则从同步状态进入捕获状态。

六、数据链路层

MSP430单片机进行位同步、帧同步后,将定时接收的数据经过以下处理经串口输出。

1、去扰

伪随机序列发生器的生成多项式为

每帧同步字后进行一次初始化, 加扰不包括帧同步字,数据由伪随机序列加扰,可破坏数据中的连零,有利于解码器位同步的锁定,并分散数据信号的能量分布,使对主信号的干扰呈类似白噪音的背景噪音,提高多工数据对主信道干扰的主观评价得分。

2、去交织和纠错码

每一子帧用缩短R-S(48,32)编码,可纠8个符号(64Bit)的随机错误。再进行卷积交织,这样数据系统能纠正长达384Bit突发性误码。这样对4.8Kbps 的抗突发性干扰时间分别为80ms 。

3、校验

采用CCITT-16校验码,可检出超出纠错范围而造成的误码,在每一子帧内验出所有≦16位的错误,可检出99.998%的17位突发性错误,99.997%的18位和大于18位的突发性错误,可以满足大多数信息及计算机通信的要求。涉及金融数据及对数据有严格要求的信息,用户可另加其它校验。

4、 输出数据帧形成

接收机根据自身的权限对于不同的业务数据,形成不同的输出帧格式进行数据输出。

七、测试结果

通过实际播出测试验证,微型低功耗CPFSK数据广播接收机的总体设计是成功的,实现了预期的设计目标,特别是较强的信道纠错编码极大地改善了接收能力。

2002年8月在北京月坛发射塔,发射频率为91.5MHz调频发射机上进行播出测试,分别使用信息0-信息7传输电子文本数据,实现用户的有条件接收;2002年9月使用透明页格式来传输差分GPS的改正数据,链路测试成功;该系统即将用在电子车站牌、路灯控制系统中。

责任编辑:gt

-

单片机

+关注

关注

6037文章

44561浏览量

635567 -

cpu

+关注

关注

68文章

10870浏览量

211874 -

接收机

+关注

关注

8文章

1182浏览量

53491

发布评论请先 登录

相关推荐

基于MSP430单片机实现CPFSK调频数据广播接收机的设计

基于MSP430单片机实现CPFSK调频数据广播接收机的设计

评论