商业卫星通信系统工作在恶劣环境和极端温度中,符合高可靠应用的所有要求。即便它们对于公司使命并不关键,但电信服务商和广播公司仍依赖它们来交付创收服务。直到最近,自适应天线的运用还不算是一个成熟技术,而现在已有可能把它们用在这些通信系统中,前提是多个信道同步这一难题得到解决。

自适应天线系统使网络运营商能增加无线网络容量。自适应天线能有效定位和跟踪多个信号,来动态地使干扰最小化,预期的信号接收最大化,因此有望提供更高的频谱效率,更大的覆盖范围,更高的频率复用率。但是,这些性能优势会导致更高的复杂性,结果,自适应天线收发器被常规体系结构更复杂。需要为每个天线阵列元件准备单独的收发器信道,并且信道之间需要准确的实时同步。

天线类型

可按物理结构、辐射模式或工作频率来对天线分类,但它们的设计目的均为辐射和接收电磁波。天线的目的是尽可能把电磁能转换为电流,反之亦然。在这方面,天线是收发系统的自由空间和传输线之间的过渡结构。

自从机电技术在19世纪末期开始得到利用以来,这两大设计领域已经实现了许多改进,科学家和工程师们努力提高效率、动态范围和容量。能量分配到周围空间以及从周围空间收集能量的效率,对频谱的运用、新网络建设成本以及这些网络提供的服务质量有深刻影响。

通过利用多根一起工作的天线来提高特定网络的覆盖范围和容量,许多种技术得到部署应用。分集方法(Diversity)利用随时间变化(例如衰减)的信号在各个位置不相同这一事实,来改善无线电波的接收。换言之,即便对于两个相隔仅一个波长的位置,信号的衰减也很可能不相同。为利用这一事实,使用两根相隔一定距离的天线来接收相同信号。在任何特定时间,在两个信号当中,信号电平最高的那个被自动发送到接收器。分集常用于信号接收。

天线还经常被排列成多元阵列。阵列是几个互连的元件被排列成匀称的结构,来形成单个天线。阵列的用途是产生某些辐射模式,它们具有单个元件无法实现的某些合乎需要的特征。当几个天线元件被组合在阵列中(称作阵列因子)时,总体辐射模式会改变。

还可连贯地组合多个孔径的输出,来产生将在接收子系统中被解调的信号。更先进的天线技术已经开发成功,使一根天线能迅速改变其辐射模式,来响应接收信号到达方向的变化。这些天线以及配套技术被称作自适应天线或智能天线。

智能天线体系结构

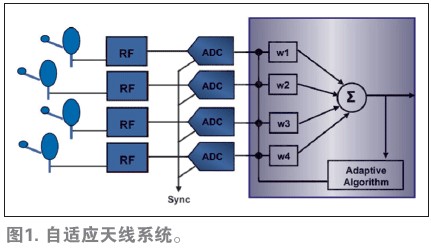

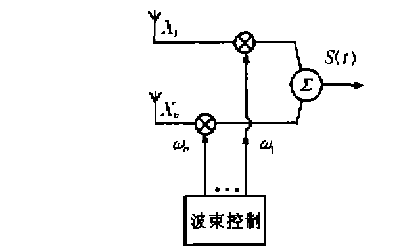

自适应或智能天线进一步拓展了分集概念。典型的自适应天线系统如图1所示。此类系统把天线阵列与数字信号处理能力结合起来,以便用一种自适应的空间敏感方式来完成收发。自适应天线能实时修改其辐射模式,来确保主瓣指向最大信号电平的方向。该方法还可被用于指向某个不需要的干扰信号方向中的无信号状态。

本质上,可在相同方向采用几个元件来放大较弱的预期信号,并消除不需要的干扰。同样,系统可以把信号组合起来,并把它们朝相同方向发射。这类方法还被称作波束成形。结果就是各个元件的动态范围可被集中起来,并能区分预期信号和非预期信号。此类好处使得自适应天线系统与常规系统相比很有吸引力。事实上,自适应天线方法的采用有望对频谱的高效使用、新无线网络建设成本的最小化、服务质量的优化产生重要影响。

但是,实现更高性能的代价是使收发器更加复杂,这是因为自适应系统需要为每个阵列元件准备单独的收发链。各个收发链必须精确同步,以便保持发射信号和接收信号之间的相位关系。本节仅重点介绍接收子系统。现代接收系统采用很快的ADC,采样率至少为1Gsps。人们需要高采样频率,这是因为奈奎斯特带宽(Nyquist bandwidth)与ADC采样频率有很简单的直接关系,NyquistBW=FS/2,其中FS即为ADC采样速率。

增加信息量

有效增加奈奎斯特带宽,就能增加收发器中的每条ADC信道的信息载波,由此提高系统吞吐率。与多信道接收器中的同步有关的一个挑战是,采样率很高的ADC会产生很高的数据速率。正常情况下,ADC有一个输出时钟来把输出数据锁到FPGA或ASIC中。但是,多信道收发器中的ADC输出时钟之间的相位关系是未知的。

系统设计者面临的挑战是要使来自多个运行于每秒数百兆或数千兆的ADC的数据同步。在系统级,一般不会试图使ADC自身同步,而是实施额外数字电路来使ADC之后的FPGA或ASIC里的数字数据重新同步。这条额外的复杂数字电路处理ADC的高速数据输出,此外还需要额外的电路开销(overhead circuitry)来确定ADC之间的实际相位关系。因此,系统级同步的缺点是需要额外高速数字电路来处理ADC输出,并且多个转换器之间实际相位关系的确定所需的开销电路很复杂。

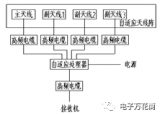

ADC10D1000等等配备创新技术的新型转换器能克服这个技术难题——在自适应天线系统中使多条信道同步。该器件是National Semiconductor公司的超高速空间适用ADC家族的新成员。它采用0.18μm纯CMOS工艺制造,满足100krad总辐射剂量(TID),并且对于超过120MeV/mg/cm2的密度具备单事件闭锁抗扰度。该设计产生的有效位数(ENOB)高达9.0,具有248MHz输入信号和1GHz 采样率,同时提供10-18误码率。该产品采用376引脚密封CCGA封装。

同步多个接收器信道

该型号有两个特性来同步系统中的多个ADC:AutoSync和DCLK Reset(图2)。DCLK Reset特性工作方式与AutoSync特性不同,但本质上执行的是相同功能。但是,当人们试图同步三个或更多ADC时,板级实施会更具挑战性。

AutoSync 是一种拥有专利的技术,不断地使系统中的多个此类转换器同步。它的工作方式无需特殊的同步脉冲,并且同步期间可能引起的任何扰动都会在一个DCLK时钟周期内得到恢复。主/从ADC可被排列成一棵二元树结构(binary tree),这样任何扰动将很快从系统去除掉。

该技术指定一个ADC为主ADC,系统中其它的为从ADC。一个带有一个主ADC和两个从ADC的系统实例如图3所示。主ADC提供两个基准时钟——RCLK1、 RCLK2,它们被一号和二号从ADC使用。为简单起见,只显示一个DCLK。但在现实中,有DCLKI和DCLKQ时钟,但根据内部芯片设计,它们生来就同相。对于数据转换器数量更多的更先进系统,链中的每个ADC被轮流用于产生两个基准时钟,这样基准时钟就以二元树形式传播(图3)。

复杂的同步

对于系统中有多个主ADC和从ADC的应用,AutoSync可被用于使各个从器件与各自的主器件同步,而DCLK Reset可被用于使主ADC彼此同步。为使多个ADC的DCLK以及数据输出同步,各个DCLK必须同时过渡,并且彼此同相。每个ADC的DCLK是在一段等待时间后从CLK生成的,加tOD(输出数据延时)减tAD(孔径延时)。因此,要想使DCLK同时过渡,CLK信号必须同时到达每个ADC。

为了消除通往每个ADC的CLK路径中的任何差异,可使用tAD调节特性。但是,使用该特性,还会影响DCLK在输出端产生的时间。如果器件处于解复用器方式,那么就有四个可能的相位,每个DCLK可能会在其中某个相位上被生成,这是因为对于本案例,典型的CLK是1GHz,而DCLK是250MHz。 RCLK信号控制着DCLK的相位,使得每个从DCLK与主DCLK同相。

有四个步骤来实现这个目标。首先,通过SPI把一号 ADC配置成主器件,并把其它所有ADC配置成从器件。然后,对于其基准时钟给其它ADC馈电的那些ADC,给它们的基准时钟通电。它们的默认方式是断电,以便省电。在下一步,对于每个从ADC,调整RCLK_IN时序来实现清洁记录。

最后,对于每个从ADC,选择四个DCLK相位中的某个,使得DCLK相位与主器件的相位匹配。用户可以选择那个通过SPI来对齐两个DCLK的相位。

责任编辑:gt

-

接收器

+关注

关注

14文章

2488浏览量

72534 -

天线

+关注

关注

68文章

3235浏览量

141436 -

卫星通信

+关注

关注

12文章

731浏览量

38921

发布评论请先 登录

相关推荐

基于AccelDSP的自适应滤波器设计

在WCDMA中LMS自适应天线阵的硬件实现

基于WCDMA技术规范的LMS自适应天线阵的硬件实现

CDMA系统中的几种智能天线自适应算法

PSAM自适应调制OFDM系统模型

基于LS-LMS的智能天线自适应干扰抑制方法

WCDMA中LMS自适应天线阵的硬件实现

如何才可以不使用自适应算法实现智能天线系统

自适应天线系统的原理及应用优势分析

自适应天线系统的原理及应用优势分析

评论