1、引言

三坐标测量机做为一种高精度测量仪器,在机械工业、汽车工业、航空航天等领域具有广泛的应用。本套通讯系统采用FPGA为主要通讯芯片,使用FPGA实现各通讯模块对数据的收发,配合单片机对数据进行编码、解码、重封装,实现了计算机和控制系统的通讯;由于FPGA程序的并行执行结构和高的执行速度,因此大大保证了数据传输的准确性和快速性。

2、通讯模块的实现

2.1 计算机与桥接卡的通讯

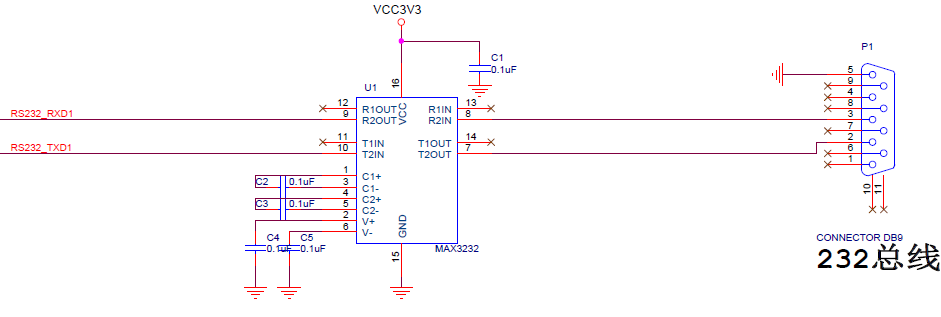

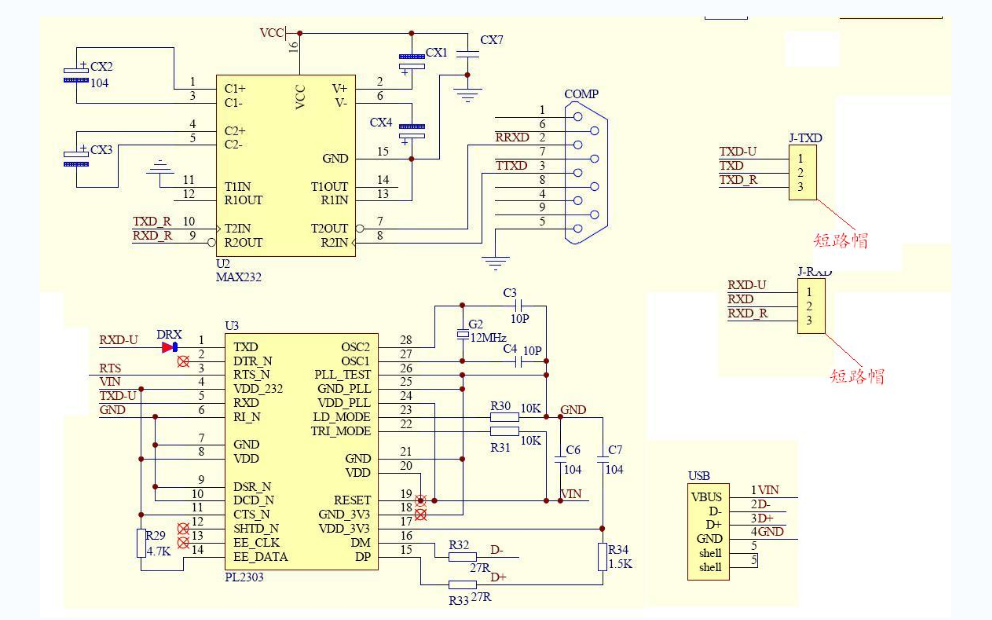

本系统采用RS232总线实现计算机和桥接卡之间的通讯。计算机发送的数据,经过RS232总线传输到桥接卡,通过MAX3232芯片实现电平转换。FPGA检测到起始位后接收数据,接收完数据后,将其存于UART接收FIFO[2]中;待接收到结束位时,FPGA产生中断信号,触发单片机读取接收FIFO中的数据并对其解码,判断数据中的目的地址,根据目的地址决定是否处理或发送到控制板;桥接卡与计算机通讯时,首先将数据进行编码,然后将数据置于发送FIFO中,启动发送模块,发送模块自动将数据发出,数据经MAX3232发送到总线上等待计算机的接收。

(1)串口发送模块的FPGA实现

串口发送模块从发送FIFO读出数据后,根据串口通信协议,数据在向外发送时,低位在前,高位在后,所以将八位的数据重新进行编辑:前加停止位‘1’,后加起始位‘0’,变为十位数据包,将十位数据按照设置波特率逐位发送即可,使用Modelsim进行仿真,仿真图见图1(data位要发送的数据,tx为发送线)

(2)串口接收模块的FPGA实现

总线空闲时当检测到由高到低变化时,表明数据开始传输,接收模块准备接收数据,接收数据时低位在前,高位在后,当接收到起始位后,每隔一个数据传输周期接收一次数据,待接收到八位数据后将数据置于接收FIFO中,使用Modelsim进行对发送模块仿真见图2(rxBuf为接收到的数据,低位在前,高位在后):

2.2 桥接卡与控制卡及控制卡之间的通讯

由于桥接卡需要和多个控制卡进行信息的交换,且不同的控制卡之间也需要数据传输,因此在进行总线选择时,必须保证各个器件都具有主控的权利,可以占用总线,本系统中桥接卡和控制卡及控制卡之间采用I2C[3][4]总线进行通讯。

I2C总线是一种两线式串行双向总线,是多主控的总线,由时钟线和数据线构成,数据传输时,时钟信号由主控器件产生。当SCL为高电平时,SDA出现由高电平到低电平变化,表明开始传送数据;当SCL为高电平时,SDA出现低电平到高电平变化,表示数据传送结束;接收方收到数据后,需向发送方发出应答信号;为了防止总线上数据冲突,总线有仲裁机制,当总线同时被多个发送方占用时,首先出现高电平的发送方被仲裁掉,因此,最长低电平周期的器件占用总线,成为主控器件;被仲裁掉的器件,放弃总线,改为接收。

使用FPGA实现I2C总线时,需要建立三个模块:总线监视模块,总线发送模块,总线接收模块。

①总线监视模块[5]的实现

总线监视模块用来为发送和接收模块提供总线状态,总线分为空闲、忙、等待三种状态。当总线上没有数据传输时,保持高电平,称为空闲态;数据传输期间,总线为忙的状态,如果主控方占用总线后没有数据发送,则为等待状态,如果总线等待时间超过设定时间,总线由等待转为空闲态。发送、接收模块需要得到的信号为起始信号、结束信号和状态信号,由总线监视模块实现这些信号。使用Modelsim进行仿真,得到波形如图3:

②I2C发送模块[6]的FPGA实现

发送模块主要实现对数据的发送;首先发送地址,发送完地址后,等待应答信号,如果没有响应,则放弃总线;如果出现响应,I2C发送模块输出RAM地址,读取RAM的数据,依次发送数据,每发送完一个字节,等待响应信号,发送模块根据RAM中的数据长度,将RAM数据读完。为了防止多个主机同时占用总线,应根据仲裁机制将总线上的非主控方仲裁掉,禁止其继续占用总线。为了防止总线传输中信号延迟,当向总线上发送下一数据时对总线上的状态进行判断,如果正确,再发送下一位数据。否则,放弃总线。使用Modelsim对I2C发送模块进行仿真如图4。

I2C_outScl:发送时钟;I2C_inScl:检测时钟

I2C_outSda:发送数据;I2C_inSda:检测数据

desAddr:目的地址;msgData:发送数据

RAM_Addr:RAM的地址信号。

③I2C接收模块[7]的FPGA实现

接收模块接收到总线监视模块发送来的起始位信号后,准备接收总线上的数据,接收到的地址后,判断接收到的地址和电路板地址是否一致;当两者一致时,向总线置应答信号ACK,继续接收下面的数据,收到的数据置于接收FIFO中;如果地址不一致,则放弃总线。使用Modelsim对I2C接收模块进行仿真如图4。

I2CbusIsBusy:总线状态;I2C_start:起始信号

myAddr:电路板的地址; rxBuf:接收寄存器

rxFIFO_wr:接收FIFO的写信号

3、通讯协议

上位机和桥接板之间采用RS232总线进行数据传输,桥接卡和控制卡以及各个控制卡之间采用I2C总线进行数据的传输,通讯采用主叫和应答方式,数据传输中使用单片机进行解码[8]。

主叫方发出指令后,等待对方响应,如果主叫方写指令到被叫方,则被叫方收到指令执行操作后返回确认信号;如果从主叫方读指令,则被叫方在下一时刻占用总线后发送数据到主叫方,主叫方在0.5s内没有收到响应包,表明传输失败。若连续3次没有响应,则与对方通信连接失败。

为了实现数据的一致性,RS-232和I2C总线采用相同的通信协议。

数据传输时以“包”进行封装,中间加入长度位和奇偶校验位。封装格式:起始字符+长度字符 +序列号+源地址+目的地址包类型+传输数据+包校验+结束字符;数据传输均采用ASCII码。

包的定义:起始位定义为‘#’,占用一个字节,接收方接收到‘#’时,表明数据开始传输;长度字符定义为除起始字符、结束字符和校验字符的所有原始字符的长度,占用一个字节;源地址:发送方地址,占用一个字节;目的地址:接收方地址,占用一个字节,当为‘00’时,定义为广播地址;包类型:占用一个字节,表明数据的类型,接收方根据包类型执行对应操作;传输数据:控制量的大小;包校验:定义为长度字符,源地址,目的地址,包类型和数据之和,占用两个字节;结束位:定义为‘~’,当接收方接收到结束字符时,表明本包传输结束,对数据包进行处理,长度位和校验位正确时执行指令,否则,放弃改数据包。

4、实验结果

使用该通讯系统实现和四控制卡之间的通讯控制,使用串口助手进行数据收发,在发送数据间隔为5us的情况下对该通讯系统进行测试,在进行8小时的测试中,系统没有出现数据丢失、错误、死机现象;使用广播地址进行数据发送,返回信号正确,没出现死机现象。

使用该通讯系统对四个电机进行控制,电机实际输出情况如表1:

本实验数据证明了该通讯系统的可用性及数据传输的准确性。

使用该系统采用广播地址实现四个电机同步联动,各个轴的运动情况如表2:

本实验数据证明了各个电机实现了指定的转动角度;各个轴运动期间,电机的状态经过I2C总线[9]及RS-232总线通讯系统成功的发送到了上位机,通讯系统没有出现死机和数据丢失,经过该实验,证明了数据传输的正确性。

4、结论

本系统采用FPGA进行通讯系统的设计,提高了数据的传输率和准确性,实现了对控制机构及时、快速的控制,有效防止突发事件的处理,经实验证明,本系统快速、准确的实现了数据的传输,可以有效快速的实现对电机的速度、位置控制、准确的读取电机的编码器信号。

-

FPGA

+关注

关注

1663文章

22493浏览量

638950 -

计算机

+关注

关注

19文章

7836浏览量

93444 -

总线

+关注

关注

10文章

3055浏览量

91856

发布评论请先 登录

【ZYNQ Ultrascale+ MPSOC FPGA教程】第十一章RS232实验

一文详解RS232、RS485、CAN总线

RS232 隔离 RS232

RS232、RS485、CAN总线隔离方案

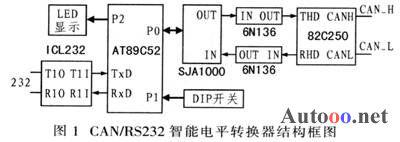

怎么实现RS232通信网络与CAN总线通信网络互联的设计?

基于采用SJAl000的CAN/RS232智能电平转换器设计方案

实现RS232串口通信的资料合集

采用RS232总线与FPGA实现三坐标测量系统的设计应用

采用RS232总线与FPGA实现三坐标测量系统的设计应用

评论