一 引言

TDI CCD能在不牺牲空间分辨率和工作速度的情况下获得高灵敏度,这个突出特点使其 在高速、微光领域具有广泛的应用前景。在科研任务中,新型TDI CCD器件研制时间过长、 供货不及时等原因会严重影响科研生产任务的进度。另外,TDI CCD器件的造价往往很高, 工艺复杂,并且有些新型TDI CCD器件的驱动要求复杂,多电源供电,上下电顺序严格,这 样在实验中就容易引起器件的损坏,造成巨大的损失。这些在电路的调试阶段经常发生。所 以我们迫切需要设计一种能在设备研制过程中和电路的调试阶段模拟实现TDI CCD器件电 性输入输出功能的模拟装置来解决上述问题。为此,本文设计了一种TDI CCD电性模拟器, 能在不用TDI CCD的条件下完成各种实验任务。

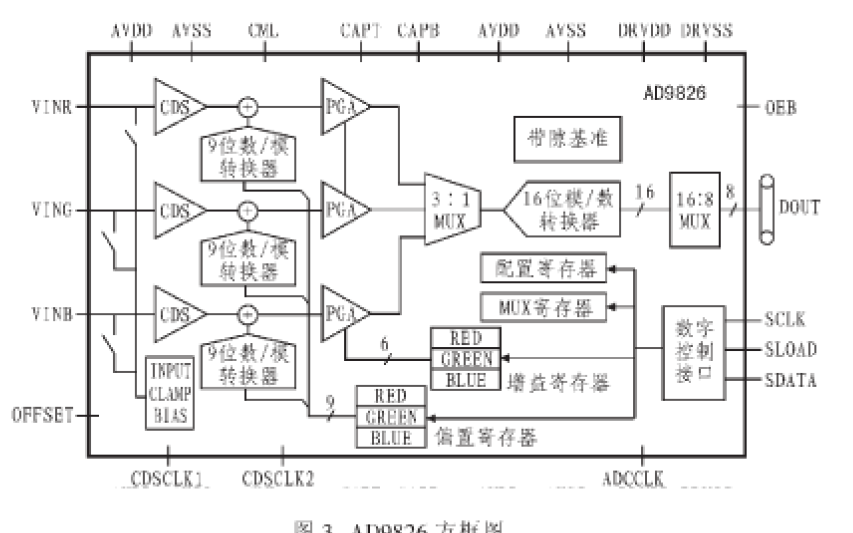

二 TDI CCD电性输入输出原理

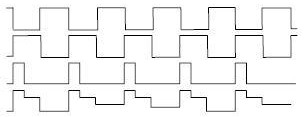

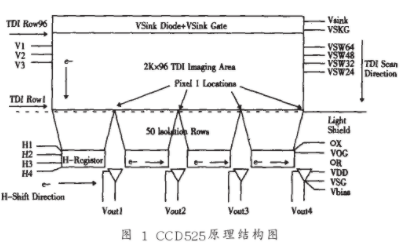

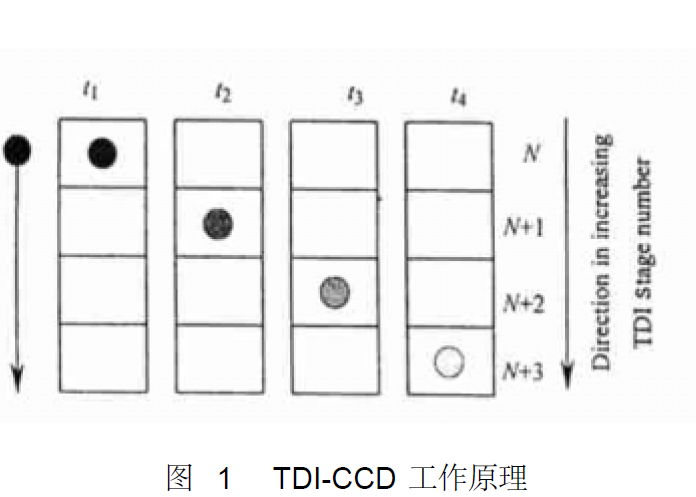

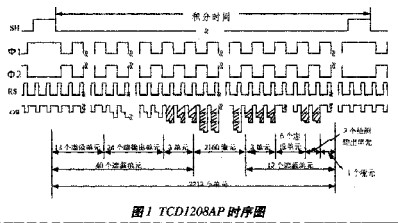

TDI CCD 为时间延迟积分型线阵CCD,它采用多次曝光的方法来提高灵敏度。本文以某 款新型TDI CCD 为例来说明其驱动与输出视频信号的关系。此TDI CCD 电性输入输出原 理如图1 所示。在其所有的驱动信号中,与输出有直接对应关系的主要是两相读出信号CR1、 CR2 和复位信号RST。其中CR1 和CR2 是完全倒相的关系。在图1 中,当TDI CCD 开始 读有效的视频信号时,输出视频信号OS 在每个RST 信号的上升沿时复位,即在输出视频 信号OS 上出现复位干扰脉冲A 段,然后立即回到参考电平B 段。TDI CCD 芯片在CR1 信 号的上升沿处开始读积分得来的像元信号反映在输出视频信号OS 上就是C 段。 A、B、C 三段即构成一个完整的TDI CCD 像元输出信号单元。由此可知,输出OS 信号的输出时序 由两个驱动信号CR1 和RST 信号决定。

对于大多数的 TDI CCD 来讲,驱动信号CR、RST 高低电平的相差幅度都是比较大的, 有时还有可能是负电平,输出信号OS 也都集中在比较高的电平上。例如本例中的TDI CCD 中CR 的高低电平各为10V 和0V,RST 的高低电平各为+3V 和-3V。输出OS 的范围是 +9V-+7V 之间,其中参考电平B 为+8V。设计TDI CCD 电性模拟器必须按照图1 所示 时序关系完成电输入输出功能,同时也要处理好电平大小关系。

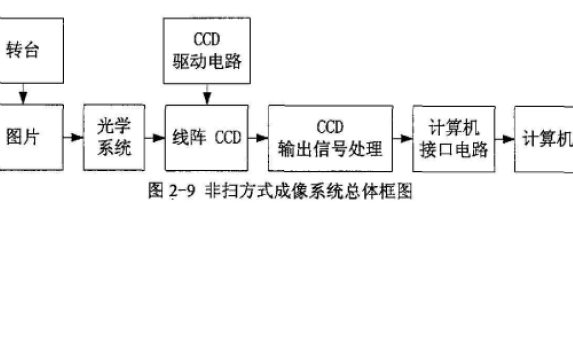

三 系统的原理及设计

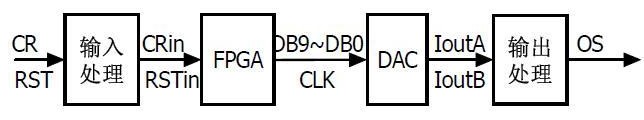

为了要按照图 1 所示模拟出TDI CCD 的电性输入输出关系,本设计所采用的方案是高速 运放作输入电平转换,用FPGA 作主控单元,高速DAC 作数模转换,高速运放作输出的结 构。如图2 所示,系统具体由四部分组成:输入处理电路、FPGA 单元、数模转换电路、输 出处理电路。其工作原理如下:输入处理电路把TDI CCD 驱动信号CR、RST 转化成可输 入的FPGA 信号Crin、RSTin,然后FPGA 单元再按照图1 的时序关系输出十位的数字信号 DB0~DB9 和时钟CLK 到DAC。再经DAC 进行数模转换之后输出是差分形式的模拟TDI CCD 信号,最后经由输出处理电路使其成为与TDI CCD 输出信号一致的视频信号OS。

3.1 输入驱动信号处理电路

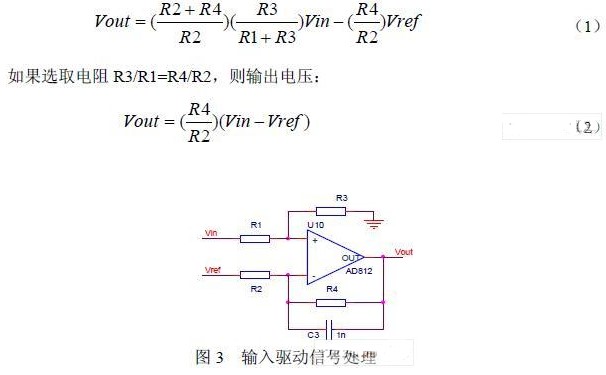

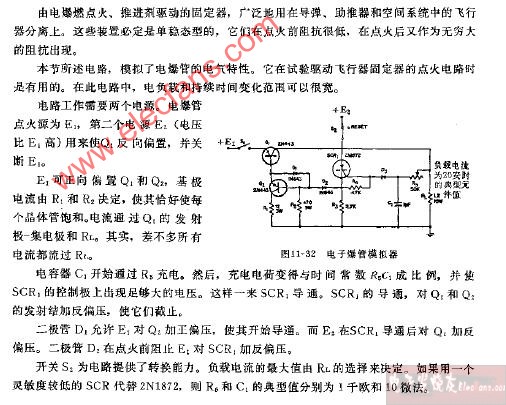

TDI CCD 芯片的输入驱动信号一般为电压差较大的两电平信号,且可能有负电平,不能 直接输入FPGA,必须先处理。如图1 所示,本设计中的TDI CCD 读出信号CR1、CR2 都 是+3V 到-3V 的两电平信号,电压差为6V。复位信号RST 的高低电平各为10V 和0V, 电压差为10V。所以采用的处理电路既要能提升负电平又要减小幅值,在本设计中采用高速 集成运放AD812 来实现这一功能[3]。如图所示:

依公式(2),图3 中引入Vref 就可以把驱动信号中的负电平提升到正区间来,适当的选 取Vref、R4/R2 值,就能使Vout 与FPGA 电平匹配。例如处理CR1 信号时,取Vref 为-3V,R4/R2 为0.5,把CR 接到Vin 上,则Vout 输出区间为0~3V。同理,将Vref 接地, R4/R2 为 0.3, 把RST 接到Vin 上,则Vout 输出区间为0~3V。这样就可以安全输入到FPGA 中。

3.2 FPGA 单元

FPGA 单元是本设计的核心器件,为保证系统的性能同时兼顾价格因素,本设计采用了 Xilinx 公司的高性能低成本FPGA 芯片Spartan3 XC3S50。它采用90nm 工艺技术以及300mm 晶圆,大大降低了FPGA 的成本。和其它同类器件相比,具有最低的价格而能提供更高的 容量和性能。设计语言采用Verilog HDL 硬件描述语言[4]。

FPGA 完成的功能是按照图1 所示输入输出信号的时序,由驱动信号CR 和RST 触发相应 的给DAC9750 的十位数字信号DB0~DB9 和时钟信号CLK。具体关系如前所述。其处理流 程如下:首先由时序判断电路来判断输入的驱动信号的上升沿。当有RST 的上升沿来时, 由其时序关系可知FPGA 的输出为图1 中A 段尖峰脉冲电平的十位数字信号。然后经计数 器延迟一小段时间后,输出为B 段对应的复位参考电平的十位数字信号。因CR1 与CR2 互 为反相关系,仅用一相CR1 来判断就可以。当有CR1 的上升沿来时,FPGA 的输出为C 段 视频信号电平对应的十位数字信号。此视频信号可根据不同的要求变化大小,可以是亮度渐 变的视频信号,也可以是预先设定的信号,这样既可以模拟出各种的TDI CCD 输出又可以 模拟叠加噪声,以满足不同实验的需要。

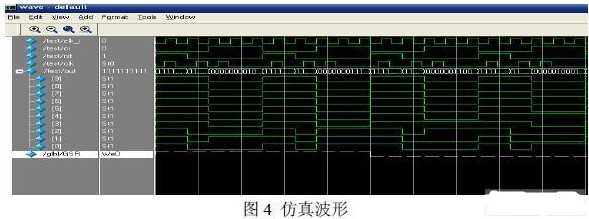

Verilog HDL 语言设计主要有三个模块:输入时序判断模块根据CR1、RST 的不同状态来 判定某一时刻的输出到底是图1 中的A,B,C 哪种状态。输出控制模块再把相应的输出转换 成DB9~DB0 和CLK,其中,对于有效状态C,可以去读取波形存储模块中的数据来满足不 同实验的需求。对于一个简单的应用,TDI CCD 输出频率为8Mhz 且输出为亮度递增,其 仿真波形如图4 所示:

由此可以看出,本设计还具有驱动时序检测的功能,当所用的驱动时序不是严格如图1 所示的时序的话,就不能输出正确的TDI CCD 视频信号。

3.3 数模转换

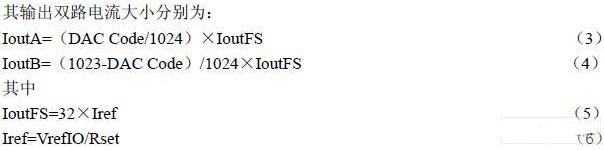

为保证 TDI CCD 的高速、低噪声要求,设计采用了Analog Device 公司的高速D/A 转换 芯片AD9750。它是一款双路电流输出型、最大输出电流为20mA、输出阻抗大于100MΩ、最大转换速率为125MSPS 的十位高速数模转换器。它接收由FPGA 产生的十位数字信号和 时钟信号,并把转成模拟信号以电流形式输出。为满足电路的低噪声要求,本设计采用了双 路差分电流输出[5]。

VrefIO 设为内部参考电压1.25V,取Rset=2kΩ,则IoutFS=20mA,为AD9750 的最大电流输出值。

3.4 输出处理

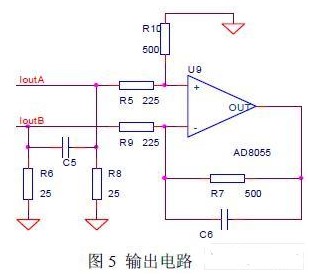

由 AD9750 产生的双路模拟电流差分信号要转换成相应的电压形式。AD9750 的输出负 载可以有多种形式,为了最大限度的保证信号精度,减少信号间干扰及噪声,设计中采用了 双路输出加到运算放大器AD8055 上的结构。如图5 所示: AD9750 的输出IoutA 及 IoutB 分别接25Ω的负载。电容C5 起到低通滤波和减小运算放大器的输出失真的作用。这样双路 差分信号经AD8055 转成单端信号输出。

由 AD8055 输出的电压信号的幅值范围为:-1V~+1V,TDI CCD 视频输出信号的范围大约 在+9V~+7V 之间,所以要经过一个电压提升的电路使输出符合要求。所采用的电路如图3 所示的电路结构。把一个-8V 的直流电平接到反相端,AD8055 的输出信号接到同相端。 放大倍数为1,最后得到的输出即是TDI CCD 视频信号。

3.5 提高信号信噪比

按照上述方法,可以由TDI CCD 的驱动得到相应的视频输出信号。但是由于TDI CCD 的 工作频率比较高,使得整个系统的工作频率都很高。所以,如何去除掉干扰和噪声,提高信 号质量是本设计的重要问题。为此,采取了以下措施:

PCB 板布局是产生干扰的,也是去除干扰的关键。本设计重点考虑FPGA 与高速 DAC 以及输出运放之间的布局。尽量减少高速信号线的线长,特别是FPGA 与高速DAC 之间的线长。对电源滤波,减少电源带来的干扰。合理设计地平面,采用数字地和模拟地分 开的方式,减少各器件间的干扰。

四 结束语

本文设计的TDI CCD 电性模拟器能模拟出TDI CCD 芯片的电性输入输出功能,同时具有 一定的驱动时序检测功能,它能替代昂贵的TDI CCD 芯片完成部分相关的实验工作,且功 能基本满足要求。

-

芯片

+关注

关注

455文章

50816浏览量

423651 -

CCD

+关注

关注

32文章

881浏览量

142266 -

模拟器

+关注

关注

2文章

875浏览量

43224

发布评论请先 登录

相关推荐

基于CPLD芯片MAX7000AE实现TDI/CCD驱动时序的设计

高速EM CCD图像传感器CCD97时序驱动电路的设计方法

TDI-CCD图像传感器

一种多普勒模拟器的设计与实现The Design and I

TDI-CCD图像传感器电荷包总转移效率分析

基于FPGA 的TDI-CCD 时序电路的设计

线阵CCD驱动时序及模拟信号处理的设计

基于CPLD的CCD相机图像信号模拟器的设计

使用FPGA实现线阵CCD驱动时序及模拟信号处理的设计说明

CCD的工作原理和几种产生CCD驱动时序方法

如何分析高分辨力TDI-CCD遥感相机的特性

使用TDI CCD芯片的电性模拟器可进行驱动时序检测

使用TDI CCD芯片的电性模拟器可进行驱动时序检测

评论