引言

某型导弹测试设备电路板检测仪主要完成该测试设备的电路板的故障检测。该检测系统要求激励信号产生电路体积小,配置灵活,且精度高、转换速度快。基于FPGA的DDS信号发生器较传统信号发生器能够更好地满足检测仪要求。

直接数字频率合成(Direct Digital Synthesize,DDS)是从相位概念出发直接合成所需波形的一种频率合成技术。它是继直接频率合成和间接频率合成之后发展起来的第三代频率合成技术,突破了前两代频率合成法的原理,从“相位”的概念出发进行频率合成,这种方法不仅可以产生不同频率的正弦波、方波、三角波,而且可以控制波形的初始相位,还可以用此方法产生任意波形,目前得到了广泛的应用。

1 DDS的工作原理和基本结构

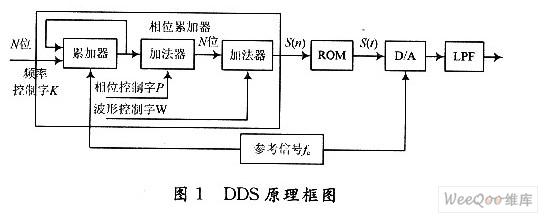

一个直接数字频率合成器由相位累加器、加法器、波形存储ROM、D/A转换器和低通滤波器构成。DDS的原理框图如图1所示。

图1中K为频率控制字,P为相位控制字,W为波形控制字,fc为参考时钟频率,N为相位累加器的字长,D为ROM数据位及D/A转换器的字长。相位累加器在时钟,fc的控制下以步长K作累加,输出的N位二进制码与相位控制字P,波形控制字W相加后作为波形ROM的地址,对波形ROM进行寻址,波形ROM输出D位的幅度码经D/A转换器变成阶梯波,再经过低通滤波器平滑后就可以得到合成的信号波形。合成的信号波形形状取决于波形ROM中存放的幅度码,因此用DDS可以产生任意波形。

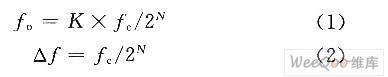

设频率控制字是K,输出频率为f0,参考时钟是fc,相位寄存器为N位,频率分辨率是△f,则有:

通过频率控制字的改变和寄存器位数的增加,可以得到令人满意的频率。

2 基于FPGA的DDS信号发生器的设计

该信号发生器是作为电路板检测仪的激励信号源,产生的信号分别为:频率为16 000±0.8 Hz的正弦波,频率为128 000±* Hz,64 000±3.2 Hz,4 000±O.2 Hz的方波和周期为10μs,占空比为1:4的脉冲信号。下面以正弦波的产生为例说明DDS的实现过程。当f0=16 000 Hz,N=16时,根据式(1),则K=104。

2.1 相位累加器

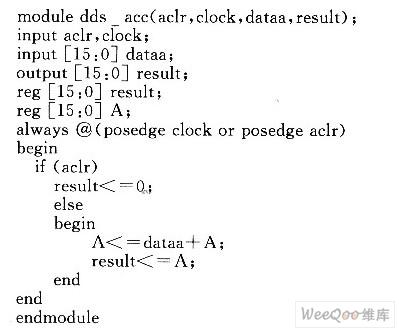

相位累加器主要是根据频率控制字生成ROM查找表的地址,采用硬件描述语言Verilog DHL实现,其源程序为:

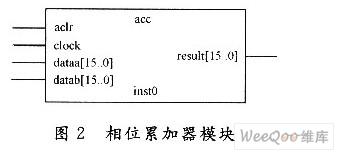

文本输入完毕后,用QuartusⅡ进行编译,然后生成.bsf文件,以便在顶层设计时调用。其生成顶层模块如图2所示。

2.2 ROM查找表

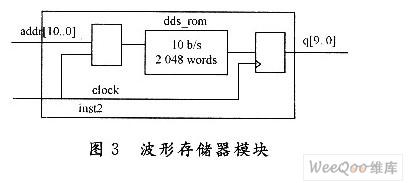

DDS中,波形存储器的设计是比较关键重要的一环。用相位累加器输出的数据作为波形存储器的地址,进行波形的相位与幅值的转换,即可在给定的时间上确定输出波形的幅值。N位的寻址ROM相当于把O°~360°的周期信号离散成具有2N个样值的序列,若波形ROM有D位数据位,则2N个样值的值以D位二进制数值存放在波形ROM中,按照地址的不同可以输出相应相位的正弦波和方波的值。在本设计中取N=11,则ROM查找表中存储2 048个波形数据,位宽为10位。

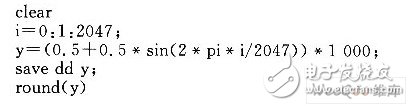

建立ROM查找表首先要生成.mif文件。具体方法是利用quartusⅡ新建.mif文件,然后填写这个文件。这里需借助Matlab填写.mif文件即可,具体方法如下:

(1)先由QuartusⅡ生成.mif文件。

(2)在Matlab中编写如下程序:

(3)在Desktop中workspace中选中数据,复制数据并将数据粘贴于txt文档中,保存。

(4)然后再将txt文档中的数据复制并粘贴于QuartusⅡ中已建好的.mif文件之中,保存。

调用的波形存储器模块如图3所示。

2.3 顶层模块的建立

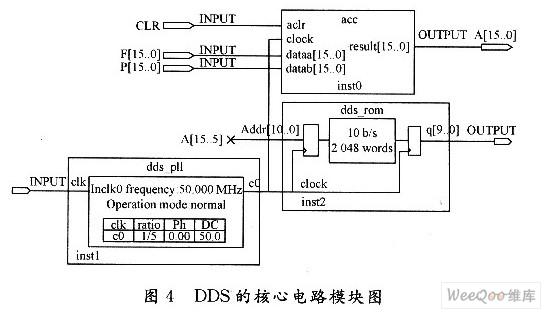

根据DDS整体电路的工作原理框图,其核心是由一个ROM存储器、一个相位累加器、一个锁相环和相应的输入、输出信号组成。其中ROM查找表是输入地址是相位累加器的高11位,这在工程上是允许的。DDS的核心电路模块图如图4所示。

方波和脉冲信号的产生只要将ROM查找表中的内容转换为相应的波形即可,整个信号源的顶层模块增加了多路选择开关。

3 波形仿真及硬件验证

完成DDS电路设计后,对电路进行了功能仿真,通过Matlab显示了仿真波形,并通过Altera公司CycloneⅡ系列芯片的DE2-70开发板结合嵌入式逻辑分析仪进行了硬件验证。

3.1 波形仿真

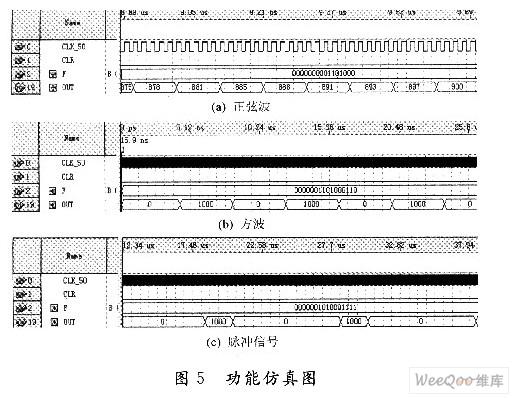

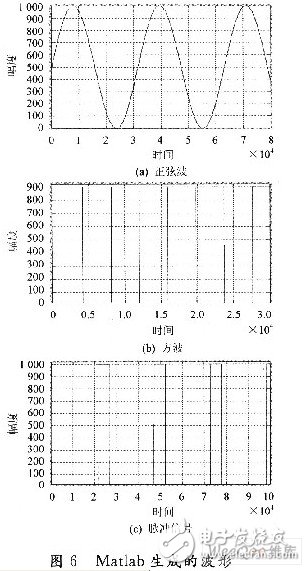

DDS电路在设计过程中,进行了功能仿真,如图5所示。由于仿真波形为数字码,不能直观地看出DDS输出的波形,为便于调试设计电路,首先生成.tbl文件,再通过相应Matlab程序生成的正弦波、方波、脉冲信号的波形曲线,如图6所示。

图5和图6显示了频率控制字为68h产生的正弦波、频率控制字为346h的方波和频率控制字为27Fh的脉冲信号的功能仿真波形。从功能仿真波形可以看出,DDS电路能够很好地产生电路板检测仪所需激励信号。

3.2 硬件验证

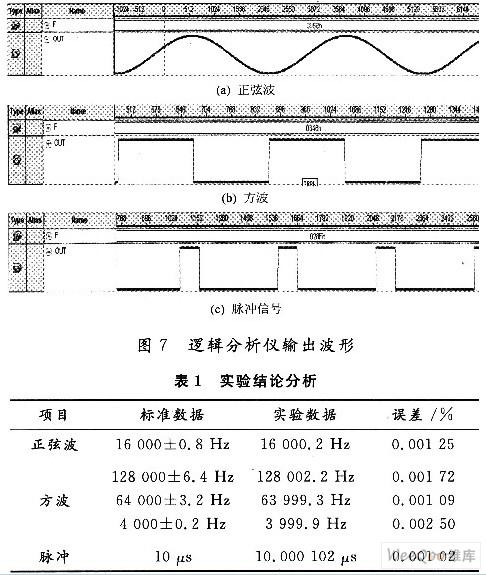

为了能够更清晰地分析DDS电路,采用DE2-70开发板结合SignalTapⅡ型嵌入式逻辑分析仪对设计进行实时的硬件验证。首先对DDS顶层电路图做部分修改,主要是进行管脚设定。将修改后的顶层文件下载到DE2-70中,通过SignalTapⅡ型嵌入式逻辑分析仪实时观测FPGA输出波形,如图7所示。SignalTapⅡ所能显示的被测信号的时间长度为T,计算公式如下:

式中:N为SignalTapⅡ的缓存中存储的采样点数,Ts为SignalTapⅡ采样时钟的周期。由图7和式(3)可得出表1所示结论。

产生误差的主要原因有两方面,一是截断误差,ROM查找表的地址输入是相位累加器的高11位;二是正弦波量化引入的误差,将正弦信号量化为二进制数必然引起误差。

4 结语

通过对DDS电路的功能仿真和硬件验证,可以看出DDS可以有效地产生所需波形信号。较传统的信号发生器,可以减小体积、降低功耗、提高可靠性和灵活性并缩短了开发周期,具有较高的实用价值。

-

FPGA

+关注

关注

1629文章

21729浏览量

602993 -

频率合成器

+关注

关注

5文章

219浏览量

32350 -

DDS

+关注

关注

21文章

633浏览量

152630

发布评论请先 登录

相关推荐

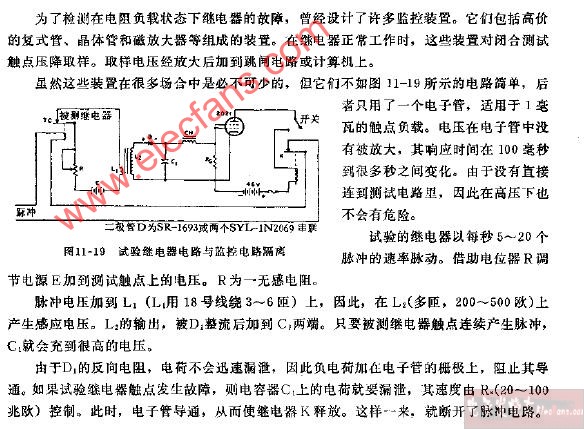

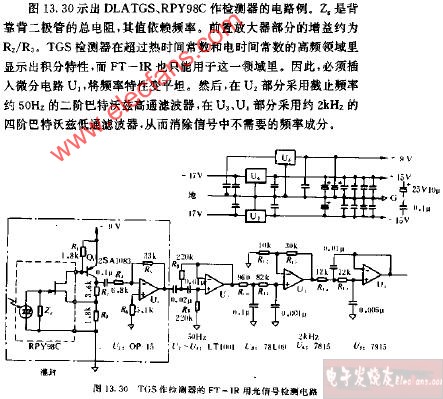

移动电源电路板 故障检测

红外检测器,红外检测器是什么意思

采用VXI总线仪器实现对电路板进行故障检测和诊断

利用DDS信号检测器进行电路板的故障检测

利用DDS信号检测器进行电路板的故障检测

评论