1 、数据合并转换器硬件电路

1.1 主要硬件简介

EPM7128是可编程的大规模逻辑器件,为ALTERA公司的MAX7000系列产品,具有高阻抗、电可擦等特点,可用门单元为2500个,管脚间最大延迟为5ns,工作电压为+5V。

IDT7205为FIFO型异步读写的存储器芯片,容量为8192×9比特,存取时间为12ns,有空、半满、满三个标志位,最大功耗为660mW,工作电压为+5V。

MSM486DX属于PC104嵌入式系统的5X86系列,为AMD-133MHz CPU,具有COM1、COM2两个串口,一个LPT并口,一个FLOPPY接口,一个IDE接口,一个VGA/LCD接口,一个AT-KEYBOARD 接口,16个中断,额定功率为8W,工作电压为+5V。

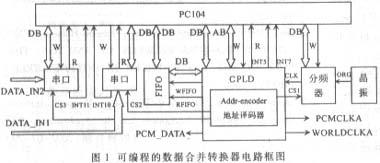

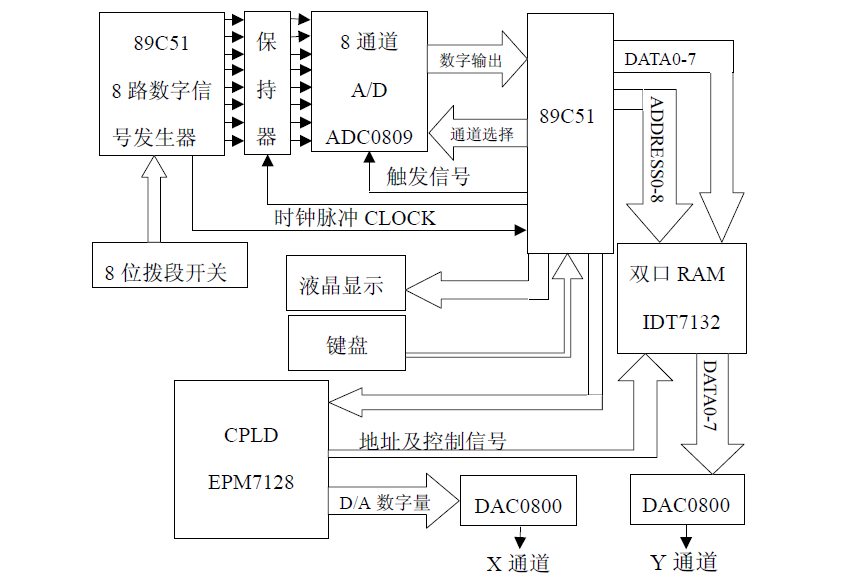

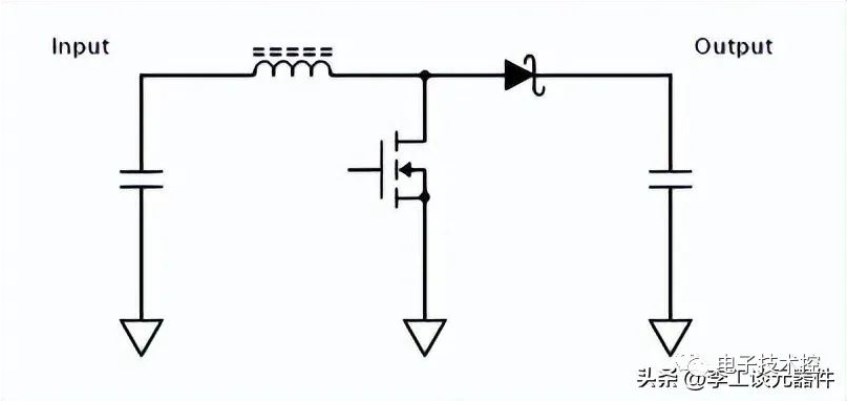

1.2 数据合并转换器电路框图

可编程的数据合并转换器电路框图如图1所示。图中,DB为数据总线,AB为地址总线,R和W分别为读写信号线,INT5、INT7、INT10和INT11为四个中断,CS1、CS2和CS3是在CPLD内部生成的地址译码器Addr-encoder分别送给分频器、两个串行口的片选信号,ORG是晶振送给分频器的振荡脉冲,CLK 是分频器输出的脉冲FRAMECLK和PCMCLK,WFIFO、RFIFO是由CPLD生成的包含地址信息的访问FIFO的读写脉冲, DATA_IN1和DATA_IN2为串行口输入数据,PCM_DATA是数据合并转换器输出的PCM流,PCMCLKA为输出的码同步时钟,WORLDCLKA为输出的字同步时钟。

1.3 电路工作分析

晶振把时钟脉冲送给分频器,分频器含有两个可编程的定时器。分频器把可控的FRAMECLK和PCMCLK送给CPLD,在CPLD内部经过逻辑组合形成三路脉冲信号,一路控制计数器形成INT5、INT7两个帧频中断触发脉冲,CPU接到中断后立即写FIFO;另一路控制移位寄存器把并行数据转换成串行数据PCM流;第三路形成RFIFO去连续读FIFO。两个串行口通过中断方式(INT10、INT11)接收到外部数据后,暂存缓冲区内,按一定格式由中断INT5控制写给FIFO。

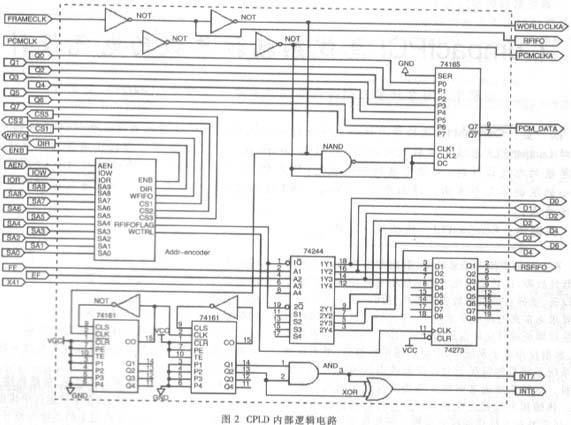

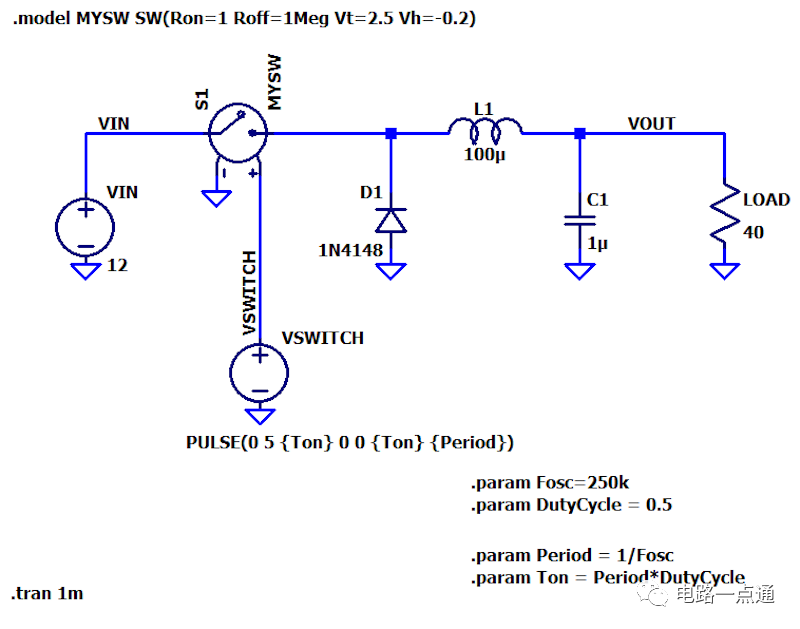

2 、CPLD内部逻辑电路

CPLD内部逻辑电路如图2所示。图中,虚线框内为CPLD内部电路,虚线框外为CPLD的I/O口。

2.1 地址译码器

地址译码器Addr-encoder用VHDL语言生成。Addr-encoder的输出有总线驱动器芯片74245的使能脉冲ENB,总线传输方向的使能脉冲DIR,写FIFO操作脉冲WFIFO,分频器和串行口的片选CS1、CS2和CS3,FIFO数据空满标志脉冲RFIFOFLAG,FIFO复位时钟脉冲WCTRL。

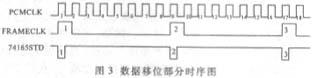

2.2 数据移位部分

FRAMECLK周期是PCMCLK 的8倍,它们都是分频器送来的脉冲。FRAMECLK反相后作为FIFO的读信号,两次反相后作为字同步时钟。PCMCLK直接作为移位寄存器74165的时钟触发脉冲,两者与非后的输出低电平作为74165重装载数据的触发电平。它们的信号时序如图3所示。

从三者的时序图可知,每当一个字节的最后一位完成移位后,在FRAMECLK脉冲反相的下降沿触发下读取FIFO数据,这时74165的装载使能74165STD恰好为低电平(与非结果),完成新数据装载,然后在PCMCLK脉冲的上升沿作用下开始新一轮次的数据移位。

2.3 帧长计数器部分

两个74161设计成1/64的分频器,也叫帧长计数器,此计数器的时钟为FRAMECLK,计数器的输出最高两位逻辑与为中断INT7,把与门输出与次高位逻辑异或为中断INT5。这样,INT7比INT5在时序上早半个周期。开机复位后,INT7脉冲首先产生,触发中断,CPU中断后在服务程序中把64个字节数据写到FIFO,然后屏蔽中断INT7,半个周期后,FIFO中还剩32个字节数据(因为FIFO的读脉冲和FRAMECLK反相同频)。然后中断INT5到来,CPU响应后,再写64个字节数据给FIFO,使FIFO中一直保持有数据的状态(可避免读FIFO正好落在两个写FIFO之间,FIFO因无数据而读死)。这样,每当中断INT5到来,都写64字节给FIFO,周而复始,所以把64字节定为帧长。

设PCMCLK的频率为f(MHz),则FRAMECLK的频率为f/8,由于帧长为64,所以有:帧频=f/(8×64),PCM流速率=f(bit/s)。分频器的分频比是通过软件设定的,所以PCM流的速率可编程。

3 、软件设计

分频器编程:

outp(0x303,0x36)://方式3,方波。//

outp(0x300,0x50);//timer0,分频比为80。//

outp(0x300,0x00);

outp(0x303,0x74);//方式2,脉冲。//

outp(0x301,0x08);//timer1,分频比为8。//

outp(0x301,0x00)

数据合并:

if((com1_count%24)==0) ;//串行口1的24字节数据放在

数组Frame的4~27的位置。//

{

com_buf1[com1_count++]=db1;

//串行口1接收数据//

int Original_Counter

Original_Counter=com1_count/24

memcpy(Frame[Original_Counter-1]+4,&com_buf1[com1_count-24],24);

if((com2_count%24)==0) ;//串行口2的24字节数据放在

数组Frame的28~51的位置。//

{

com_buf2[com2_count++]=db2

;//串行口2接收数据//

int Original_Counter;

Original_Counter=com2_count/24;

Memcpy(Frame[Original_Counter-1]+28,&com_

Buf2[com2_count-24],24) ;//合并后的数据放在Frame

数组中。//

写FIFO:

void Send_To_Fifo(int number); //Send_To_Fifo函数为中断

服务程序的一部分。//

{

for int i=0;i《64;i++)

outp(WFIFO Frame[number][i]; //数组送给FIFO,

实现数据合并//

}

责任编辑:gt

-

芯片

+关注

关注

457文章

51350浏览量

428305 -

转换器

+关注

关注

27文章

8755浏览量

148304 -

分频器

+关注

关注

43文章

448浏览量

50109

发布评论请先 登录

相关推荐

请问谁有epm7128的tqfp封装的管脚定义分布图啊?官网只有84脚的!!

基于QCM传感器的生物芯片检测电路的设计

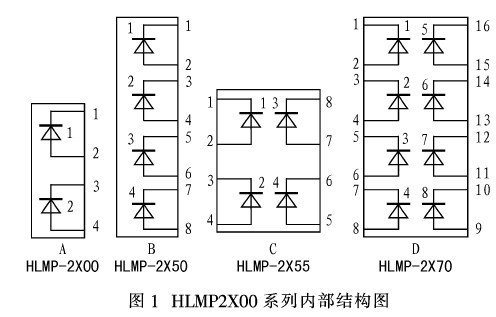

基于EPM7128和HLMP2X50的键盘编码显示电路

基于EPM7128SLC84实现的AD574A采样控制器

EPM7128在光栅位移测量仪中的应用

TMS320LF2407型DSP和EPM7128型CPLD在移动

使用51单片机和EPM7128设计实现简易逻辑分析仪的论文免费下载

数据合并转换器电路的工作原理分析及如何采用EPM7128芯片实现

数据合并转换器电路的工作原理分析及如何采用EPM7128芯片实现

评论