引 言

微小卫星促进了专用集成电路(ASIC—Application Spceific Integrated Circuit)在航天领域的应用。现场可编程门阵列(FPGA —Field Programable Gate Array)作为ASIC的特殊实现形式,是中国航天目前集成设计的最佳技术选择,也是中国微小卫星发展的必由之路。

微小卫星对其功耗、质量和体积提出了较苛刻的要求,因此采用FPGA片内冗余容错代替片外冗余容错,是实现系统可靠性指标的另一种好办法。

应用于空间环境的FPGA,其时序逻辑需要防范空间粒子辐射引起的单粒子翻转,片内三模冗余(TMR) 是应对单粒子翻转的主要手段。因此,采用FPGA片内冗余容错方式提高可靠性,是非常必要的。

和其它集成电路一样,FPGA内部存在制造缺陷。研究发现这些缺陷的空间分布是不均匀的,表现出成团性。FPGA内部缺陷成团对FPGA片内冗余容错设计会产生负面影响,需要开展针对性的研究并提出应对策略,以提高FPGA片内冗余容错设计的有效性。

缺陷成团的相关研究

缺陷成团在电子系统设计领域还未被充分认识和重视,但作为集成电路制造领域的研究课题,却有相当长的研究历史。

(1) 集成电路缺陷类型

FPGA等集成电路(IC—Integrate Circuit)在制造过程中会产生缺陷。制造缺陷分成全局缺陷和局部缺陷。全局缺陷可以控制,但局部缺陷呈现随机性,难以避免,并随着芯片面积的增大而增加。在出厂测试中可以检测出绝大部分的局部缺陷,但有一些局部缺陷由于其影响一时未能显现而通过了检测设备的检测,这些局部缺陷经过一段时间的使用后会逐步扩展,引起电路故障。空间飞行器选用的FPGA,尽管经过了严格的考核和筛选,但由于其工作于恶劣的太空环境,仍然会诱发潜在的微小缺陷,引起电路故障,从而对航天电子产品的可靠性构成严重威胁。

(2) 集成电路缺陷的空间分布及成品率预计模型

局部缺陷降低了IC的成品率(Manufacturing Yield),为此需要在成品率预计的基础上采用相应的冗余容错措施,以满足生产成品率要求。

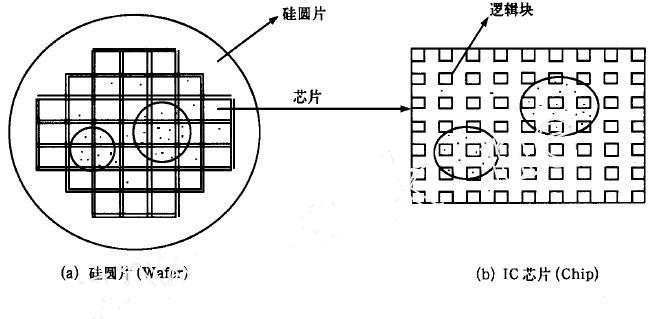

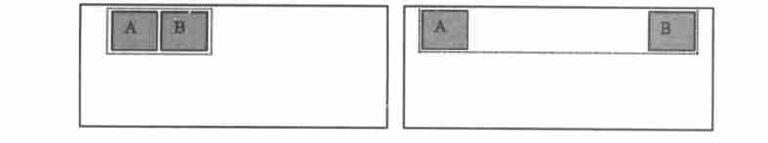

IC芯片(Chip)制作在一定尺寸的硅圆片(Wafer)上,若干个IC芯片在Wafer上按行、列整齐排列,每个芯片内部含有若干个逻辑块(Logic Block)。FPGA、CPLD、存储器等IC芯片,其构造逻辑块在内部也是按行、列整齐排列的。图1(a)是硅圆片示意图,内部整齐排列着芯片;图1(b)是FPGA芯片的示意图,内部排列着逻辑块,逻辑块之间是布线通道。

图1 硅圆片、芯片及内部缺陷分布示意图

早期研究认为,在Wafer和IC内缺陷的空间分布是均匀的。假定一个IC芯片内部含有n个逻辑块,每个逻辑块的平均可靠度为p。对于内部无冗余容错的IC,成品IC必须是n个逻辑块均无故障。设P为其预计成品率,则成品率预计模型为

![]()

在IC中有规律地增加一些备用逻辑块,用这些备用逻辑块代替故障逻辑块,以提高IC成品率。假定IC有n个逻辑块,其中r =n - k ,为备用逻辑块,IC是成品的条件是n个逻辑块中有k个以上无故障,其概率为

![]()

因此采用冗余容错电路IC的成品率预计模型为

![]()

式(2)是IC成品率预计的二项式分布模型。用此模型预计IC成品率,预计值与实际值存在较大差异。大量实验观测发现,二项式分布成品率预计模型不准确的根源在于IC内部缺陷的空间分布是不均匀的,呈现成团效应(Clustering)。缺陷成团的主要原因是IC工艺的批次性,工艺条件会随着时间和空间发生变化,导致IC芯片的批次之间,同一批的圆片与圆片之间,甚至是同一圆片的芯片与芯片之间,缺陷的分布都不同。逻辑块的可靠度p不是常数,而是随机变量。

缺陷成团的表象如图1 所示,图中黑点代表缺陷,圆框标注的是一个缺陷团。缺陷团面积是个随机值,大面积缺陷团可以覆盖整个圆晶片,小面积缺陷团局限在一个芯片内,覆盖相邻的若干逻辑块。

缺陷成团使得邻近逻辑块的缺陷存在相关性。要建立反映缺陷成团性的成品率预计模型,需要对复杂的多变量联合概率密度函数积分,可见用解析方法求得成品率几乎是不可能的。因此,通常采用数学逼近的方法,依靠系列可解析函数逼近成品率预计模型。

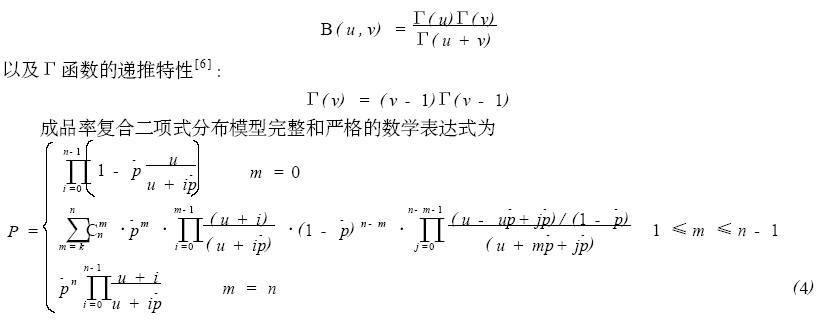

成品率预计的负二项式分布模型和复合泊松(Poisson) 分布模型,如Neymann TypeA ,Poisson Binomial 分布模型,由于考虑了缺陷的成团性,都能较准确地预计成品率。Stapper等假定p服从B分布,提出成品率复合二项式分布模型,这一模型不仅可以较准确地预计IC成品率,而且便于分析计算。成品率复合二项式分布模型为

![]()

式中p-是p的均值,u是B分布的一个参数。

式(3)与式(2)相比,是在式(2)的基础上增加了一个含参数u、p-的比例因子,从而反映出缺陷成团对成品率的影响。

缺陷成团对FPGA片内冗余容错电路可靠性的影响

卫星电子系统的功能电路布局于FPGA内,功能电路由芯片内的若干简单逻辑块构成。为提高功能电路的可靠性,往往需要在片内对功能电路整体采取冗余容错措施,如最常用的单备份冗余容错形式。冗余容错电路包括主份电路、若干备份电路和切换电路,其可靠性是由主份电路、备份电路和切换电路共同决定的。如果主份和备份电路远比切换电路复杂,则可以忽略切换电路对冗余容错电路可靠性的影响,以下的讨论就是针对这一情况进行的。

对于冗余容错电路,不允许主份和备份电路都出现故障,引起冗余容错电路失效。因此有必要采取措施,尽可能降低冗余容错电路的失效率。

无论是FPGA内逻辑单元一类的简单逻辑块,还是处理器阵列中的处理器单元(PE)一类的复杂逻辑块,都可以采用成品率复合二项式分布模型分析其成品率。若把冗余容错电路的主份和备份电路分别看成是片内的一个复杂逻辑块,则可以用此模型分析缺陷成团对冗余容错电路可靠性产生的影响。

复合二项式分布模型的数学推导

经分析,式(3)给出的成品率复合二项式分布模型表达式存在错误,Stapper在文献中没有给出推导过程,因此首先从数学上对此模型进行了严格推导。推导的关键是利用Γ函数与B函数的关系:

缺陷成团对冗余容错电路可靠性影响分析

式(4)中的第三项对应n冗余容错电路的无故障概率Pn为

![]()

式(4) 中的第一项对应n 冗余容错电路的失效率Qn 为

![]()

分析式(5) 、(6) ,当参数u 趋近于无穷大时

![]()

当参数u 趋近于零时

![]()

式(7)、(8)表明,当参数u 趋近于无穷大时,Pn和Qn的值等于缺陷均匀分布时的值,说明此时缺陷不具备成团性,而是呈均匀分布状态; 式(9)、(10)表明,当参数u趋近于零时,Pn和Qn的值分别等于主份电路的可靠度和共效率。

参数u反映了IC 内部缺陷成团性的强弱,称为模型的成团因子。u 越大,缺陷成团性越弱;u 越小,缺陷成团性越强。

进一步分析表达式(5)、(6),对于任意的u》0 ,由于

缺陷成团时片内冗余容错电路的无故障概率和失效率比缺陷均匀分布时的都要高。缺陷成团性增大了冗余容错电路的失效率,削弱了冗余容错的可靠性增长功效。

其值随参数u增大而增大,因此失效率Qn随参数u增大而减小,并且在u=0时取得最大值。成团因子u越大,冗余容错电路的失效率越低、可靠性就越高。这一结论对冗余容错电路可靠性设计具有重要指导意义。

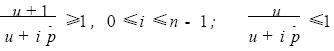

成团因子

缺陷成团性强弱可以理解为缺陷相关性的强弱。缺陷成团性越强,缺陷相关性就越强,成团因子越小,反之亦然。若应用式(4)分析一个冗余容错电路,则成团因子反映的是冗余容错电。路内缺陷的平均相关度缺陷团面积是个随机值,当冗余容错电路面积小于最小缺陷团面积时,相应成团因子的值只取决于缺陷团内缺陷相关性的强弱,与冗余容错电路面积无关;当冗余容错电路面积大于最大缺陷团面积时,此时成团因子不仅受缺陷成团性强弱的影响,而且随冗余容错电路面积的变化而变化。

图2 成团因子α与冗余容错电路面积的关系

IC成品率预计常用到负二项式分布模型,此模型中的参数α是模型的成团因子。Stapper采用回归分析法分析验证成团因子α,得出成团因子与冗余容错电路面积的关系,如图2所示。曲线中的OA水平直线段表示α维持不变,对应冗余容错电路面积小于所有缺陷团面积的情况;曲线中的BC直线段表明α与冗余容错电路块面积成正比,对应冗余容错电路面积大于所有缺陷团面积的情况; 曲线中的AB曲线段表明α随冗余容错电路面积增大而呈现非线性增长,此时冗余容错电路面积介于最小缺陷团面积和最大缺陷团面积之间。

在没有缺陷团面积数据时,一般假定FPGA内缺陷团面积小至逻辑块,大至整个芯片,并且在这范围内连续分布。此时图2中的点A、B分别趋近点O、C,在曲线整个范围内,成团因子随冗余容错电路块面积增大而呈非线性增长。

实验数据表明,在冗余容错电路面积小于所有缺陷团面积时,成团成子u维持不变。成团因子α和u物理意义相同,遵循相似的变化规律。

缺陷成团时提高冗余容错电路可靠性的策略

冗余容错电路的主份和备份电路布局于FPGA芯片内。当FPGA内缺陷成团时,可以通过调整布局,增大主、备份电路的几何距离,降低冗余容错电路的失效率。

分析表明,在缺陷成团时,冗余容错电路的失效率取决于所对应成团因子的大小。成团因子决定于冗余容错电路的等效面积。冗余容错电路的等效面积等于涵盖整个冗余容错电路的最小面积,如图3所示。增大主、备份电路的几何距率,就是增大冗余容错电路的等效面积,从而增大对应成团因子的值。增大成团因子,就能降低冗余容错电路的失效率,提高其可靠性。

图3 冗余容错电路布局示意图

提高冗余容错电路可靠性策略的定量分析

由于成团因子与冗余容错电路等效面积之间存在复杂非线性关系,无法为上述策略建立分析模型进行定量分析。但当FPGA内只有小于冗余容错电路面积的缺陷团,且成团因子与冗余容错电路等效面积成线性关系,或者可以用线性关系近似时,则可以建立相应的分析模型进行定量分析。

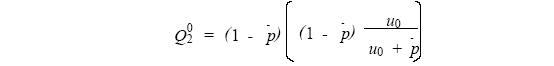

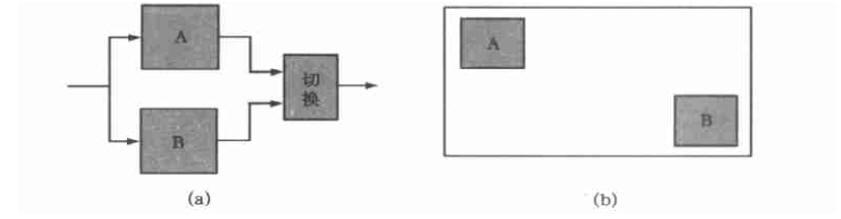

考虑一个单模块单备份容错电路,如图3 所示。A 是主份电路,B 是备份电路。如果单纯考虑信号时延,则布局时应将主、备份电路相邻排列。称这一布局为单模块单备份容错电路的基本布局,基本布局的等效面积为2S0(S0为主份电路面积) ,此时主、备份电路之间的距离为0,对应成团因子为u0,则有基本布局的失效概率Q02为

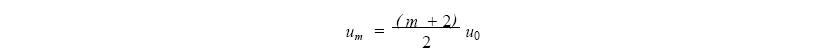

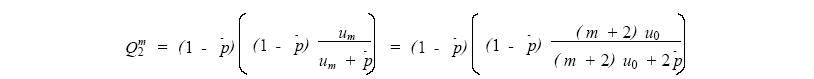

增大主、备份电路的距离,在主、备份之间留有面积等于m 个主份电路面积的空间。此布局为调整布局。调整布局的等效面积为(m+2)S0 ,此时主、备份电路之间的距离为m ,对应成团因子为um 。

um 和u0有如下关系

调整布局的失效率Qm

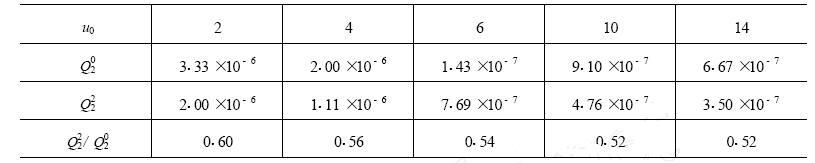

无论成团因子u0取何值,调整布局都能够降低冗余容错电路的失效率。表1 数据反映的是基本布局和特定调整布局(m=2)失效率随成团因子u0的变化情况,主份电路的可靠度p-=0.99999。

在成团因子较宽的一个变化范围内,特定调整布局(m=2)失效率比基本布局失效率降低了约1/2。

表1 失效率随成团因子u0 变化表

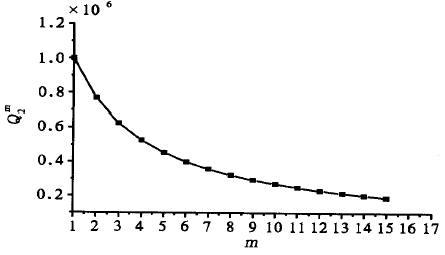

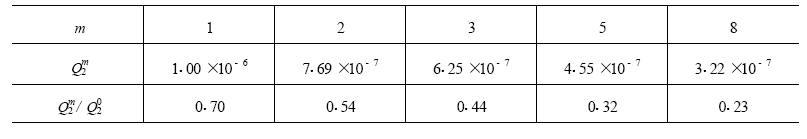

图4 冗余容错电路失效率随距离变化关系

冗余容错电路的主、备份电路间距离越大,冗余容错电路失效率越低。图4是冗余容错电路失效率随主、备份电路之间的距离变化(m变化)的情况,曲线对应的主份电路可靠度p-= 0.99999,成团因子u0=6。

表2 列出了不同布局失效率的具体改善数据,当m=8时,失效率约为基本布局的1/5。

表2 冗余容错电路失效率随布局变化表

缺陷成团时芯片内备份电路的优化布局原则

每种冗余容错方式,在FPGA的矩形(含正方形) 芯片内实现时,可以选择不同的布局方案。应用本章提出的策略,针对常用的几种冗余容错方式,从可靠性角度提出了最佳的一个布局方案。

图5(a)是单模块单备份容错形式。按图5(b)所示,将主、备份电路沿芯片对角线布置,可以获得最低的失效率。切换电路布置在与主、备份电路距离相同的位置上,保证切换电路的两路输入信号时延基本相同。主、备份电路的输入分别从就近的芯片引脚输入,避免占用内部大量的互连资源。两引脚再通过PCB板上的印制线相连。

图5 单模块单备份容错形式布局

布局、时延与资源利用率

依据本章提出的策略进行布局,冗余容错模块之间存在较大的空间,在这空间里可以布置其他功能电路。但是冗余容错模块之间的长距离信号连接需要消耗FPGA内有限的连线资源,往往由于连线资源消耗殆尽,无法继续布置其他的功能电路,从而降低了芯片逻辑资源的利用率。因此,冗余容错模块可靠性的提升也是以牺牲资源为代价的。解决这一问题的一个有效办法是利用FPGA丰富的输入输出管脚资源,将片内的长线连接改为片外PCB板印制导线的连接。

无论是片内的还是片外的长线连接,都势必引起较大的信号时延,这会限制电路的最高工作频率,但随着FPGA性能的不断改善,信号时延问题会逐步缓解。

结束语

基本FPGA的片内冗余容错将会是提高微小卫星可靠性的重要手段。随着FPGA规模的增大和集成密度的提高,内部缺陷发生的概率也在增大,因此研究缺陷成团性对片内冗余容错的影响,具有较重要的工程价值。后续工作需要研究缺陷成团对一些常用片内冗余容错方式如TMR的影响,提出相应的应对策略。在此基础上再进一步探讨在电子设计自动化环境下,高效实现应对缺陷成团性策略的方法。

-

FPGA

+关注

关注

1664文章

22571浏览量

640655 -

可编程

+关注

关注

2文章

1336浏览量

41578 -

卫星

+关注

关注

18文章

1886浏览量

70505

发布评论请先 登录

FPGA内缺陷成团机理与可靠性的策略分析

FPGA内缺陷成团机理与可靠性的策略分析

评论