1 引言

互补金属氧化物半导体(CMOS)图像传感器具有功耗低,集成度高和易于控制等特点,其信噪比,光灵敏度和动态范围等性能可与成熟的电荷耦合器件(CCD)图像传感器相媲美,因此,CMOS图像传感器为发展微型化、数字化和多功化成像器件开辟了新思路。高分辨率、高帧频的CMOS图像采集系统在高速运动分析、高速物体追踪及高速变化过程罔像的获取等领域应用广泛。

2 高帧频COMS相机电子学系统模块

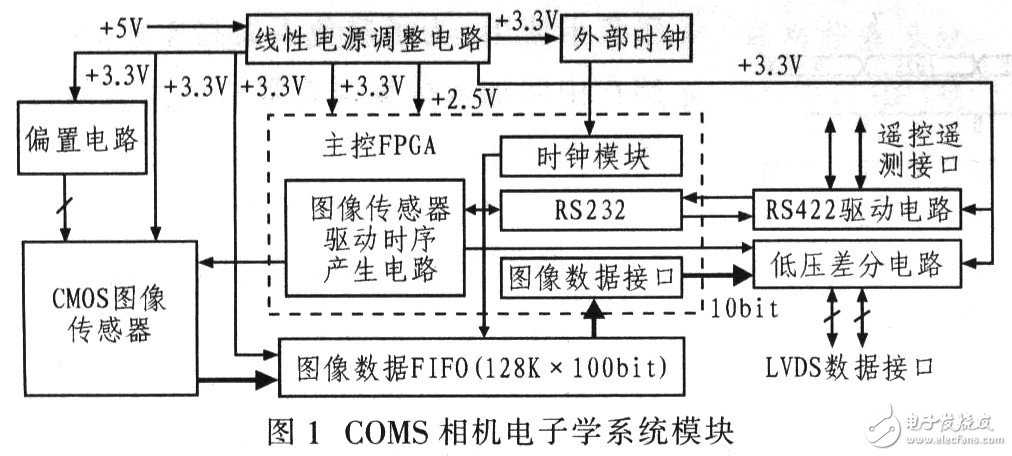

相机电子学系统包括CMOS图像传感器焦平面板和驱动控制板,原理结构如图1所示。主要功能模块包括:CMOS图像传感器、LD0电源调整电路及滤波电路、时序电路、时钟电路、图像数据接口电路、RS422驱动电路,以及低压差分电路等。

2.1 焦平面板

经滤波电路平台输出+5 V二次电源电压,冉经LD0电压调整电路输出+3.3V电压。该电压经滤波后向图像传感器及偏置电路提供电源。

MT9M413内部集成有10 bit A/D转换器(简称ADC),可直接输出3.3 V的数字信号。时序驱动板CPLD的端口电压为+3.3 V,因此两者之间可直接传输信号,无需电平转换电路。MT9M413含有10个输出通道,数据总线多达100条,因此采用微型板问连接器连接焦平面板和驱动控制板,以减小电路板体积和质量。

2.2 驱动控制板

驱动控制板是相机控制系统的核心,其作用主要包括:产生MT9M413的丁作时序;FIF0读写控制;实现间接指令接口RS232(RS422电平);实现图像输出接口(LVDS电平)。驱动控制板的时序信号和控制信号通过FPGA实现,综合考虑速度、器件容量、工作温度、功耗及抗辐射能力等因素,选用Actel公司的APA600型FPGA,该器件内置2个锁相环,I/O电压为+3.3V,内核电压为+2.5 V,属于低功耗器件。

2.2.1 MT9M413图像传感器工作原理

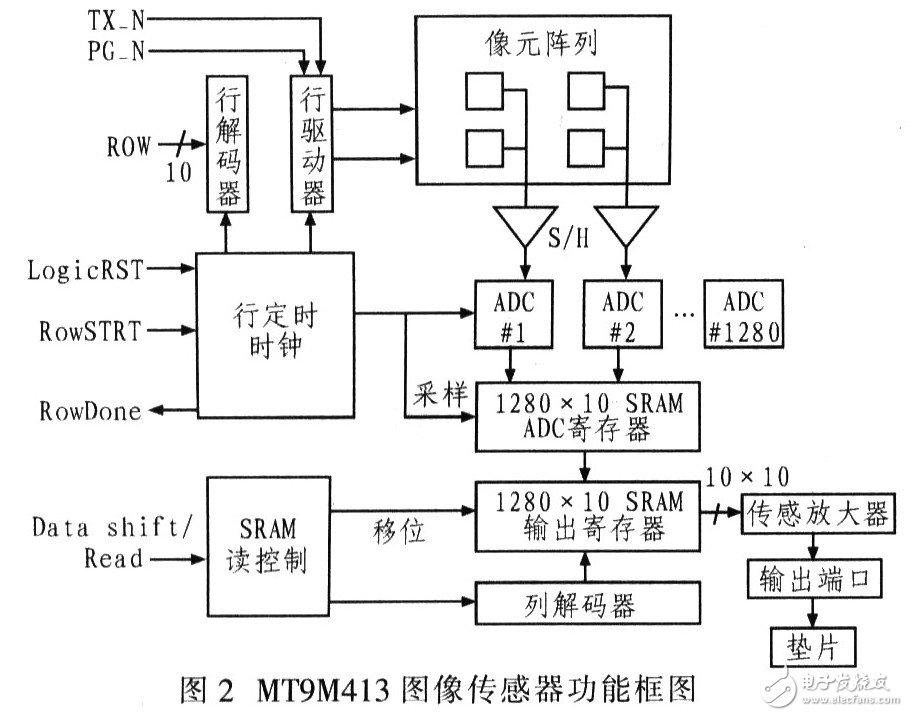

MT9M413是Micron公司的具有3.3V电源,1.31 M像素的CMOS数字图像传感器,其分辨率为l 280 H×1 024 V;主时钟为66 MHz时,帧频可达500f/s;动态范围为59 dB;快门时间范围为10μs~33 ms。片内集成10 bit自标定、全数字接口的ADC。MT9M413功能框图如图2所示,其功能组件包括:像元阵列、行地址选择逻辑、列放大器组、l 280个10位ADC模块、ADC寄存器和读出寄存器模块。

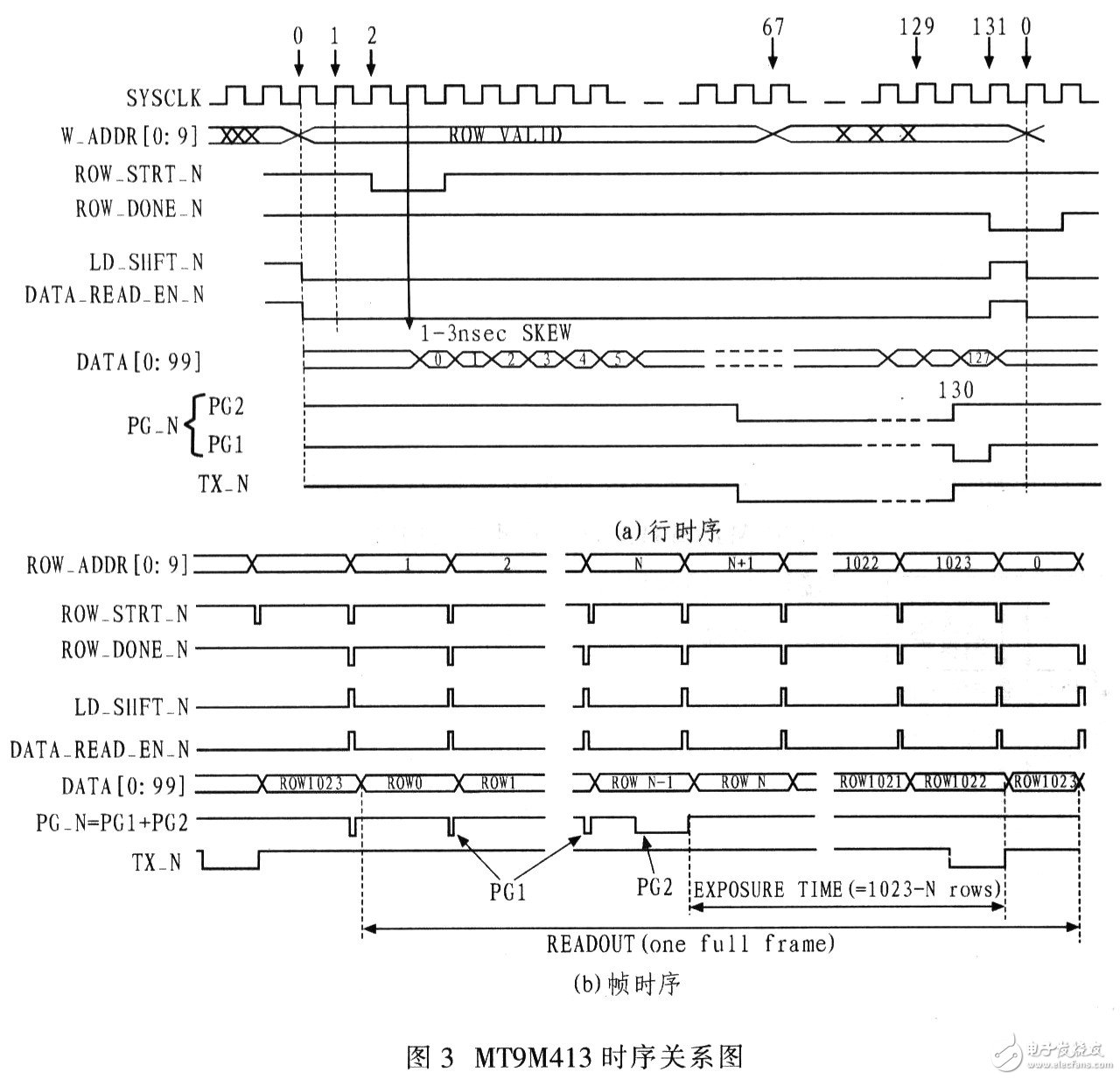

MT9M413的时序关系如图3所示。10位ROW—ADDR行地址总线输入选择读出的像素行,ROW_STRT_N信号开始从像素行读模拟数据,并数字化地存储在ADC寄存器中,当这一系列工作完成后,器件输出ROW_DONE_N信号。当DATA_READ_EN_N信号有效时,LD_SHFT_N信号低电平有效,从ADC寄存器开始向输出寄存器转移数字数据,DATA_READ_EN_N信号使输出寄存器使能。DATA_READ_EN_N置低保持两个时钟后。开始读取新像素行和转换循环。在新行转换同时允许读取先前转换的数字信号,因此行周期是从ROW_STRT_N信号开始到。ROW_DONE_N信号返回,或在LD_SHFT_N和DATA_READ_EN_N信号有效周期加两个时钟的时间。PG_N(PGl+PG2)信号同时置位整个像素阵列的光探测器进行光积分;TX—N信号同时为整个阵列的每一个像素转移光探测器的电荷到存储器,结束光积分。必须注意的是,在连续模式下,PG—N和rrx—N脉冲必须持续64个SYSTCLK时钟周期;在ROW—STRT_N为低电平时,ROW—ADDR地址总线才有效,且至少持续66个SYSCI.K时钟周期。通过增加光积分阶段的行转移脉冲个数调整曝光时间。对MxN阵列的CMOS器件.Ⅳ个行转移周期即可完成一帧图像的所有行转移。为了增大积分时间,可以增加行转移的数量,使得行转移脉冲个数大于Ⅳ,当然在第Ⅳ个转移周期之外的信号无效。

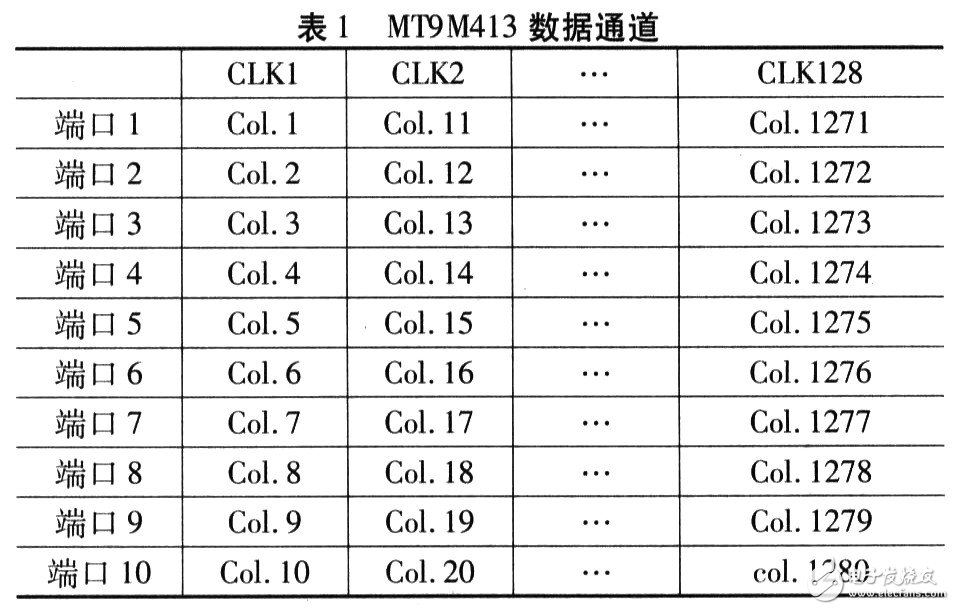

图像信号从10个通道同步读m,每个通道的位宽均为10 bit.每个通道所对应的像元编号如表1所示。

整帧图像输出需要128个时钟周期。随后将1。5通道合并成一路50 bit数据:6~10通道合并成一路50 bit数据,分别缓存在两个数据FIF0中.每个FIFO的容量为128 KxS0bit.并将上述两路信号传输给FPGA进行并.并转换,最后输m一路10 bit并行图像数据。

2.2.2 FIFO读写控制

由于M’F9M413每个时钟周期可同时输出100位数据,必须经过FPGA并。并转换。转换成10位数据供LV:DS数据采集卡使用。为了避免丢失高速数据,必须在中间加入数据缓存器。该系统设计选用两片128 KxS0 bit的FIFO。它是一种高速、低功耗的先入先出型缓存器。

2.2.3 基于VHDL硬件电路的实现

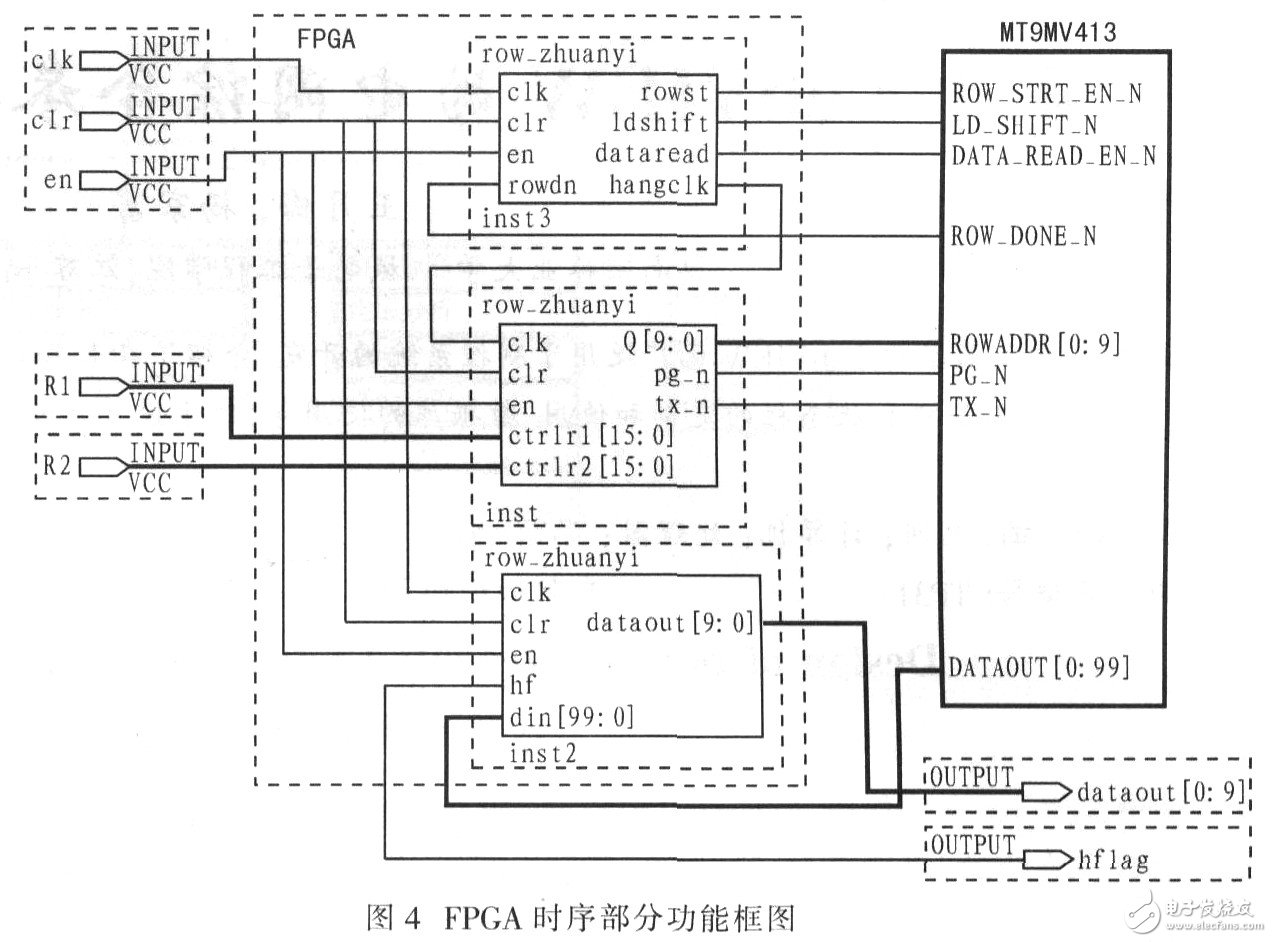

VHDL硬件描述语言支持自上而下的设计方法。根据自上而下的设计方法,确定输入/输出信号,同时根据时序划分功能模块,然后把所有的输入/输出信号分配到各个功能模块中,每个功能模块分别进行VHDL设计输入、功能仿真、后仿真。在各个功能模块实现各自功能后,例化到顶层设计中,完成顶层的VHDL设计输入、功能仿真、综合、后仿真。直至达到设计要求。部分VHDL硬件捕述如图4所示,其中R1是帧计数,R2是行计数。总曝光时间的计算公式如下:总曝光时间=Rl×行周期×l 024+(1 023一R2)×行周期。

3 结语

该系统没计根据CMOS的时序要求.经仿真调试能够产生相应的驱动脉冲和偏置电压,并通过遥控数据的注入,实现了曝光时间的可调控制。

-

芯片

+关注

关注

449文章

48563浏览量

413044 -

图像传感器

+关注

关注

68文章

1786浏览量

129001 -

vhdl

+关注

关注

30文章

816浏览量

127810

发布评论请先 登录

相关推荐

VHDL语言实现数字电压表

如何利用FPGA和VHDL语言实现PCM码的解调?

MT9M413高帧频CMOS图像传感器原理

用VHDL语言实现3分频电路

用VHDL语言实现3分频电路(占空比为2比1)

使用Quartus和VHDL语言实现的LPC时序的工程文件

采用MT9M413芯片与VHDL语言实现高帧频COMS相机电子学系统设计

采用MT9M413芯片与VHDL语言实现高帧频COMS相机电子学系统设计

评论