引 言

随着电子技术、计算机技术和EDA技术的不断发展,利用FPGA/CPLD进行数字系统的开发已被广泛应用于通信、航天、医疗电子、工业控制等领域。与传统电路设计方法相比,FPGA/CPLD具有功能强大,开发周期短,投资少,便于追踪市场变化及时修改产品设计,以及开发工具智能化等特点。近年来,FPGA/CPLD发展迅速,随着集成电路制造工艺的不断进步,高性价比的FPGA/CPLD器件推陈出新,使FPGA/CPLD成为当今硬件设计的重要途径。在FPGA/CPLD的应用设计开发中,VHDL语言作为一种主流的硬件描述语言,具有很强的电路描述和建模能力,能从多个层次对数字系统进行建模和描述,从而大大简化了硬件设计任务,提高了设计效率和可靠性,并在语言易读性和层次化、结构化设计方面。表现出了强大的生命力和应用潜力。

QuartusⅡ是Altera公司在21世纪初推出的FPGA/CPLD集成开发环境,是Altera公司前一代FPGA/CPLD集成开发环境Max+PlusⅡ的更新换代产品,其界面友好,使用便捷,功能强大,为设计者提供了一种与结构无关的设计环境,使设计者能方便地进行设计输入、快速处理和器件编程。

计数器是数字系统中使用最多的时序电路之一,不仅能用于对时钟脉冲计数,还可以用于分频、定时、产生节拍脉冲和脉冲序列以及进行数字运算等。可变模计数器由于计数容量可以根据需要进行变化,为其广泛使用创造了便利。这里在QuartusⅡ开发环境下,用VHDL语言设计了一种具有清零、置数、使能控制、可逆计数和可变模功能的计数器。

1 基本可变模计数器设计

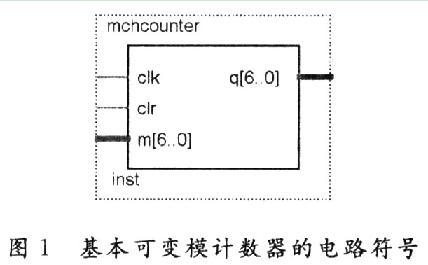

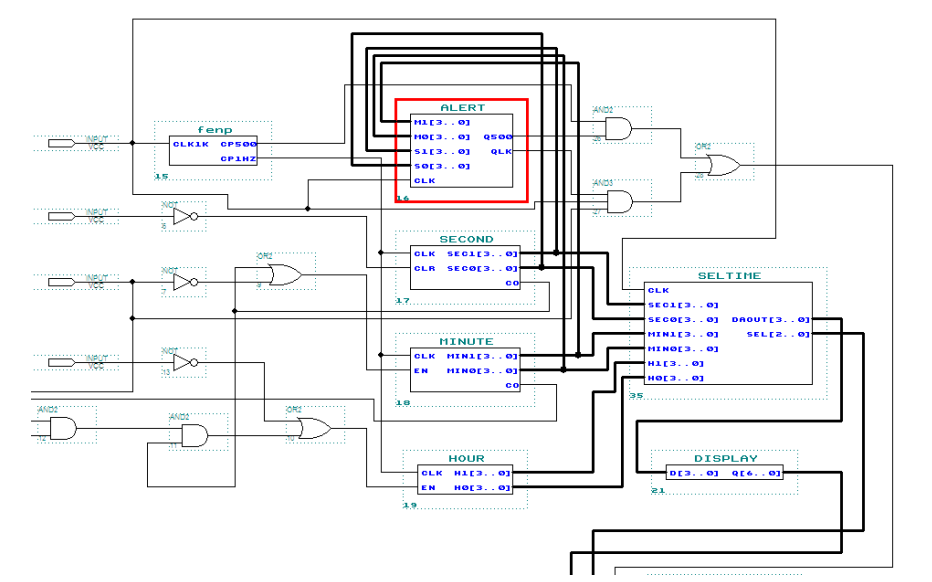

可变模计数器是指计数/模值可根据需要进行变化的计数器。电路符号图1所示,clk为时钟脉冲输入端,clr为清零端,m为模值输入端,q为计数输出端。

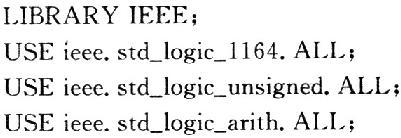

基本可变模计数器的VHDL代码如下所示:

说明:上述代码设计采用了常用的if语句结构,即“if条件句then顺序语句elsif条件句then顺序语句else顺序语句end if”结构,实现模值小于99的可变模计数。

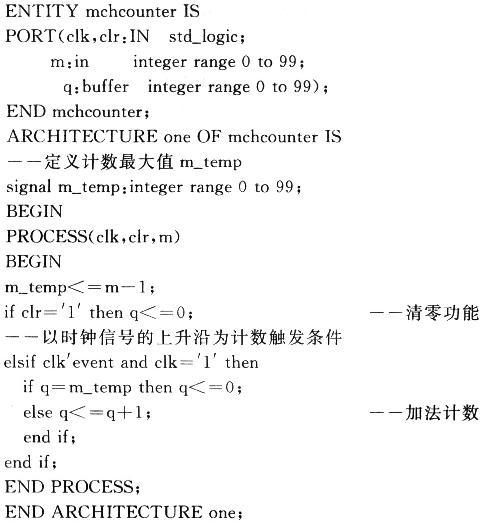

从上述的代码可以看出,基本的可变模计数器的功能单一。仿真验证则表明在进行模值变换时,基本的可变模计数器存在一些功能上的缺陷:计数器若是由较小的模值变化为较大的模值时,能正常的进行变模计数;但当其由较大的模值变化为较小的模值,则可能出现计数失控,如图2所示,图中显示了当模值由12变换为7时,即发生了计数失控。失控的原因是大于当模值由12变换为7时,计数输出为q为11,大于当前模值7的计数最大值6,由此产生了计数失控。

2 改进的多功能可变模计数器

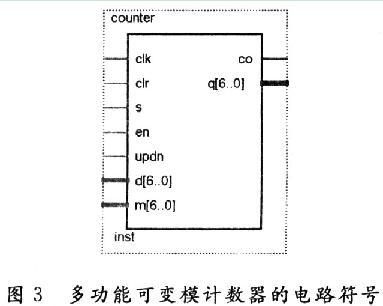

为了克服上述基本可变模计数器的缺陷,并增加更多的控制功能,在此设计了一种改进的多功能可变模计数器,具有清零、置数、使能控制、可逆计数和可变模功能。其电路符号如图3所示,clk为时钟脉冲输入端,m为模值输入端,clr为清零控制端,s为置数控制端,d为置数输入端,en为使能控制端,updn为计数方向控制端,q为计数输出端,co为进位输出端。

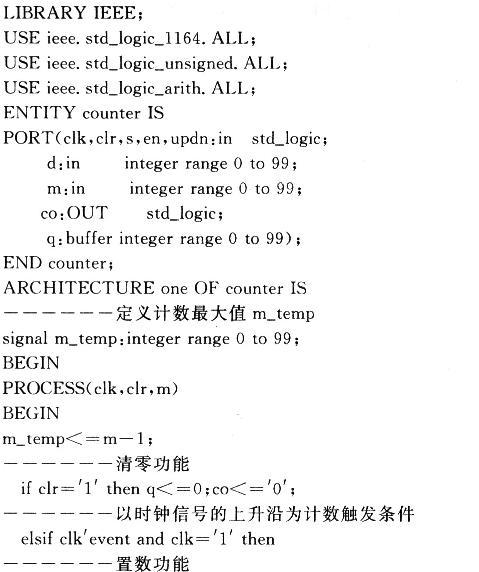

这里所设计的多功能可变模计数器的VHDL代码如下所示:

LIBRARY IEEE;

值得注意的是,这里所设计的多功能可变模计数器具有如下特点:

(1)该设计的多功能可变模计数器具有多个功能控制端。因此各个控制端的优先权顺序就成为设计的关键,经过理论分析和仿真调试,最终确认的优先权顺序为:clr(清零)→clk(时钟触发)→s(置数)→en(使能)→updn(计数方向)。这个优先权顺序可以有效地保证各个功能的完整实现,以及技术器的稳定运行。

(2)为了防止出现计数失控,大多数计数器采用给计数器增加一个复位控制端的办法,当发现计数输出q发生了计数失控时,通过复位控制端将计数器复位来排除计数失控。这种方法虽然有效,但是每次出现计数失控都要手动控制复位,给实际使用带来了不便。该设计的多功能可变模计数器中,将当前的计数输出q与当前的计数最大值m_temp进行比较,如果q比m_temp大,则强制将m_temp赋给q,这样就可以自动避免计数失控,不必再增加手动的复位控制端。

3 仿真结果分析

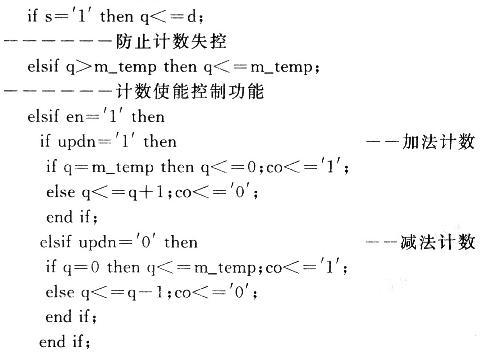

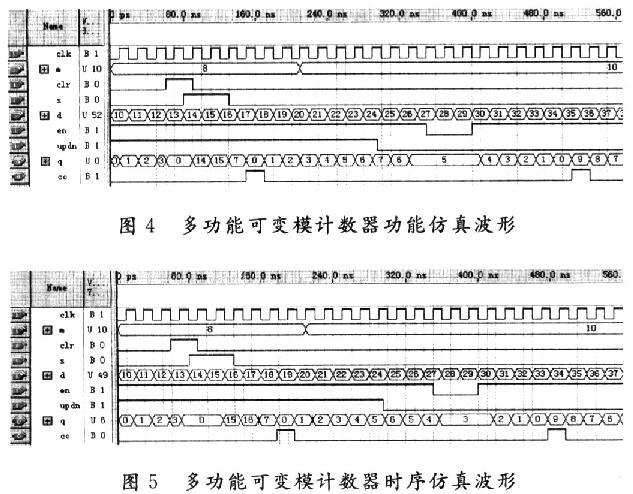

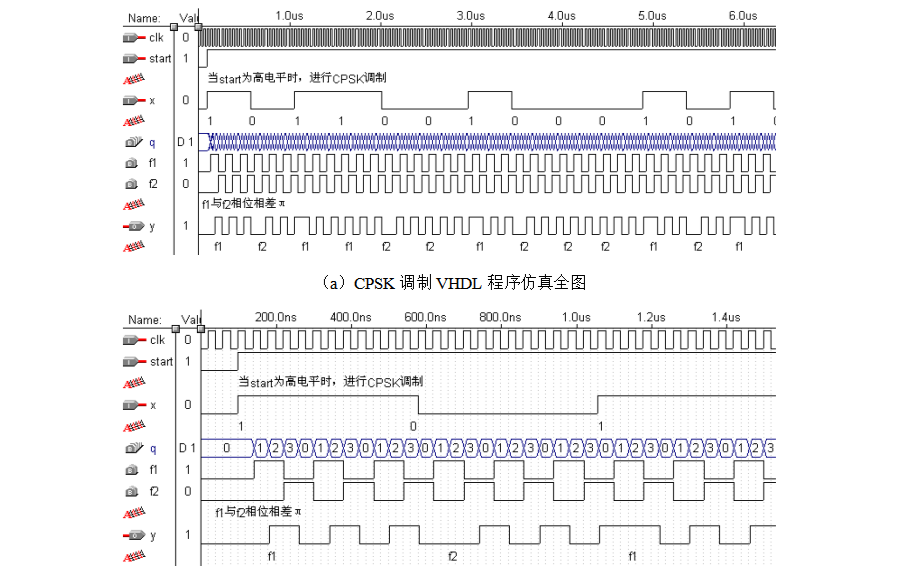

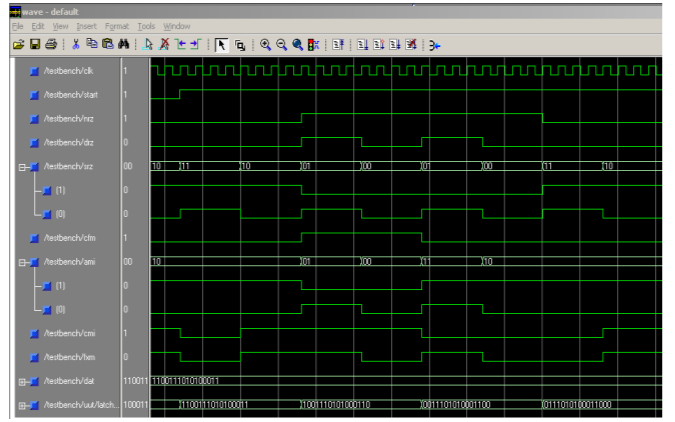

该多功能可变模计数器在QuartusⅡ开发环境下进行了仿真验证,功能仿真波形如图4所示,时序仿真波形如图5所示。

仿真结果分析如下:

(1)clk为时钟信号,由时钟信号的上升沿触发计数;

(2)m为模值输入端,当其变化时,计数容量相应发生变化;

(3)clr为清零控制端,当其为高电平时清零;

(4)s为置数控制端,当其为高电平时将置数输入端d的数据加载到输出端q;

(5)en为使能控制端,当其为高电平时正常计数,当其为低电平时暂停计数;

(6)updn为计数方向控制端,当其为高电平时计数器加法计数,当其为低电平时计数器减法计数。

4 结 语

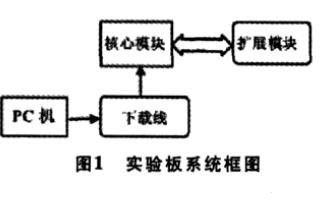

这里所设计的多功能可变模计数器在QuartusⅡ开发环境下进行了仿真验证后,下载到湖北众友科技实业股份有限公司的ZY11EDA13BE实验箱中进行了硬件验证。该实验箱使用ACEX1K系列EP1K30QC208芯片作为核心芯片.实验证明设计正确,功能完整,运行稳定。另外,该设计的多功能可变模计数器可根据需要将模值的最大值由99进一步扩展,获得更高的计数模值。

-

FPGA

+关注

关注

1630文章

21759浏览量

604369 -

cpld

+关注

关注

32文章

1248浏览量

169440 -

vhdl

+关注

关注

30文章

817浏览量

128176

发布评论请先 登录

相关推荐

在QuartusⅡ开发环境下怎么用VHDL语言设计可变模功能的计数器?

基于Multisim的计数器设计仿真

基于Proteus的任意进制计数器设计与仿真

采用VHDL预言实现基于Petri网的并行控制器设计并进行仿真验证

如何使用FPGA进行多功能实验板的设计与实现

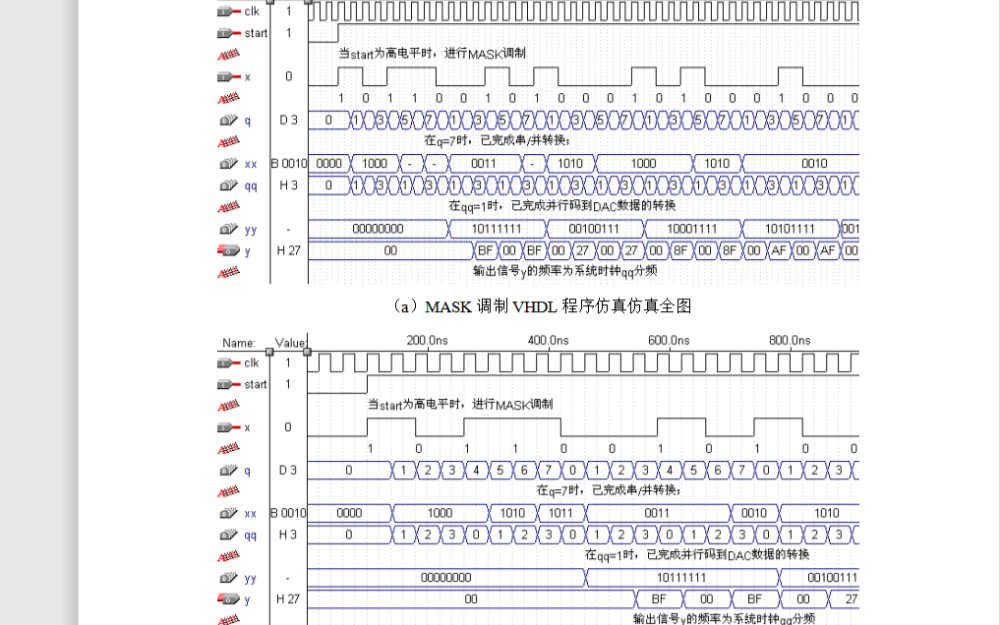

使用VHDL硬件描述语言实现基带信号的MASK调制的程序与仿真

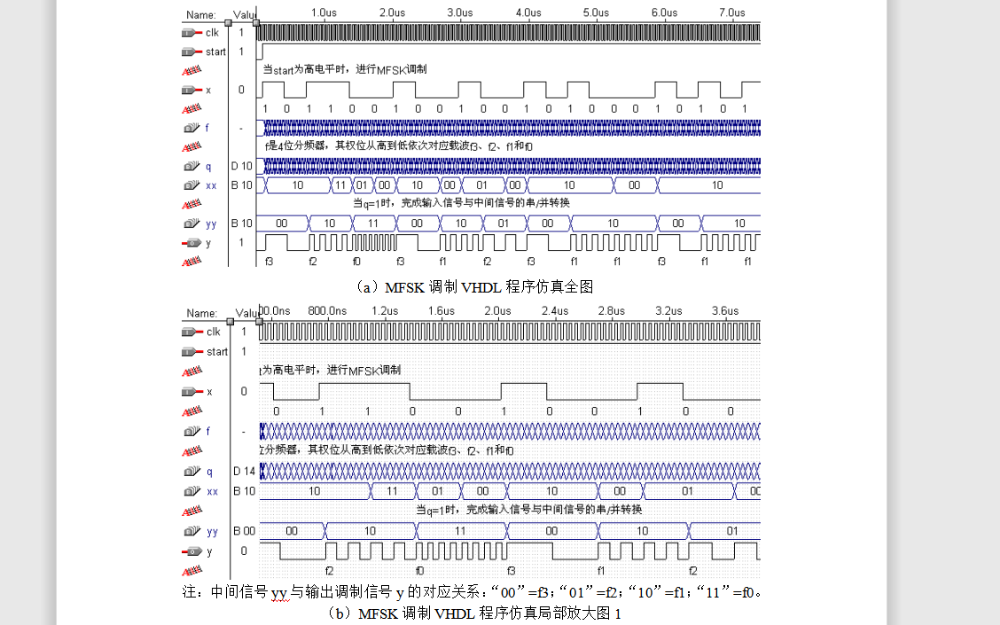

使用VHDL硬件描述语言实现基带信号的MFSK调制的程序与仿真

采用VHDL语言实现多功能可变模计数器设计并进行仿真验证

采用VHDL语言实现多功能可变模计数器设计并进行仿真验证

评论